|

|

|

Overview

|

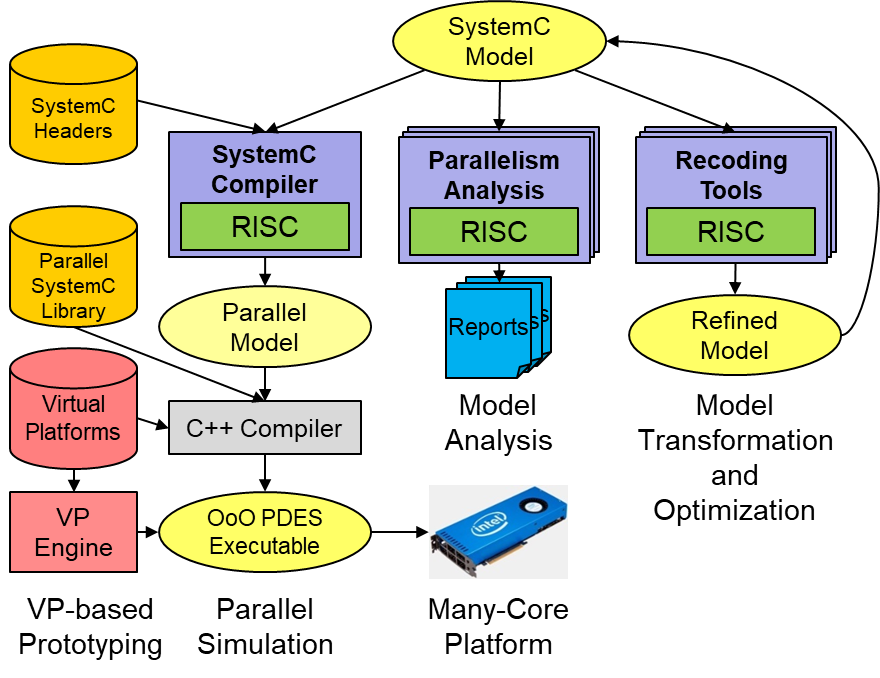

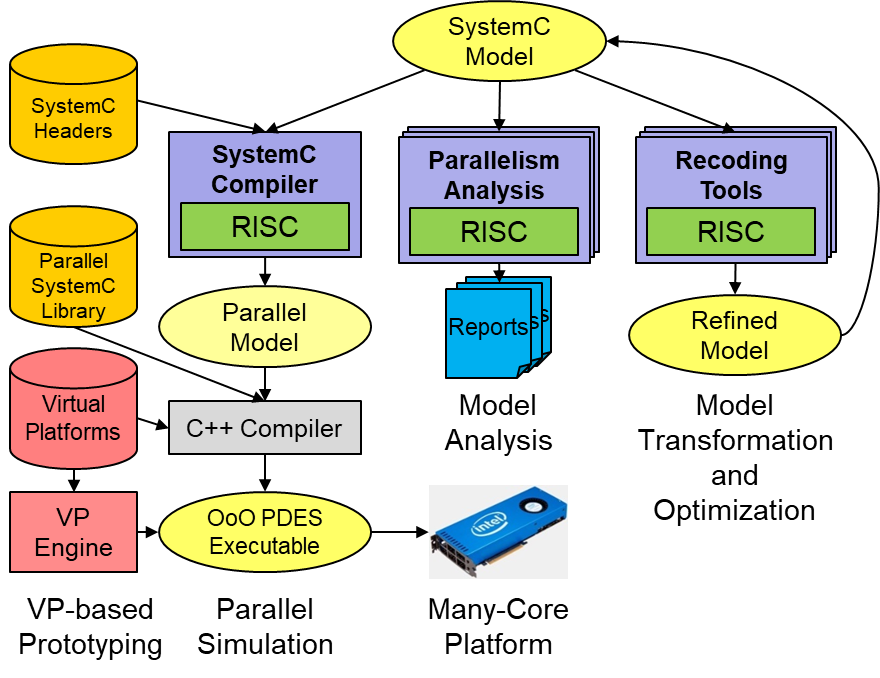

The Recoding Infrastructure for SystemC (RISC) project

addresses the advanced analysis and agressive parallel simulation

of embedded system models with hardware and software components.

We focus on Transaction Level Models (TLM 1.0 and TLM-2.0)

described in the SystemC language

and aim for maximum compliance with the IEEE standard 1666.

As simulation host platform, the project targets modern multi- and many-core computer architectures,

including the Intel® Many Integrated Core (MIC) architecture,

such as the Xeon® Phi™ Coprocessor.

A central goal of the project is the efficient analysis and validation of IEEE SystemC design models

through high-performance simulation with maximum parallelism

for fast and accurate performance analysis and rapid design space exploration.

This project encompasses the detailed study, research and development of

- analysis, visualization and transformation tools for high-level SystemC models,

- advanced out-of-order parallel simulation algorithms for the SystemC language, and

- efficient mapping of parallel threads onto symmetric many-core platforms.

At the center of the project is the research and development

of analysis, visualization and transformation tools for IEEE SystemC models,

including

- advanced static and dynamic analyzers of SystemC models,

- a dedicated SystemC compiler for aggressive yet standard-compliant parallel simulation,

- a parallel simulator with out-of-order execution on many-core platforms,

- visualization tools for hierarchical connectivity and potential parallelism, and

- recoding tools for source-to-source transformation of legacy SystemC models.

Acknowledgments:

Substantial funding for this project has been provided by Intel Corporation

through initial seed funding,

the project "Out-of-Order Parallel Simulation of SystemC Virtual Platforms on Many-Core Architectures",

and the project "Scaling the Recoding Infrastructure for Parallel SystemC Simulation".

The PI and project members are very thankful for this support.

Disclaimer:

This is an ongoing project.

The RISC software and other materials provided here are a work in progress and subject to change.

Source code and documentation are provided as-is, without any guarantees.

Use RISC at your own risk!

|

|

Open Source Releases

|

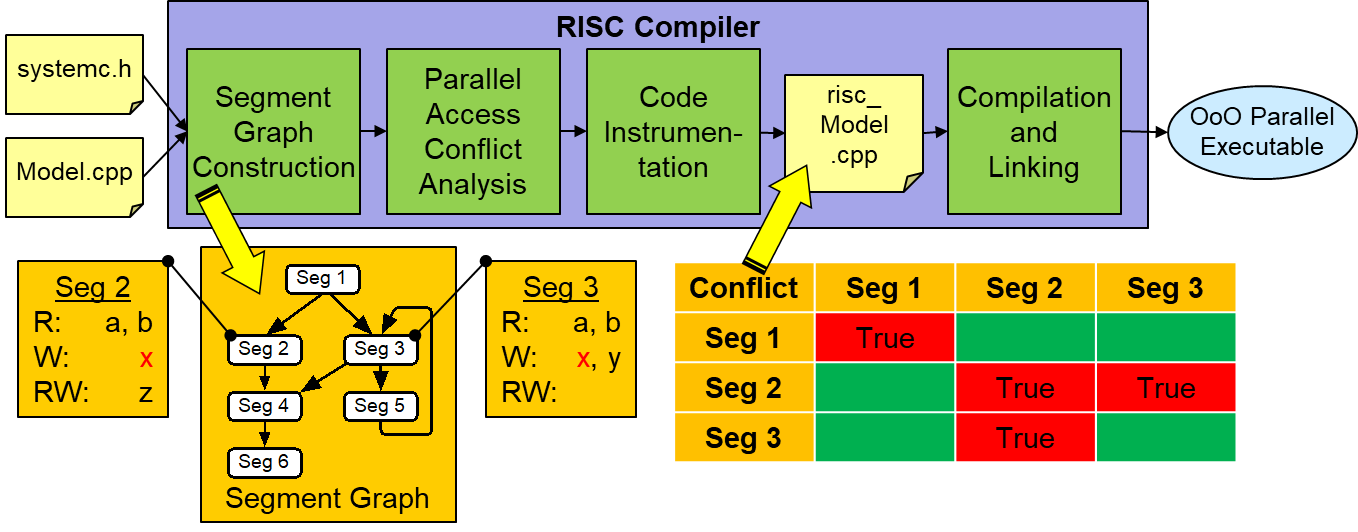

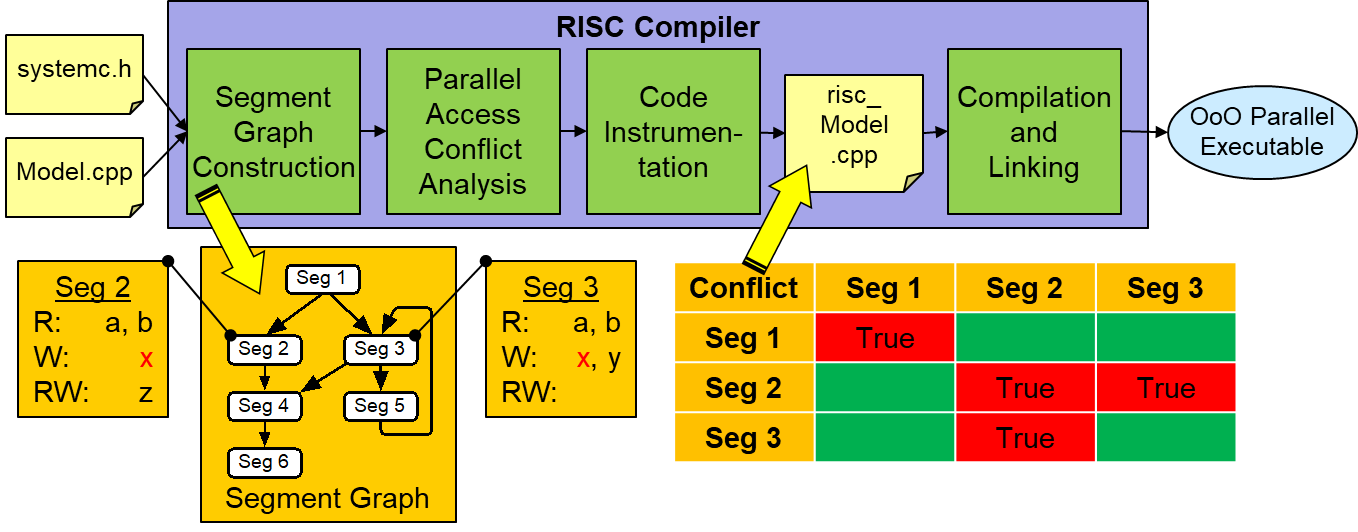

The Recoding Infrastructure for SystemC (RISC) is

an open-source framework for static and dynamic analysis

and source-to-source transformations of IEEE SystemC models.

RISC is built on top of

Accellera SystemC

and the Rose compiler.

RISC provides a dedicated SystemC compiler and out-of-order parallel simulator,

as well as model visualization and performance tuning tools.

In addition, the RISC data structures offer programming access

to the Internal Representation (IR) and Segment Graph (SG) of SystemC models

via documented APIs.

The RISC software and documentation are freely available below:

RISC API, Alpha Release V0.1.0: (2014-06-04)

RISC Compiler and Simulator, Alpha Release V0.2.0: (2015-09-30)

RISC Compiler and Simulator, Alpha Release V0.2.1: (2015-10-30)

RISC Compiler and Simulator, Beta Release V0.3.0: (2016-09-30)

RISC Compiler and Simulator, Release V0.4.0: (2017-07-31)

RISC Compiler and Simulator, Release V0.4.2: (2018-06-15)

RISC Compiler and Simulator, Release V0.5.0: (2018-09-30)

RISC Compiler and Simulator, Release V0.6.0: (2019-09-30)

RISC Compiler and Simulator, Release V0.6.2: (2020-09-13)

RISC Compiler and Simulator, Release V0.6.3: (2021-08-18)

- Installation notes and script: INSTALL,

Makefile

- Open source tar ball: risc_v0.6.3.tar.gz

- Docker script and container: Dockerfile,

RISC v0.6.3 at hub.docker.com

- Doxygen documentation: RISC API,

OOPSC API

- Tool manual pages: risc,

elab,

simd,

list,

tree,

visual,

sysdot,

flatten

- BSD license terms: LICENSE

RISC Change Log:

Authors: (in alphabetical order):

- Farah Arabi

- Emad Arasteh

- Zhongqi Cheng

- Rainer Doemer

- Vivek Govindasamy

- Aditya Harit

- Spencer Kam

- Guantao Liu

- Daniel Mendoza

- Tim Schmidt

- Yutong Wang

Center for Embedded and Cyber-Physical Systems (CECS),

University of California, Irvine

|

|

Project Videos

|

ESWEEK 2020 Tutorial

"Out-of-Order Parallel Simulation of SystemC Models using the RISC Framework"

Rainer Doemer

September 20, 2020

- Presentation handout: ESWeekTutorial.pdf

- Part 1: "Introduction to Out-of-Order Parallel Discrete Event Simulation",

Video

- Part 2: "Overcoming the Obstacles of IEEE SystemC Semantics",

Video

- Part 3: "RISC: Recoding Infrastructure for SystemC",

Video

- Part 4: "Hands-on Practical Training with RISC Compiler and Simulator",

Video

- Part 5: "Hands-on Practical Analysis of Parallel Potential of SystemC Models",

Video

- Practical training, hands-on demo "cheat sheet": ESWeekTutorial.txt

|

|

Project Publications

|

|

|

|

|

|

|

|

|

|

|

-

Z. Cheng, T. Schmidt, R. Dömer:

"SystemC Coding Guideline for Faster Out-of-Order

Parallel Discrete Event Simulation", chapter 6 in

"Languages, Design Methods, and Tools for Electronic System Design"

by T. Kazmierski, S. Steinhorst and D. Grosse,

reprint of best papers at FDL 2018,

Springer Nature, Switzerland, January 2020.

(ISBN 978-3-030-31585-6)

|

|

|

|

|

|

|

|

|

|

-

R. Dömer, Z. Cheng, D. Mendoza, A. Dingankar:

"RISC: Recoding Infrastructure for SystemC,

Open Source Framework for Parallel Simulation",

Workshop on Open Source EDA Technology at ICCAD,

San Diego, California, November 2018.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|