Contact Information

Hardware accelerators, programming languages and compilers for accelerators

sitaoh [AT] uci [DOT] edu

https://sitaohuang.com/

Professor Huang’s Research

Sitao Huang received his Ph.D. in electrical and computer engineering from University of Illinois at Urbana-Champaign in 2021. He received his B.Eng. degree in electronics engineering at Tsinghua University in 2014, and his M.S. degree in electrical and computer engineering at the University of Illinois at Urbana-Champaign in 2017. His research interests include highly efficient hardware acceleration, programming language and synthesis flow for hardware systems and optimization of heterogenous systems. He is a recipient of 2019 Sundaram Seshu International Student Fellowship and 2018 Rambus Computer Engineering Fellowship. His research has won several awards, including the Best Paper Nomination at ASP-DAC 2021, the Student Innovation Award at the 2018 IEEE HPEC Graph Challenge, and the first place at DAC 2019 System Design Contest.

Research Interests

Hardware accelerators, programming languages and compilers for accelerators, high-level synthesis, heterogeneous computing

Selected Research Projects

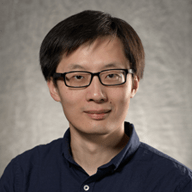

PyLog: A High-Level Programming and Synthesis Flow for FPGAs

PyLog is a high-level, Python-based algorithm-centric programming and synthesis flow for FPGA. PyLog features a set of compiler optimization passes and a type inference system to generate high-quality design.

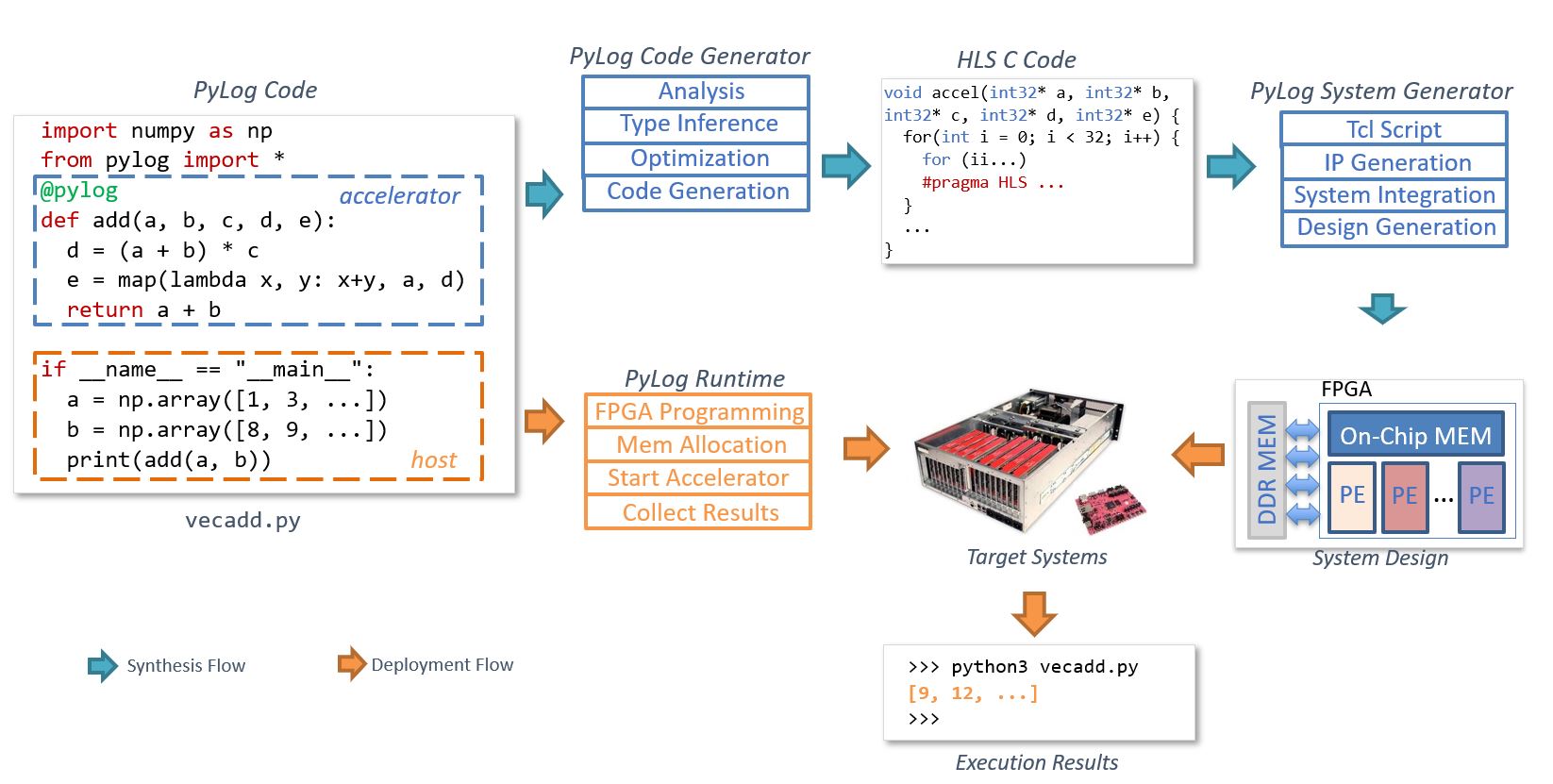

Mixed Precision Quantization for ReRAM-based DNN Inference Accelerators

(ASP-DAC 2021 Best Paper Candidate)

We propose a mixed precision quantization scheme for ReRAM-based DNN inference accelerators where weight quantization, input quantization, and partial sum quantization (ADC quantization) are jointly applied for each DNN layer. We also propose an automated quantization flow powered by deep reinforcement learning to search for the best quantization configuration in the large design space.

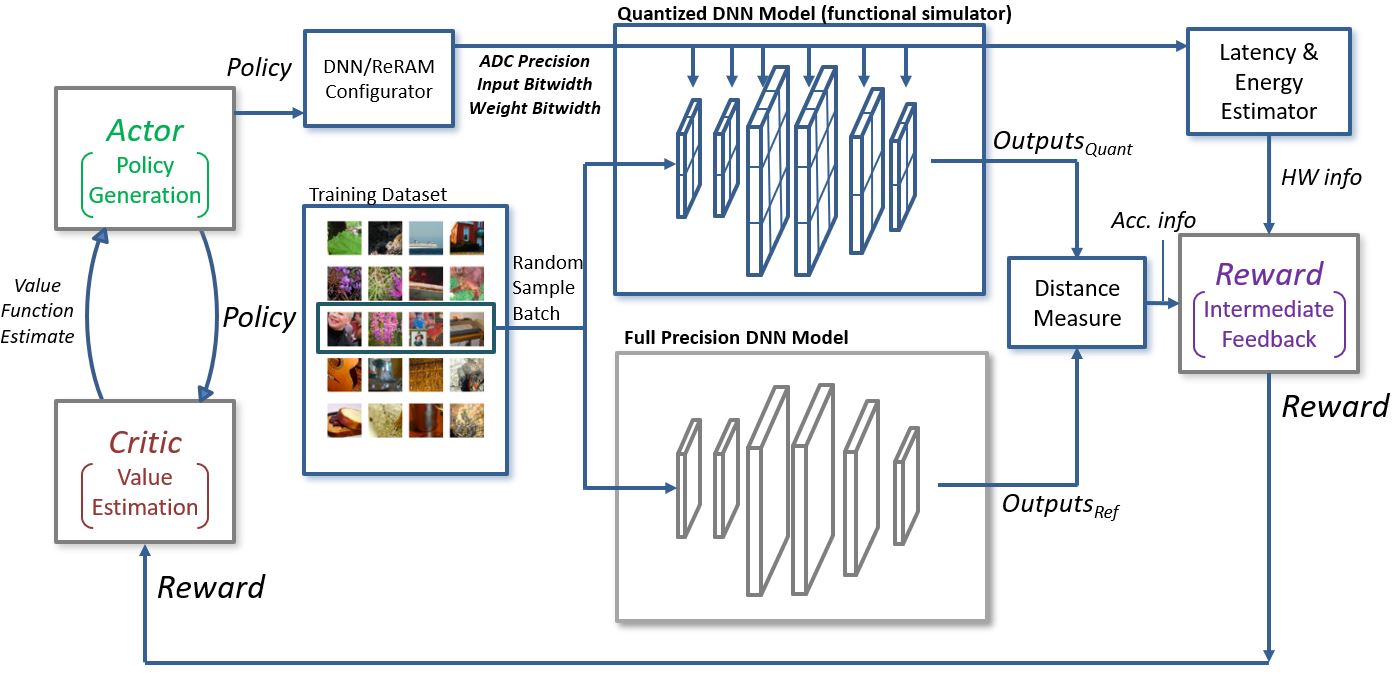

Chai-FPGA: Collaborative Execution Strategies for Heterogeneous CPU-FPGA Architectures

We propose the collaborative schemes for CPU-FPGA systems, including data partitioning, coarse-grained task partitioning, and fine-grained task partitioning. We explore and evaluate the potential of collaborative execution between CPUs and FPGAs using OpenCL high level synthesis. We observe that choosing the most suitable partitioning strategy can improve performance by up to 2x.

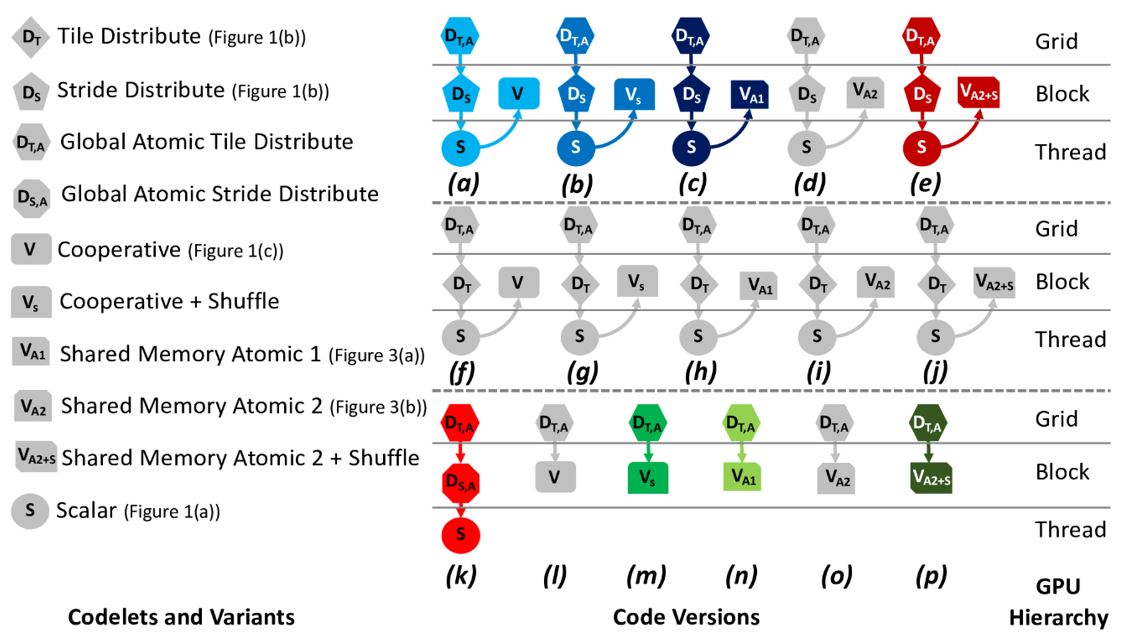

Tangram: A High-Level Language for Efficient Performance-Portable Kernel Synthesis

Tangram is a general-purpose high-level language that achieves high performance across architectures, including GPUs and multi-core CPUs. In Tangram, a program is written by synthesizing elemental pieces of code snippets, called codelets. A codelet can have multiple semantic-preserving implementations to enable automated algorithm and implementation selection. An implementation of a codelet can be written with tunable knobs to allow architecture-specific parameterization. The Tangram compiler produces highly optimized code by choosing and composing architecture-friendly codelets, and then tuning the knobs for the target architecture.