#include <design.h>

Classes | |

| class | label_writer |

| class | SegEdge |

| class | SegNode |

Public Types | |

| typedef boost::adjacency_list < boost::vecS, boost::vecS, boost::directedS, SegNode, SegEdge > | graph_t |

| typedef boost::adjacency_list::vertex_descriptor | VertexDescriptor |

Public Member Functions | |

| Design (int argc, char *argv[], std::vector< std::string > psg_file_names=std::vector< std::string >(0), bool is_psg_mode=false, bool PrintFrontendArgs=false) | |

| default constructor More... | |

| ~Design () | |

| void | initialize_port_mapping () |

| void | initialize_interfaces () |

| void | initialize_definitions () |

| void | initialize_top_modules () |

| void | initialize_global_functions () |

| void | initialize_global_variables () |

| void | initialize_path_instance_mapper () |

| void | print_all_class_definitions () |

| void | print_all_global_functions () |

| void | print_design () |

| InstanceTree | get_root () |

| Module * | find_module_definition (SgClassDefinition *cd) |

| PrimitiveChannel * | find_prim_channel_definition (SgClassDefinition *cd) |

| HierarchicalChannel * | find_channel_definition (SgClassDefinition *cd) |

| Interface * | find_interface (SgClassDefinition *cd) |

| Variable * | find_global_variable (SgVariableDefinition *var_def) |

| Find a port by it's ast variable definition. More... | |

| void | reset_instance_counter () |

| This function resets the instance counter of the module and hierarchical channel instances to zero. More... | |

| bool | perform_static_analysis () |

| The functions return if a static analysis will be performed. More... | |

| void | add_module_to_definition_list (SgClassDefinition *class_def) |

| Only for internal use! This function triggers the analysis of a module. The new analyzed module will be put into the module_definitions_ container. More... | |

| void | add_hierarchical_channel_to_defintion_list (SgClassDefinition *class_def) |

| Only for internal use! This function triggers the analysis of a module. The new analyzed module will be put into the hierarchical_channel_ container. More... | |

| std::string | get_design_file_name () |

| This function returns the input file name of the design. More... | |

| void | store_port_mapping (std::string) |

| This function stores the port mapping information to .psg file. More... | |

| void | load_port_mapping (std::string) |

| This function loads the port mapping information from .psg file. More... | |

| Socket * | find_socket (SgVariableDefinition *) |

| This function finds the socket according to its underlying symbol. More... | |

| ModuleInstance * | find_module_instance (SgVariableDefinition *) |

| This function finds the socket according to its underlying symbol. More... | |

| bool | is_analyzable () |

| void | draw_port_mapping () |

Private Member Functions | |

| Design (const Design &d) | |

| Disabled copy constructor. More... | |

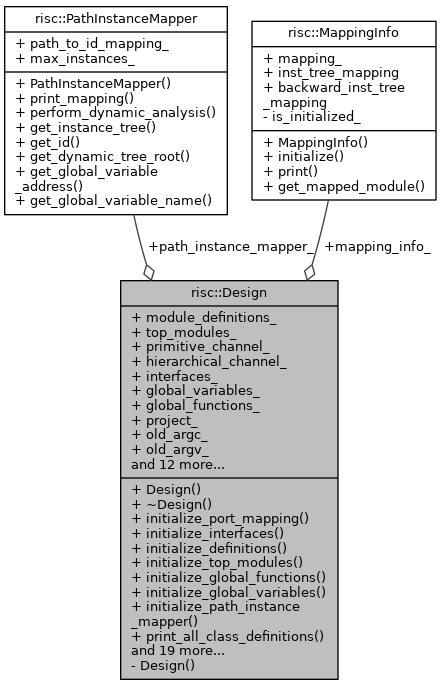

This class represents the internal representation. The IR offers different interfaces to start search in IR.

| typedef boost::adjacency_list<boost::vecS, boost::vecS, boost::directedS, SegNode, SegEdge> risc::Design::graph_t |

| typedef boost::adjacency_list ::vertex_descriptor risc::Design::VertexDescriptor |

|

explicit |

default constructor

| argc | expects argc from main function |

| argv | expects argv from main function |

| psg_file_names | names of psg files |

| is_psg_mode | risc run as psg constructor |

| PrintFrontendArgs | default false |

| risc::Design::~Design | ( | ) |

|

private |

Disabled copy constructor.

| risc::Design::add_hierarchical_channel_to_defintion_list | ( | SgClassDefinition * | class_def | ) |

Only for internal use! This function triggers the analysis of a module. The new analyzed module will be put into the hierarchical_channel_ container.

| risc::Design::add_module_to_definition_list | ( | SgClassDefinition * | class_def | ) |

Only for internal use! This function triggers the analysis of a module. The new analyzed module will be put into the module_definitions_ container.

| void risc::Design::draw_port_mapping | ( | ) |

| risc::HierarchicalChannel * risc::Design::find_channel_definition | ( | SgClassDefinition * | cd | ) |

| risc::Variable * risc::Design::find_global_variable | ( | SgVariableDefinition * | var_def | ) |

Find a port by it's ast variable definition.

| risc::Interface * risc::Design::find_interface | ( | SgClassDefinition * | cd | ) |

| risc::Module * risc::Design::find_module_definition | ( | SgClassDefinition * | cd | ) |

| risc::Design::find_module_instance | ( | SgVariableDefinition * | vd | ) |

This function finds the socket according to its underlying symbol.

| risc::PrimitiveChannel * risc::Design::find_prim_channel_definition | ( | SgClassDefinition * | cd | ) |

| risc::Design::find_socket | ( | SgVariableDefinition * | vd | ) |

This function finds the socket according to its underlying symbol.

| risc::Design::get_design_file_name | ( | ) |

This function returns the input file name of the design.

| risc::InstanceTree risc::Design::get_root | ( | ) |

| void risc::Design::initialize_definitions | ( | ) |

| void risc::Design::initialize_global_functions | ( | ) |

| void risc::Design::initialize_global_variables | ( | ) |

| void risc::Design::initialize_interfaces | ( | ) |

| void risc::Design::initialize_path_instance_mapper | ( | ) |

| void risc::Design::initialize_port_mapping | ( | ) |

| void risc::Design::initialize_top_modules | ( | ) |

| bool risc::Design::is_analyzable | ( | ) |

| risc::Design::load_port_mapping | ( | std::string | filename | ) |

This function loads the port mapping information from .psg file.

| function risc::Design::perform_static_analysis | ( | ) |

The functions return if a static analysis will be performed.

| void risc::Design::print_all_class_definitions | ( | ) |

| void risc::Design::print_all_global_functions | ( | ) |

| void risc::Design::print_design | ( | ) |

| risc::Design::reset_instance_counter | ( | ) |

This function resets the instance counter of the module and hierarchical channel instances to zero.

| risc::Design::store_port_mapping | ( | std::string | filename | ) |

This function stores the port mapping information to .psg file.

| std::string risc::Design::dynamic_analysis_filename_ |

This variable contains the filename of the input file for the dynamic analysis.

| FunctionVector risc::Design::global_functions_ |

| VariableVector risc::Design::global_variables_ |

| HierarchicalChannelVector risc::Design::hierarchical_channel_ |

| std::vector<std::string> risc::Design::input_files_ |

| std::string risc::Design::instrumentor_output_filename_ |

This variable contains the name which will be used for the dir file during the presimulation.

| InterfaceVector risc::Design::interfaces_ |

| ModuleInstanceVector risc::Design::loaded_module_instances |

| risc::Design::loaded_threads |

functions that are implemented in the psg but are not simulation processes

| MappingInfo risc::Design::mapping_info_ |

| ModuleVector risc::Design::module_definitions_ |

| bool risc::Design::no_immediate_notify |

| int risc::Design::old_argc_ |

| char** risc::Design::old_argv_ |

| PathInstanceMapper* risc::Design::path_instance_mapper_ |

| graph_t risc::Design::port_mapping_graph |

| PrimitiveChannelVector risc::Design::primitive_channel_ |

| SgProject* risc::Design::project_ |

| int risc::Design::psg_count |

| std::vector<std::string> risc::Design::psg_file_names_ |

| bool risc::Design::psg_mode |

| std::vector<int> risc::Design::psg_seg_count |

| std::vector<Thread*> risc::Design::simulation_threads |

| InstanceVector risc::Design::top_modules_ |

1.8.5

1.8.5