## **Input Specification**

- Programming language (C/C++, ...)

- Programming semantics requires pre-synthesis optimization

- System description language (SystemC, ...)

- Simulation semantics requires pre-synthesis optimization

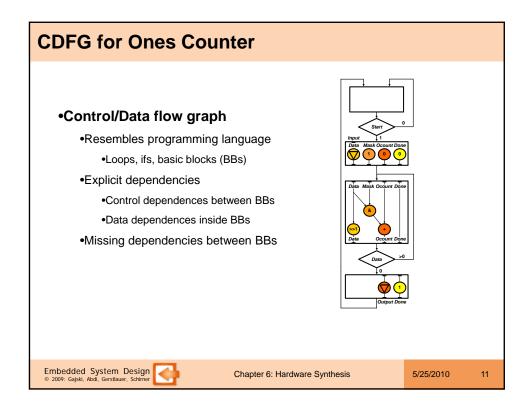

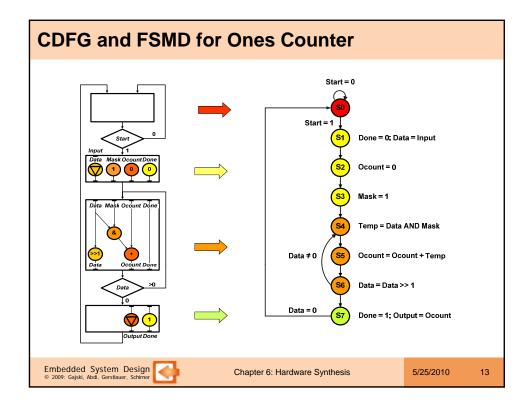

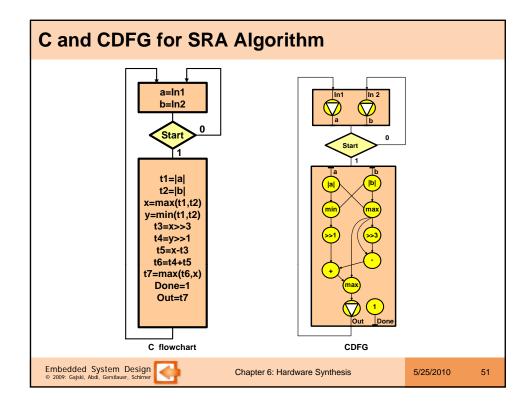

- Control/Data flow graph (CDFG)

- CDFG generation requires dependence analysis

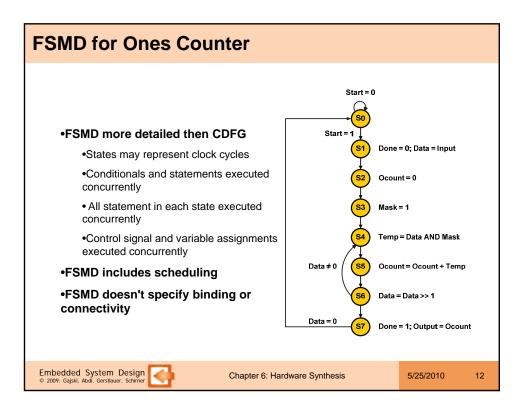

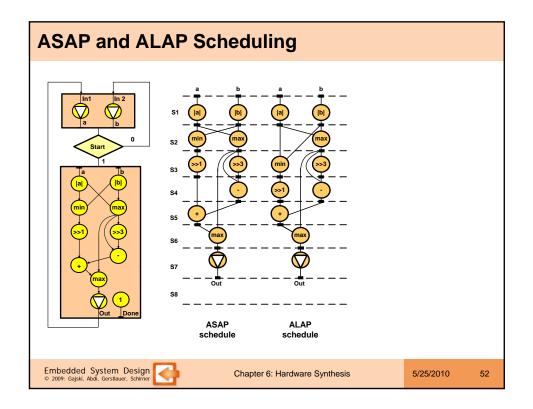

- Finite state machine with data (FSMD)

- State interpretation requires some kind of scheduling

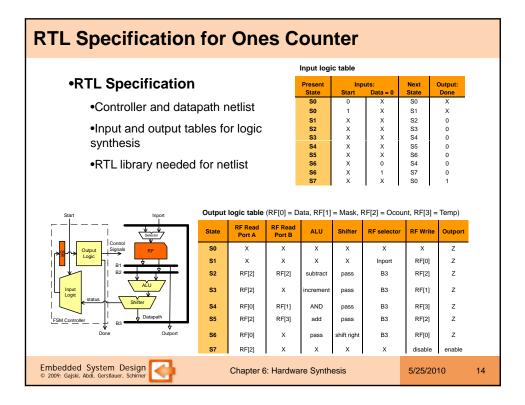

- RTL netlist

- RTL design that requires only input and output logic synthesis

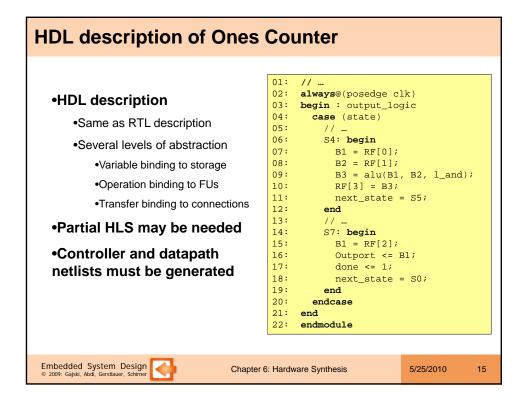

- Hardware description language (Verilog / VHDL)

- HDL description requires RTL library and logic synthesis

| Embedded System Design Chapter 6: Hardware Synthesis 5/25/2010 | 9 |

|----------------------------------------------------------------|---|

| C Code for Ones Counter                                                                                                                                                                                |                                                                                                                                                                                                                                                                |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <ul> <li>•Programming language semantics</li> <li>• Sequential execution,</li> <li>• Coding style to minimize coding</li> <li>•HW design</li> <li>• Parallel execution,</li> </ul>                     |                                                                                                                                                                                                                                                                |  |

| <pre>• Communication through signals<br/>01: int OnesCounter(int Data){<br/>02: int Ocount = 0;<br/>03: int Temp, Mask = 1;<br/>04: while (Data &gt; 0) {<br/>05: Temp = Data &amp; Mask;<br/>06</pre> | <pre>01: while(1) { 02: while (Start == 0); 03: Done = 0; 04: Data = Input; 05: Ocount = 0; 06: Mask = 1; 07: while (Data&gt;0) { 08: Temp = Data &amp; Mask; 09: Ocount = Ocount + Temp; 10: Data &gt;&gt;= 1; 11: } 12: Output = Ocount; 13: Done = 1;</pre> |  |

| Function-based C code                                                                                                                                                                                  | 14: }<br>RTL-based C code                                                                                                                                                                                                                                      |  |

| Embedded System Design Chapt                                                                                                                                                                           | er 6: Hardware Synthesis 5/25/2010 10                                                                                                                                                                                                                          |  |

## Conclusion

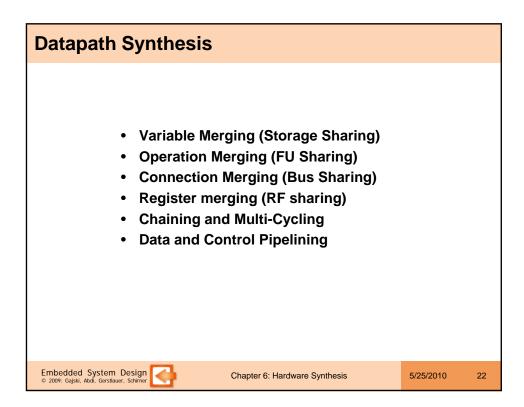

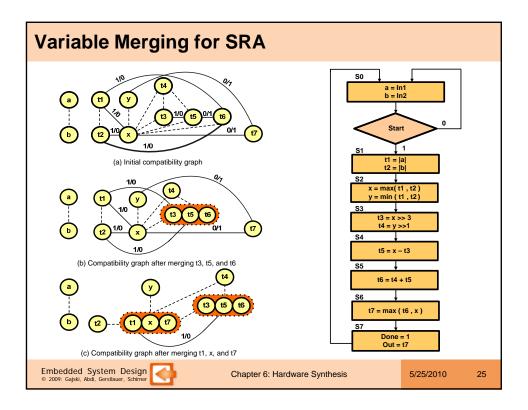

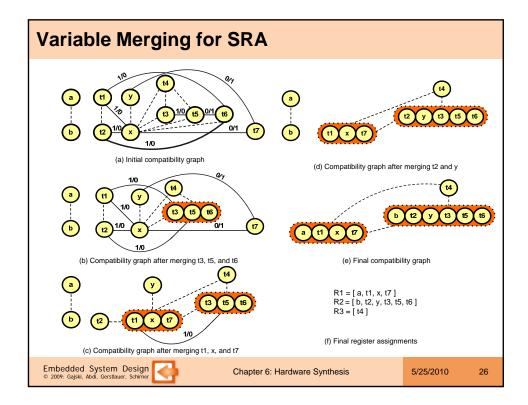

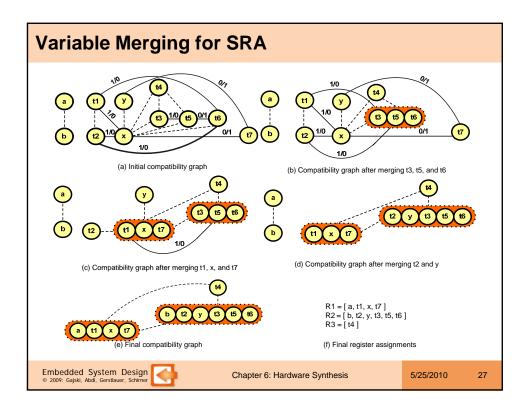

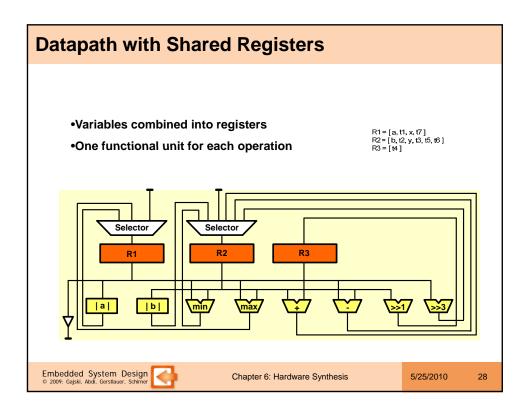

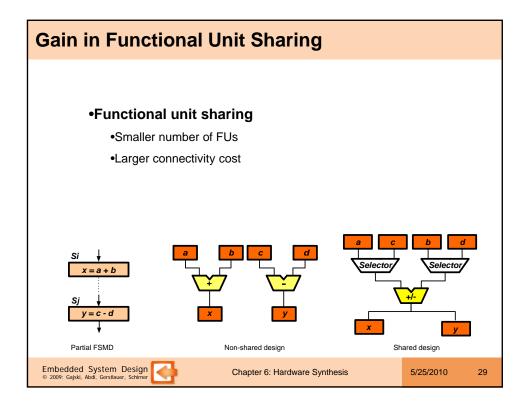

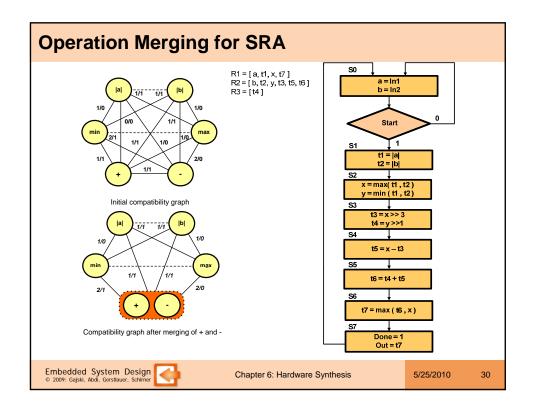

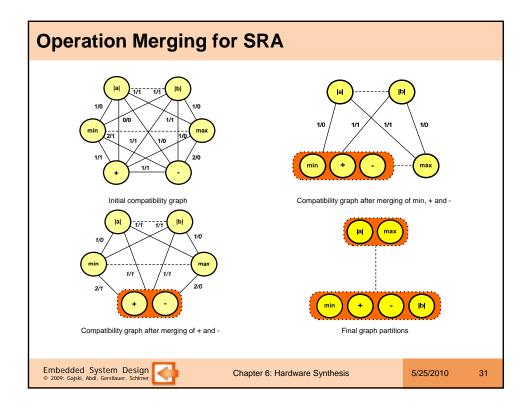

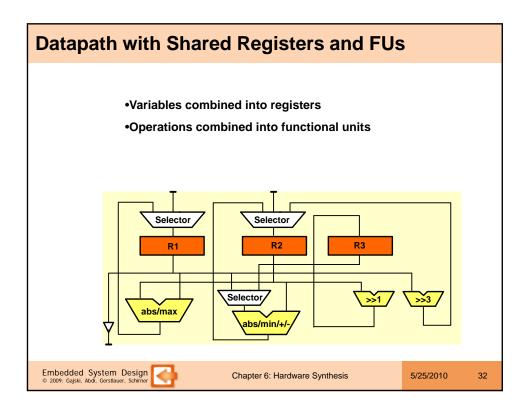

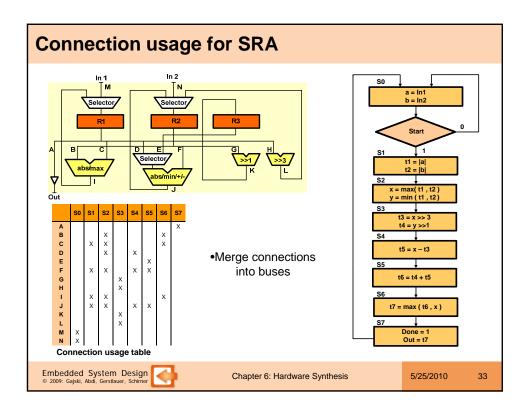

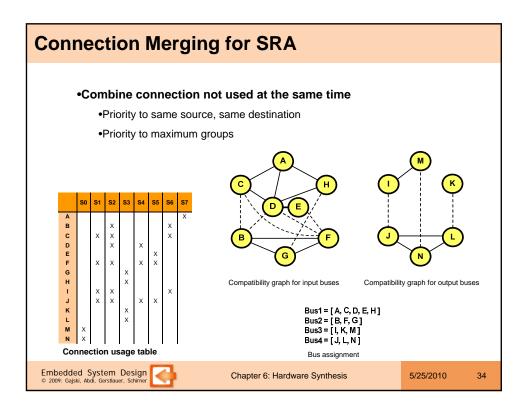

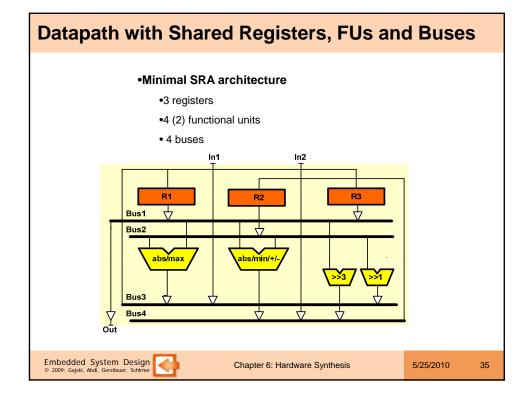

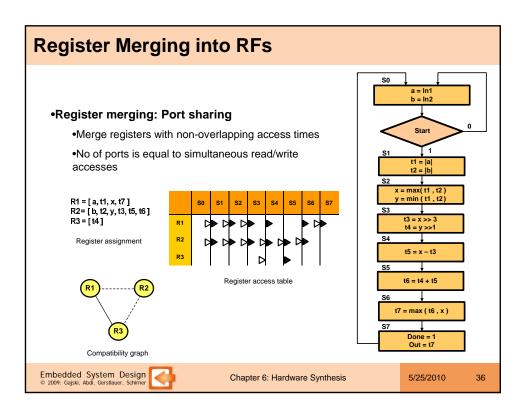

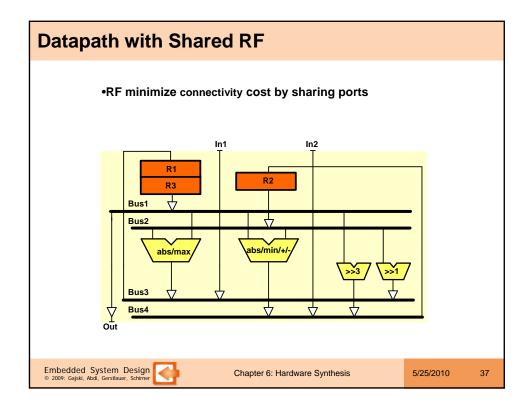

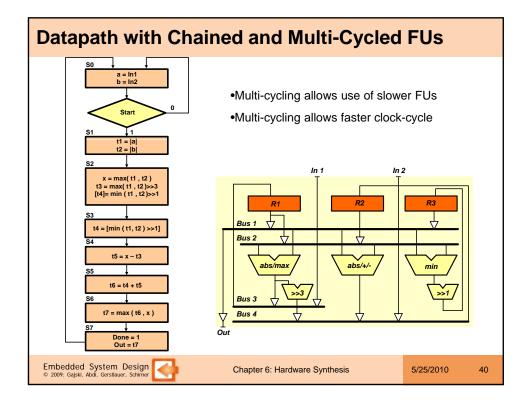

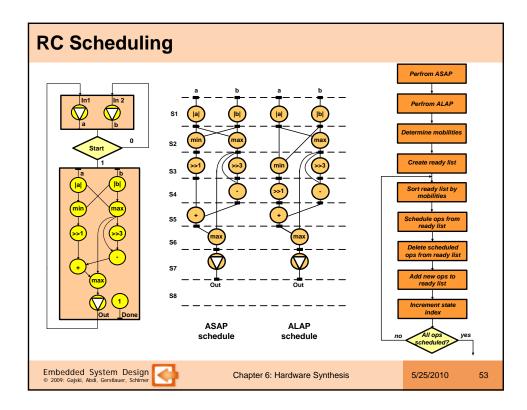

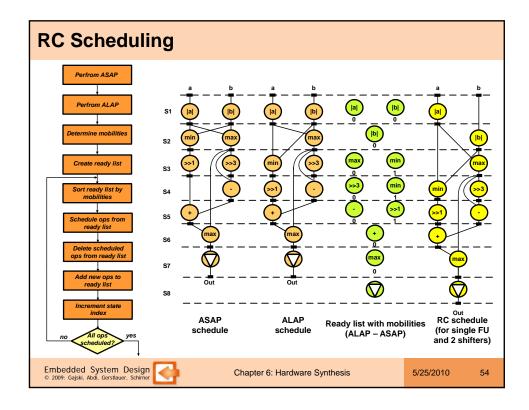

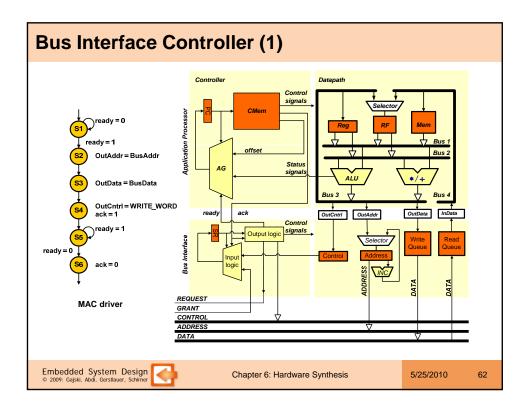

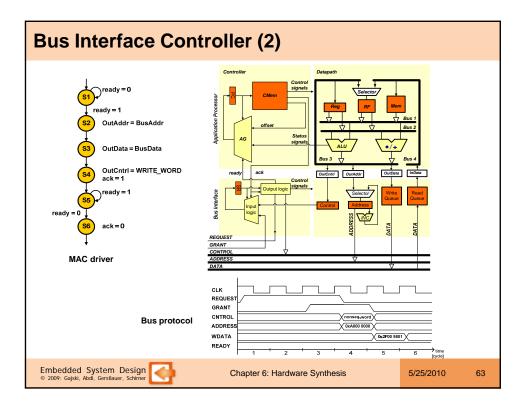

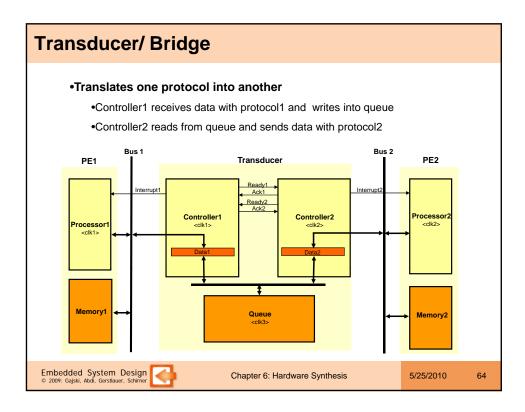

## • Synthesis techniques • Variable Merging (Storage Sharing) • Operation Merging (FU Sharing) Connection Merging (Bus Sharing) • Architecture techniques Chaining and Multi-Cycling • Data and Control Pipelining • Forwarding and Caching • Scheduling • Metric constrained scheduling Interfacing • Part of HW component • Bus interface unit • If too complex, use partial order Embedded System Design © 2009: Gajski, Abdi, Gerstlauer, Schirner 5/25/2010 Chapter 6: Hardware Synthesis 65