# **Embedded System Design**

Modeling, Synthesis, Verification

Daniel D. Gajski, Samar Abdi, Andreas Gerstlauer, Gunar Schirner

System Synthesis

7/08/2009

- System design trends

- Model-based synthesis

- Transaction level model generation

- Application to platform mapping

- Platform generation

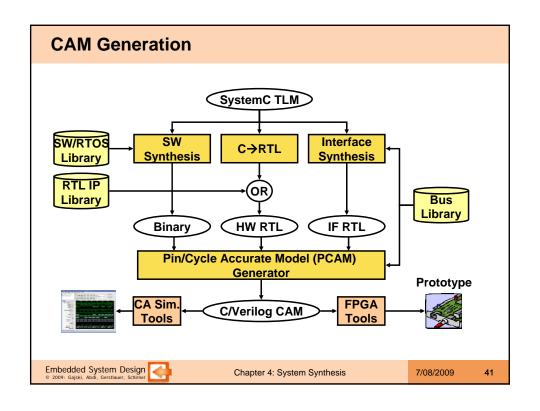

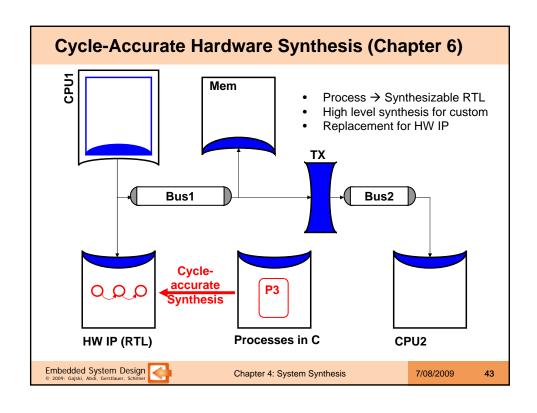

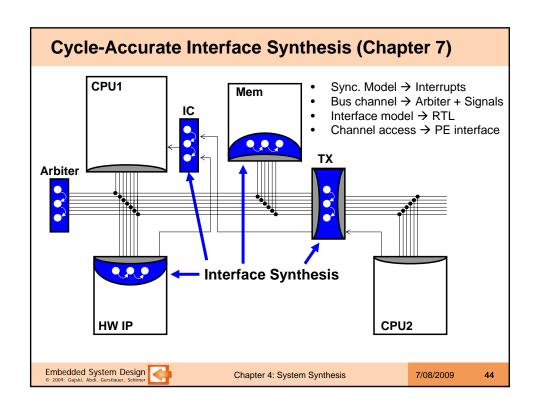

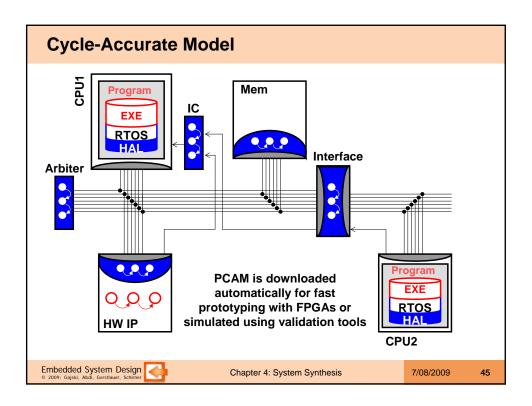

- Cycle-accurate model generation

## **Traditional System Design**

### Hardware first approach

- · Platform is defined by architect or based on legacy

- · Designers develop and verify RTL model of platform

- Slow error prone process

### SW development after HW is finalized

- Debugging is complicated on the board due to limited observablity

- HW errors found during SW development are difficult to rectify

- Application is ported after system SW is finalized

Chapter 4: System Synthesis

7/08/2009

3

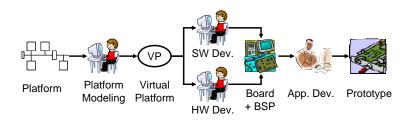

## **Virtual Platform based System Design**

### · Virtual platform (VP) is a fast model of the HW platform

- Typically an instruction set simulator or C/C++ model of the processor

- Peripherals are modeled as remotely callable functions

- · Executes several orders of magnitude faster than RTL

#### SW and HW development are concurrent

- VP serves as the golden model for both SW and HW development

- · SW development can start earlier

- HW designers can use SW for realistic test bench for RTL

Embedded System Design

© 2009: Galski, Abdi, Gerstlauer, Schirner

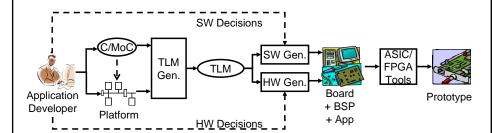

## **Model-based System Design**

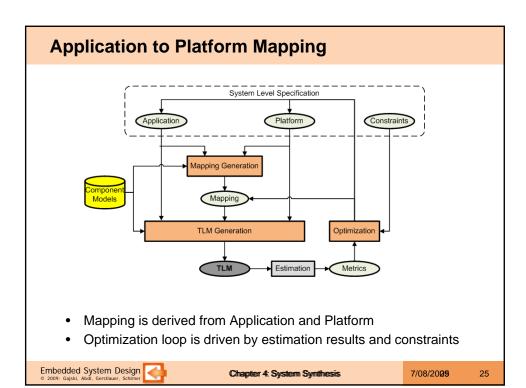

- Model based design gives control to application developers

- Application is captured as high level C/C++/UML specification

- Transaction level model (TLM) is used to verify and evaluate the design

- System synthesis

- The best platform for given application can be synthesized automatically

- For legacy platforms, application mapping can be generated automatically

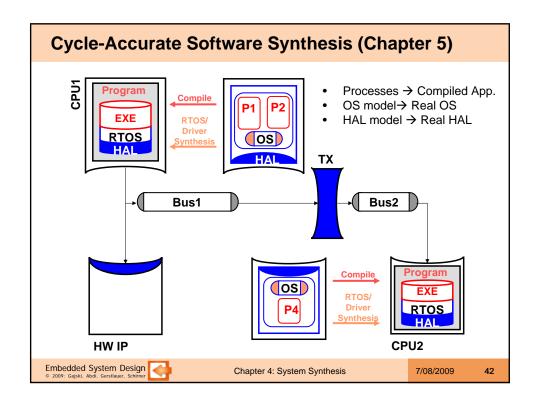

- Cycle accurate SW/HW can be generated from TLM for implementation

Embedded System Design

© 2009: Gajski, Abdi, Gerstlauer, Schirner

Chapter 4: System Synthesis

7/08/2009

\_

- · System design trends

- Model-based synthesis

- Transaction level model generation

- · Application to platform mapping

- Platform generation

- Cycle-accurate model generation

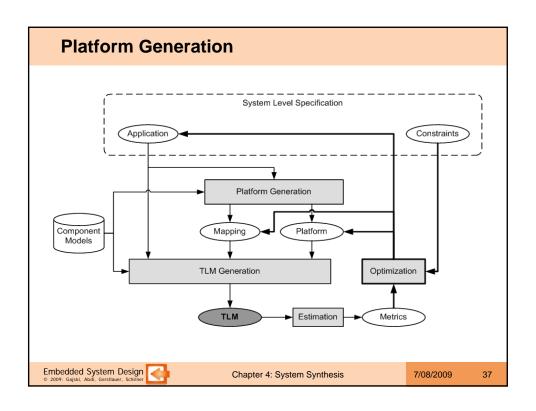

## **Model Based Synthesis**

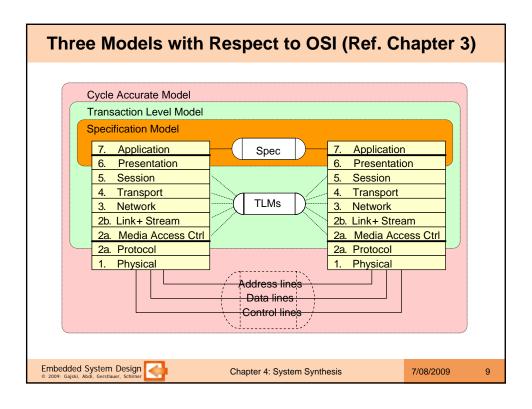

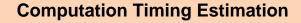

- · Synthesis of cycle-accurate model (CAM) from specification

- · Process may be divided into several steps

- · Specification is defined as application model and design constraints

- Several intermediate models, such as TLMs, may be used

- Platform component models are needed for TLM generation

Embedded System Design

Chapter 4: System Synthesis

7/08/2009

7

## **System Synthesis Inputs and Output**

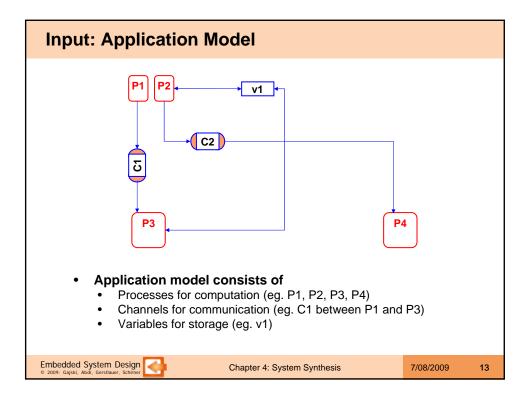

#### Inputs

- Application Model

- Purely functional model

- Specified in a given model of computation (Stateflow, dataflow, CSP, MP)

- Component Models

- Data models of configurability and metrics

- Functional models of component services

- Examples: HW IP models (Processor, Peripheral, Bus), SW IP models (RTOS, Drivers)

- Constraints

- Bounds on metrics (Performance, area, power, reliability, security)

- Optimization goal as a cost function of metrics

#### Output

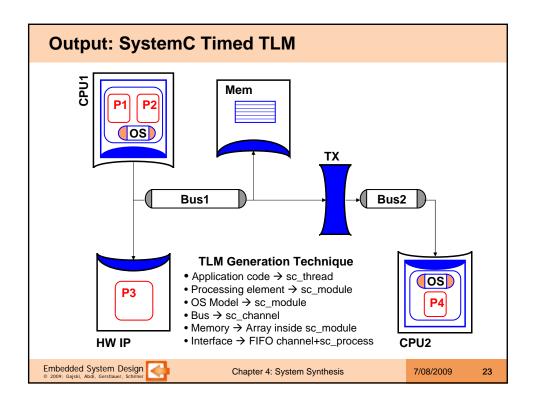

• TLM of application mapped to HW/SW platform

Embedded System Design

Chapter 4: System Synthesis

7/08/2009

8

- System design trends

- Model-based synthesis

- Transaction level model generation

- · Application to platform mapping

- Platform generation

- Cycle-accurate model generation

# **Synthesis Case 1: Fixed Platform and Mapping**

- Initial platform and mapping are given

- · Optimization tools may modify spec under given constraints

Embedded System Design

© 2009: Gajski, Abdi, Gerstlauer, Schirner

Chapter 4: System Synthesis

7/08/2009

11

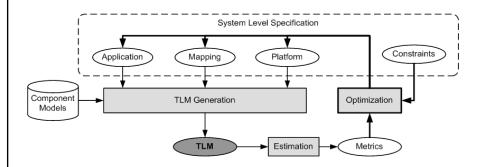

## **Tool support for Synthesis Case 1**

- GUI for application specification

- · GUI for platform specification

- · GUI for application to platform mapping

- TLM generation tool

- · TLM-based metric estimation tools

- · Constraint-based spec optimization tools

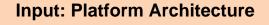

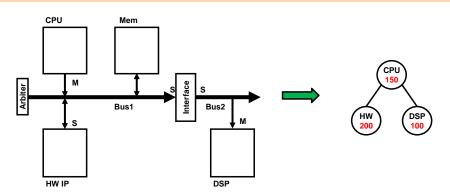

#### Platform consists of

- Hardware: PEs (eg. CPU1, HW), Buses (eg. Bus1), Memories (eg. Mem), Interfaces (eg. Transducer)

- Software: Operating systems (eg. OS1) on SW PEs

Chapter 4: System Synthesis

7/08/2009

15

## **Platform Objects**

#### Processing element (PE)

- Symbolic representation of computation resources

- Different types such as SW processors, HW IPs etc.

#### • Bus

- Symbolic representation of communication media

- Types include shared, point-to-point, link, crossbar etc.

#### Memory

- Symbolic representation of physical storage

- · May contain shared variables or SW program/data

#### Transducer

- · For protocol conversion and store-forward routing

- · Necessary for PEs with different bus protocols

### Operating system (OS)

- Software platform for individual PEs

- Needed for scheduling multiple processes on a PE

Embedded System Design

Chapter 4: System Synthesis

7/08/2009

1

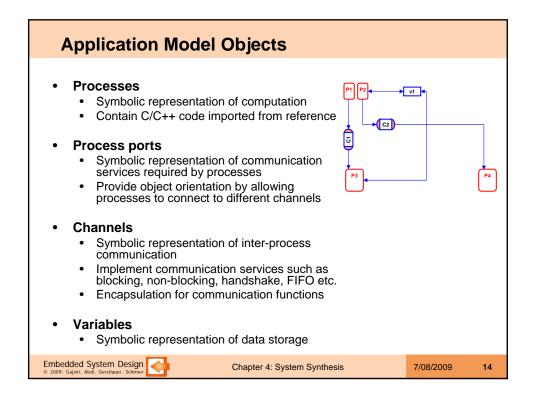

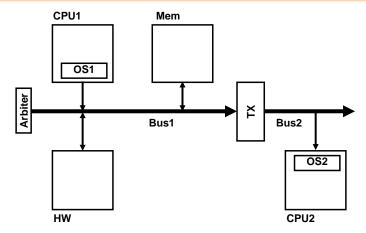

## **Mapping Rules**

#### Processes to PEs

- Each process in the application must be mapped to a PE

- Multiple processes may be mapped to SW PE with OS support

- Example: P1, P2 → CPU1

#### Channels to Routes

- All channels between processes mapped to different PEs are mapped to routes in the platform

- Route consists of bus segments and interfaces

- · Channel on each bus segment is assigned a unique address

#### · Variables to Memories

- Variables accessed by processes mapped to different PEs are mapped to shared memories

- All variables are assigned an address range depending on size

- Stochastic memory delay model

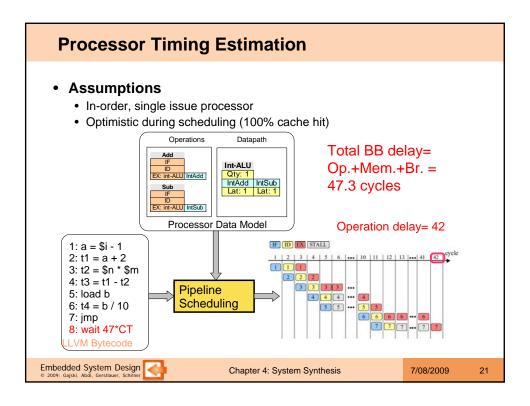

- DFG scheduling to compute basic block delay [DATE 08]

- RTOS model added for PEs with multiple processes

Chapter 4: System Synthesis

7/08/2009

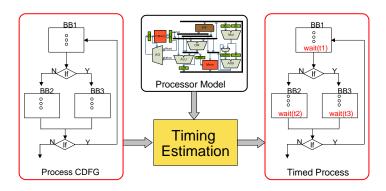

# **Stochastic Memory Delay Model**

- Assumption

- Cache and branch prediction hit rate available in data model

- Delay Estimation

- Operation access overhead =  $N_{op}^{*} ((1.0 HR_i)^{*} (CD + L_{mem}))$

- Data access overhead =  $N_{ld}$  \*  $((1.0 HR_d)$  \*  $(CD + L_{mem}))$

- Branch prediction miss penalty = MP<sub>rate</sub> \* Penalty

Chapter 4: System Synthesis

- System design trends

- Model-based synthesis

- Transaction level model generation

- Application to platform mapping

- Platform generation

- Cycle-accurate model generation

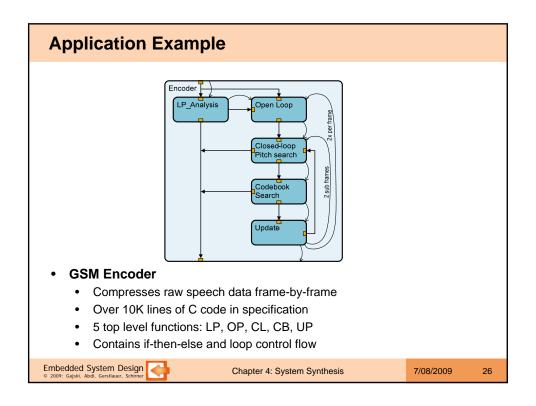

## **Profiling**

- Given input MoC, profile application for:

- Computation

- Number of operations (size)

- Operations type per data type and frequency of use

- Concurrency between modules and dependency

- Communication

- Volume, frequency of communication between modules

- Timing dependency

- Latency requirements

- Storage

- Instruction size

- Variable size

Chapter 4: System Synthesis

7/08/2009

27

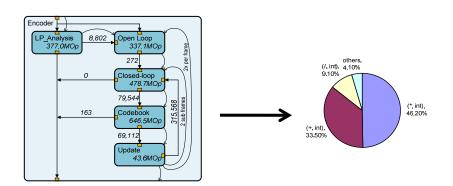

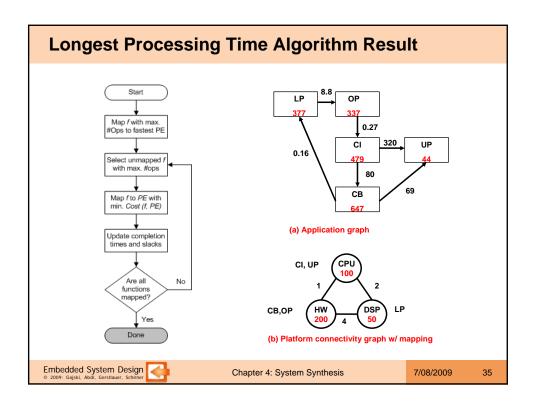

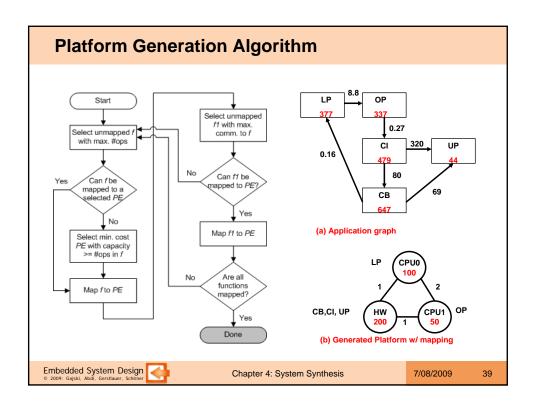

### **Profiled Statistics**

- Profiling helps select the appropriate components for implementation

- All fixed point ops→ No need for processors with floating point units

- Large number of multiplications → Processor with HW multiplier is ideal

- CB is most computationally intensive → Ideal for custom HW mapping

Embedded System Design

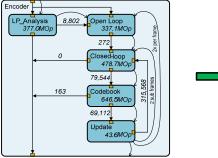

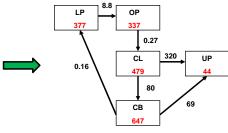

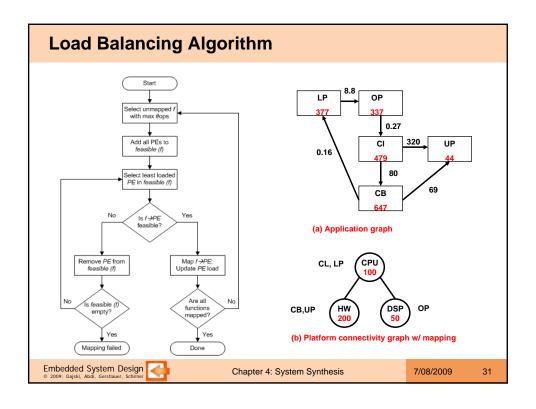

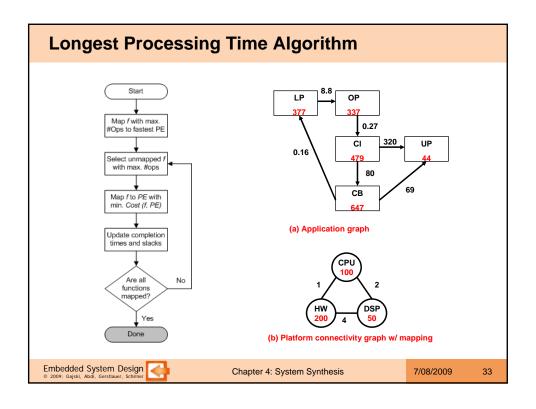

# **Application Graph**

- Profile information is abstracted into a simplified graphical representation for synthesis algorithms

- Node tags = millions of operations

- Edge tags = kilobytes transferred

- Control dependencies are excluded for simplicity

Embedded System Design

© 2009: Gajski, Abdi, Gerstlauer, Schirner

Chapte Chapte

Chapter 4: System Synthesis

7/08/2009

29

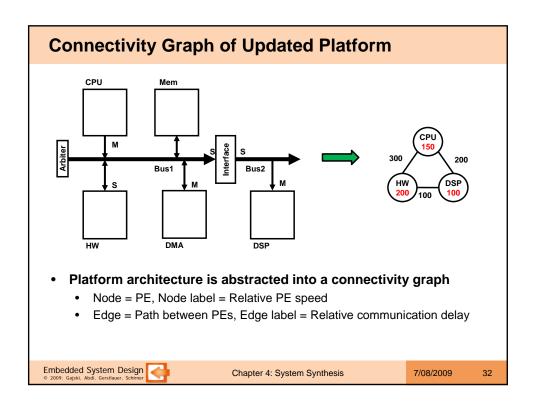

# **Platform Connectivity Graph**

- Platform architecture is abstracted into a connectivity graph showing possibility of inter-PE communication

- Node tag = PE speed (relative)

- No edge between HW and DSP due to missing DMA on Bus1

Embedded System Design

Chapter 4: System Synthesis

7/08/2009

30

- System design trends

- Model-based synthesis

- Transaction level model generation

- Application to platform mapping

- → Platform generation

- Cycle-accurate model generation

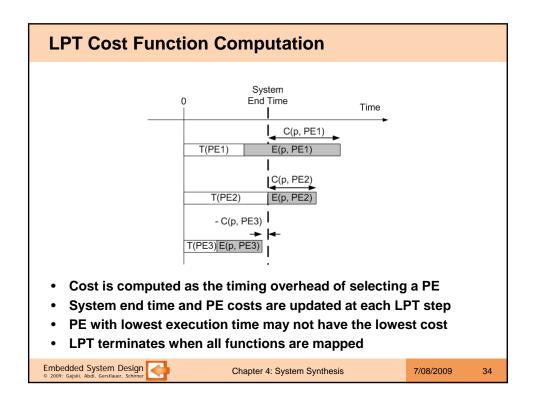

## **Component Database**

| PE Type | Cost | Speed | Capacity<br>(Speed *6 sec) |

|---------|------|-------|----------------------------|

| CPU     | 2    | 100   | 600                        |

| DSP     | 1    | 50    | 300                        |

| HW      | 5    | 200   | 1200                       |

- Timing constraint: Application must complete in <6 seconds.

- Database of processing elements used for component selection

- · Characterized by type, cost and speed

- Computation capacity is the PE speed multiplied by timing constraint

- Similar library for buses and memories may be used

- System design trends

- Model-based synthesis

- Transaction level model generation

- Application to platform mapping

- → Platform generation

- Cycle-accurate model generation

## **Summary**

- Emergence of model-based system design

- Virtual platforms replace prototypes for early SW development

- Increasing adoption of TLMs for SW/HW design

- · Challenges for synthesis of large system designs

- Manual model development is time consuming and error-prone

- Different platforms are needed for different application domains

- · Mapping application to a multi-core platform is complicated

- Need for well defined model semantics is needed at TLM and cycle-accurate levels

- Enables automatic TLM generation

- System synthesis becomes possible

- Future of system synthesis

- · Based on formalized system level models such as TLM

- Automatic mapping of application to platform

- Automatic generation of application specific platforms