#include "sysc/kernel/sc_simcontext.h"#include "sysc/datatypes/bit/sc_logic.h"#include "sysc/communication/sc_signal_ifs.h"

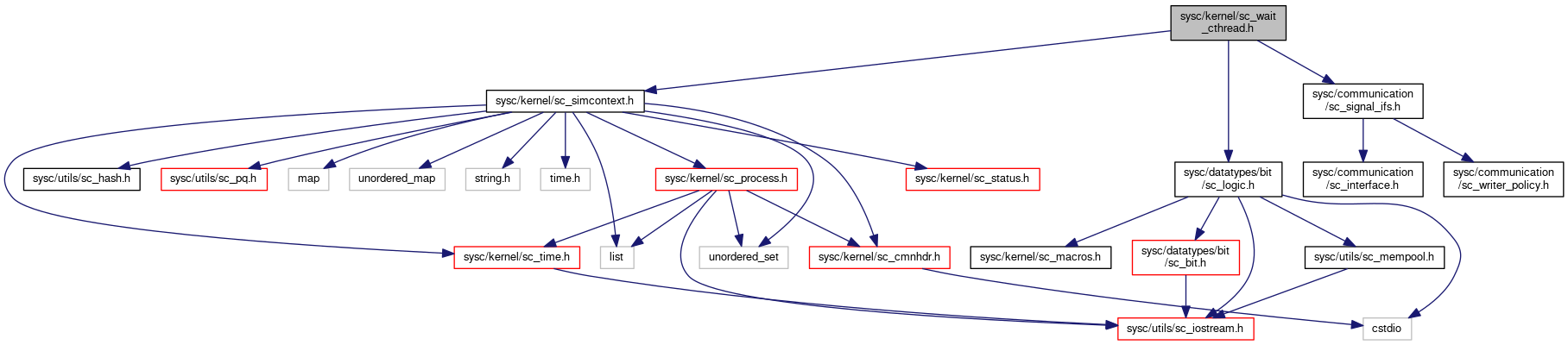

Include dependency graph for sc_wait_cthread.h:

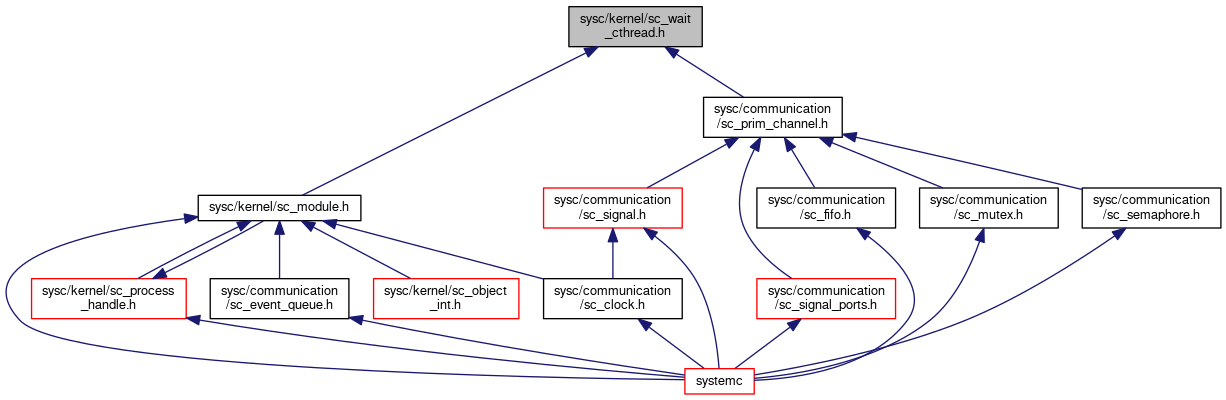

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Namespaces | |

| sc_core | |

Functions | |

| void | sc_core::halt (int, sc_simcontext *=sc_get_curr_simcontext()) |

| A new parameter segment ID is added for the out-of-order simulation. More... | |

| void | sc_core::wait (int, int, sc_simcontext *=sc_get_curr_simcontext()) |

| A new parameter segment ID is added for the out-of-order simulation. More... | |

| void | sc_core::at_posedge (const sc_signal_in_if< bool > &, int, sc_simcontext *=sc_get_curr_simcontext()) |

| A new parameter segment ID is added for the out-of-order simulation. More... | |

| void | sc_core::at_posedge (const sc_signal_in_if< sc_dt::sc_logic > &, int, sc_simcontext *=sc_get_curr_simcontext()) |

| A new parameter segment ID is added for the out-of-order simulation. More... | |

| void | sc_core::at_negedge (const sc_signal_in_if< bool > &, int, sc_simcontext *=sc_get_curr_simcontext()) |

| A new parameter segment ID is added for the out-of-order simulation. More... | |

| void | sc_core::at_negedge (const sc_signal_in_if< sc_dt::sc_logic > &, int, sc_simcontext *=sc_get_curr_simcontext()) |

| A new parameter segment ID is added for the out-of-order simulation. More... | |

1.8.5

1.8.5