# System-level Modeling and Design with the SpecC Language

#### **Dissertation**

zur Erlangung des Grades eines

Doktors der Naturwissenschaften

der Universität Dortmund

am Fachbereich Informatik

von **Rainer Dömer**

Dortmund 2000

| Tag der mündlichen Prüfung: |  |  |

|-----------------------------|--|--|

| Dekan/Dekanin:              |  |  |

| Gutachter:                  |  |  |

|                             |  |  |

|                             |  |  |

|                             |  |  |

|                             |  |  |

|                             |  |  |

|                             |  |  |

## System-level Modeling and Design with the SpecC Language

#### **Dissertation**

for the degree of "Doktor der Naturwissenschaften"

submitted to the

Department of Computer Science

at University of Dortmund

by **Rainer Dömer**

Dortmund, Germany 2000

For Julia

### **Abstract**

The semiconductor roadmap estimates the design complexity for digital systems to continue to increase according to Moore's law. In the next years, embedded systems with 10ths of millions of transistors on one chip will be standard technology. System-on-Chip (SOC) designs will integrate processor cores, memories and special-purpose custom logic into a complete system fitting on a single die. However, the increased complexity of SOC designs requires more effort, more efficient tools and new methodologies. Increasing the design time is not an option due to market pressures.

System-level design reduces the complexity of the design models by raising the level of abstraction. Starting from an abstract specification model, the system is step-wise refined with the help of computer-aided design (CAD) tools. Using codesign techniques, the system is partitioned into hardware and software parts and finally implemented on a target architecture. Established design methodologies for behavioral synthesis and standard software design are utilized. However, moving to higher abstraction levels is not sufficient.

The key to cope with the complexity involved with SOC designs is the reuse of Intellectual Property (IP). The integration of complex components, which are predesigned and well-tested, drastically reduces the design complexity and, thus, saves design time and allows a shorter time-to-market. Since the idea of IP reuse promises great benefits, it must become an integral part in the system design methodology. Furthermore, the use of IP components must be directly supported by the design models, the tools and the languages being used throughout the design process. For example, it must be easy to insert and replace IP components in the design model ("plug-and-play").

This work addresses the main issues in SOC design, namely the system design methodology, system-level modeling, and the specification language.

First, an IP-centric system design methodology is proposed which is based on the reuse of IP. It allows the reuse and integration of IP components at any level and at any time during the design process. Starting with an abstract executable specification of the system, architecture exploration and communication synthesis are performed in order to map the design model onto the target architecture. At any stage, the systems functionality and its characteristics can be evaluated and validated.

The model being used in the methodology to represent the system must meet system

design requirements. It must be suitable to represent abstract properties at early stages as well as specific details about design decisions later in the design process. In order to support IP, the model must clearly separate communication from computation. In this work, a hierarchical model is described which encapsulates computation and communication in separate entities, namely behaviors and channels. This model naturally supports reuse, integration and protection of IP.

In order to formally describe a design model, a language should be used which directly represents the properties and characteristics of the model. This work presents a newly developed language, called SpecC, which allows to map modeling concepts onto language constructs in a one to one fashion. Unlike other system-level languages, the SpecC language precisely covers the unique requirements for embedded systems design in an orthogonal manner. Built on top of the C language, the de-facto standard for software development, SpecC supports additional concepts needed in hardware design and allows IP-centric modeling. Recently, the SpecC language has been proposed as a standard system-level language for adoption in industry by some of Japan's top-tier electronics and semiconductor companies.

The proposed methodology and the SpecC language have been implemented in the SpecC design environment. In a graphical framework, the SpecC design environment integrates a set of CAD tools which support system-level modeling, design validation, design space exploration, and (semi-) automatic refinement. The framework and all tools rely on a powerful, central design representation, the SpecC Internal Representation (SIR).

Using the SpecC design environment, the IP-centric methodology has been successfully applied to several designs of industrial size, including a GSM vocoder used in mobile telecommunication.

## **Contents**

| 1 | Intr | oduction | n 1                                    |

|---|------|----------|----------------------------------------|

|   | 1.1  | System   | n-level Design                         |

|   |      | 1.1.1    | Levels of abstraction                  |

|   |      | 1.1.2    | The Y-Chart                            |

|   |      | 1.1.3    | Models of computation                  |

|   |      | 1.1.4    | System design process                  |

|   |      |          | 1.1.4.1 Specification                  |

|   |      |          | 1.1.4.2 Validation                     |

|   |      |          | 1.1.4.3 Refinement                     |

|   |      |          | 1.1.4.4 Methodology                    |

|   |      | 1.1.5    | Intellectual Property                  |

|   |      |          | 1.1.5.1 IP components                  |

|   |      |          | 1.1.5.2 IP reuse                       |

|   |      |          | 1.1.5.3 IP protection                  |

|   |      |          | 1.1.5.4 IP requirements                |

|   | 1.2  | Related  | d Work                                 |

|   |      | 1.2.1    | Design systems                         |

|   |      |          | 1.2.1.1 Homogeneous specification      |

|   |      |          | 1.2.1.2 Heterogeneous specification    |

|   |      | 1.2.2    | Languages                              |

|   |      |          | 1.2.2.1 Software programming languages |

|   |      |          | 1.2.2.2 Hardware description languages |

|   |      |          | 1.2.2.3 Codesign languages             |

|   |      |          | 1.2.2.4 System-level languages         |

|   | 1.3  | Goals    |                                        |

|   | 1 4  | Outline  | e 27                                   |

viii CONTENTS

| 2 | IP-c | entric N | Modeling                  | 29 |

|---|------|----------|---------------------------|----|

|   | 2.1  | Comp     | utation and Communication | 30 |

|   | 2.2  | The Sp   | pecC Model                | 32 |

|   |      | 2.2.1    | Basic structure           | 32 |

|   |      | 2.2.2    | Test bench                | 33 |

|   | 2.3  | Comp     | utation Models            | 33 |

|   |      | 2.3.1    | Algorithmic program       | 33 |

|   |      | 2.3.2    | Sequential execution      | 35 |

|   |      | 2.3.3    | Concurrent execution      | 35 |

|   |      | 2.3.4    | Exceptions                | 35 |

|   |      | 2.3.5    | IP model                  | 36 |

|   | 2.4  | Comm     | nunication Models         | 36 |

|   |      | 2.4.1    | Shared memory model       | 36 |

|   |      | 2.4.2    | Channel models            | 37 |

|   | 2.5  | Model    | ling with IP              | 39 |

|   |      | 2.5.1    | Channel model             | 39 |

|   |      | 2.5.2    | Wrapper model             | 40 |

|   |      | 2.5.3    | Adapter model             | 41 |

|   |      | 2.5.4    | Inlining                  | 41 |

| 3 | The  | SpecC    | Design Methodology        | 45 |

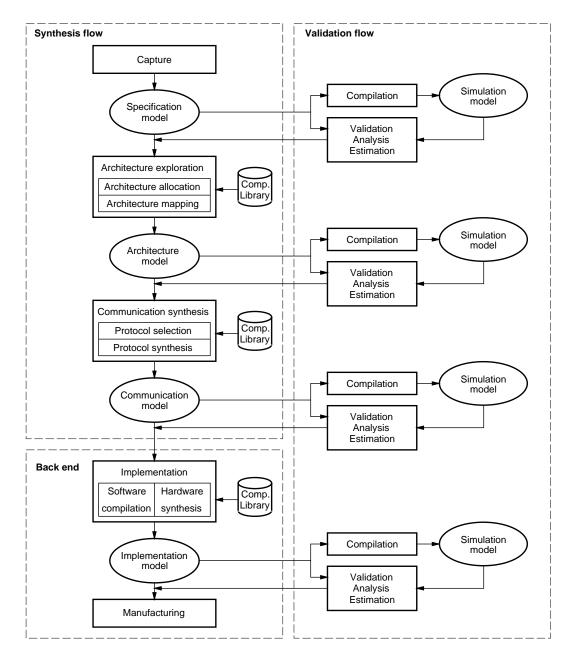

|   | 3.1  | Overv    | iew                       | 45 |

|   | 3.2  | Specif   | fication Capture          | 48 |

|   |      | 3.2.1    | The specification model   | 49 |

|   | 3.3  | Valida   | tion and Analysis         | 49 |

|   |      | 3.3.1    | Simulation                | 50 |

|   |      | 3.3.2    | Estimation                | 51 |

|   | 3.4  | Archit   | ecture Exploration        | 52 |

|   |      | 3.4.1    | Architecture allocation   | 53 |

|   |      | 3.4.2    | Architecture mapping      | 54 |

|   |      |          | 3.4.2.1 Behavior mapping  | 55 |

|   |      |          | 3.4.2.2 Scheduling        | 57 |

|   |      |          | 3.4.2.3 Variable mapping  | 58 |

|   |      |          | 3.4.2.4 Channel mapping   | 60 |

|   |      | 3.4.3    | The architecture model    | 62 |

|   | 3.5  | Comm     | nunication Synthesis      | 64 |

|   |      | 3.5.1    | Protocol selection        | 64 |

|   |      | 3.5.2    | Transducer insertion      | 65 |

|   |      | 3.5.3    | Protocol synthesis        | 67 |

|   |      | 3.5.4    | The communication model   | 68 |

*CONTENTS* ix

|   | 3.6 | Back e  | nd                             |

|---|-----|---------|--------------------------------|

|   |     | 3.6.1   | Hardware synthesis             |

|   |     | 3.6.2   | Software compilation           |

|   |     | 3.6.3   | The implementation model       |

| 4 | The | SpecC : | Language 73                    |

|   | 4.1 | Langua  | age Requirements               |

|   |     | 4.1.1   | Executability                  |

|   |     | 4.1.2   | Synthesizability               |

|   |     | 4.1.3   | Modularity                     |

|   |     |         | 4.1.3.1 Behavioral hierarchy   |

|   |     |         | 4.1.3.2 Structural hierarchy   |

|   |     | 4.1.4   | Completeness                   |

|   |     |         | 4.1.4.1 Concurrency            |

|   |     |         | 4.1.4.2 Synchronization        |

|   |     |         | 4.1.4.3 Exception handling     |

|   |     |         | 4.1.4.4 Timing                 |

|   |     |         | 4.1.4.5 State transitions      |

|   |     | 4.1.5   | Orthogonality                  |

|   | 4.2 | Langua  | age Comparison                 |

|   | 4.3 | _       | ation                          |

|   |     | 4.3.1   | Types and expressions          |

|   |     |         | 4.3.1.1 Boolean type           |

|   |     |         | 4.3.1.2 Bit vector type        |

|   |     |         | 4.3.1.3 Event type             |

|   |     |         | 4.3.1.4 Time type              |

|   |     | 4.3.2   | Statements and declarations    |

|   | 4.4 | Basic S | Structure                      |

|   | 4.5 | Behavi  | oral Hierarchy                 |

|   |     | 4.5.1   | Sequential execution           |

|   |     |         | 4.5.1.1 Imperative program     |

|   |     |         | 4.5.1.2 Finite state machine   |

|   |     | 4.5.2   | Concurrent execution           |

|   |     |         | 4.5.2.1 Parallel execution     |

|   |     |         | 4.5.2.2 Pipelined execution 89 |

|   | 4.6 | Structu | ral Hierarchy                  |

|   |     | 4.6.1   | Behaviors                      |

|   |     | 4.6.2   | Netlists                       |

|   | 4.7 | Comm    | unication                      |

|   |     | 471     | Channels 93                    |

X CONTENTS

|   |            | 4.7.2    | Interfaces                        | 94  |

|---|------------|----------|-----------------------------------|-----|

|   | 4.8        | Synchr   | ronization                        | 96  |

|   | 4.9        | Except   | ion Handling                      | 97  |

|   |            | 4.9.1    | Interrupt                         | 97  |

|   |            | 4.9.2    | Abortion                          | 98  |

|   | 4.10       | Timing   | Ţ                                 | 98  |

|   |            | 4.10.1   | Exact timing                      | 98  |

|   |            |          | Timing ranges                     |     |

|   | 4.11       |          | ent Annotation                    |     |

|   | 4.12       | Library  | Support                           | 102 |

|   | 4.13       | Summa    | ary                               | 103 |

|   | 4.14       | Possibl  | le Extensions                     | 104 |

|   |            | 4.14.1   | Fine tuning                       | 104 |

|   |            | 4.14.2   | Operator overloading              | 104 |

|   |            | 4.14.3   | Object orientation                | 105 |

|   |            | 4.14.4   | Templates                         | 105 |

| _ | -          |          |                                   | 40- |

| 5 |            | _        | Design Environment                | 107 |

|   | 5.1        |          | ew                                |     |

|   | <i>5</i> 2 | 5.1.1    | SpecC release 2.0.4               |     |

|   | 5.2        | •        | Internal Representation           |     |

|   |            | 5.2.1    | SIR File format                   |     |

|   |            | 5.2.2    | SIR library                       |     |

|   |            | 5.2.3    | Application Programming Interface |     |

|   |            |          | 5.2.3.1 Kernel layer              |     |

|   |            | 504      | 5.2.3.2 Hierarchy layer           |     |

|   |            | 5.2.4    | Experiment                        |     |

|   |            |          | 5.2.4.1 Example application       |     |

|   | <i>5</i> 2 | C C      | 5.2.4.2 Results                   |     |

|   | 5.3        | _        | Compiler                          |     |

|   | 5.4        | 5.4.1    | Refinement Tools                  |     |

|   |            | 5.4.1    | SpecC profiler                    |     |

|   |            | 3.4.2    | SpecC tool set                    | 121 |

| 6 | IP P       | rotectio | n in the SpecC System             | 123 |

|   | 6.1        | Public   | IP Declaration                    | 124 |

|   |            | 6.1.1    | Behavior IP                       | 124 |

|   |            | 6.1.2    | Channel IP                        | 124 |

|   | 6.2        | Secret   | IP Implementation                 | 125 |

|   |            | 6.2.1    | Implementation problem            |     |

*CONTENTS* xi

|   |            | 6.2.2    | Implementation solution               | 127 |

|---|------------|----------|---------------------------------------|-----|

|   | 6.3        | Integrat | tion with the SpecC compiler          | 128 |

|   | 6.4        | Experir  | ments and Results                     | 129 |

|   |            | 6.4.1    | RT level IP examples                  | 129 |

|   |            | 6.4.2    | System level IP examples              | 130 |

| _ | ~          |          |                                       | 122 |

| 7 |            | clusion  |                                       | 133 |

|   | 7.1        |          | outions                               |     |

|   |            | 7.1.1    | IP-centric model                      |     |

|   |            | 7.1.2    | IP-centric methodology                |     |

|   |            | 7.1.3    | SpecC language                        |     |

|   |            | 7.1.4    | SpecC design environment              |     |

|   |            |          | 7.1.4.1 SpecC Internal Representation |     |

|   |            | - 1 ·    | 7.1.4.2 SpecC compiler                |     |

|   |            | 7.1.5    | IP protection                         |     |

|   |            | 7.1.6    | Experience                            |     |

|   | <b>7</b> 0 | 7.1.7    | Impact                                |     |

|   | 7.2        |          | Work                                  |     |

|   |            | 7.2.1    | SpecC language                        |     |

|   |            | 7.2.2    | Synthesis flow                        | 139 |

| A | Spec       | C Users  | s Manual                              | 141 |

|   | A.1        | SpecC    | Compiler scc                          | 141 |

|   | A.2        | SpecC    | Profiler sprof                        | 149 |

|   | A.3        | SpecC    | Tool Set                              | 153 |

|   |            | A.3.1    | sir_delete                            | 153 |

|   |            | A.3.2    | sir_list                              | 155 |

|   |            | A.3.3    | sir_note                              | 159 |

|   |            | A.3.4    | sir_rename                            | 161 |

|   |            | A.3.5    | sir_strip                             | 163 |

|   |            | A.3.6    | sir_tree                              | 165 |

| В | Snor       | C Docio  | gn Examples                           | 169 |

| D | B.1        | _        | ll Examples                           | 169 |

|   | B.2        |          | Example                               |     |

|   | B.3        | -        | -                                     |     |

|   | в.3<br>В.4 |          | ller Examples                         |     |

|   | B.5        |          | Encoder                               |     |

|   |            |          | Vocoder                               | 173 |

|   | D.O        | CIDIVI V | /UCUUCI                               | 1/4 |

| xii | CONTENTS |

|-----|----------|

| X11 | CONTENTS |

| $\mathbf{C}$ | Spec   | C Internal Representation | 179 |

|--------------|--------|---------------------------|-----|

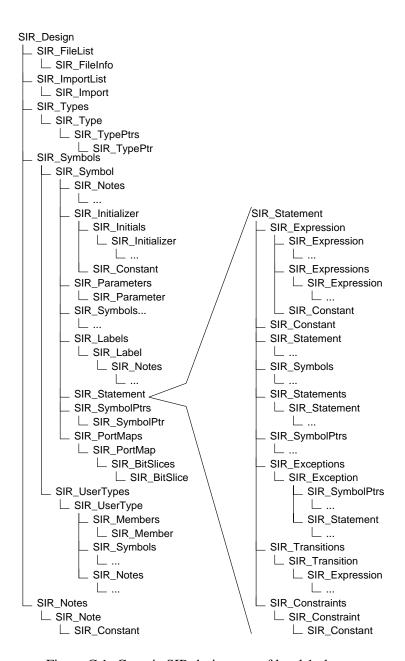

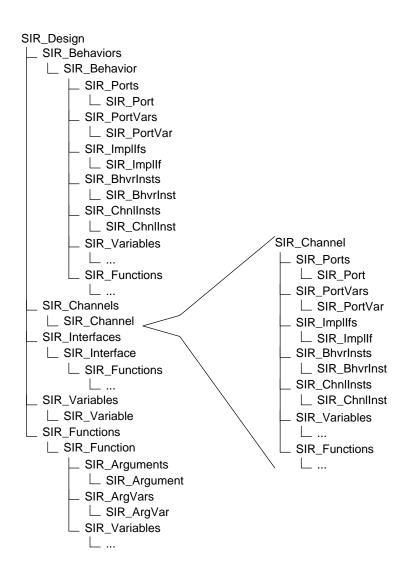

|              | C.1    | SIR graph                 | 179 |

|              | C.2    | Design Trees              | 182 |

|              | C.3    | Base Classes              | 183 |

|              | C.4    | Error Handling            | 183 |

| Bil          | oliogr | aphy                      | 185 |

| Gl           | ossary | Ÿ                         | 195 |

| Inc          | lex    |                           | 199 |

## **List of Figures**

| 1.1  | Abstraction versus complexity               | 4  |

|------|---------------------------------------------|----|

| 1.2  | System-level design in the Y-Chart          | 6  |

| 1.3  | Design process using step-wise refinement   | 9  |

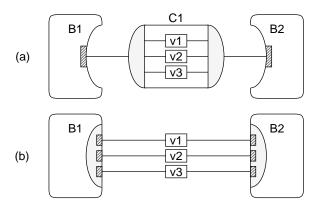

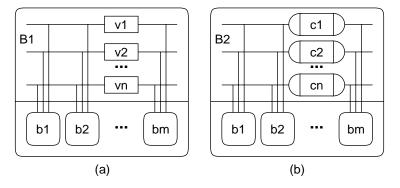

| 2.1  | Separation of computation and communication | 30 |

| 2.2  | Communication inlining                      | 31 |

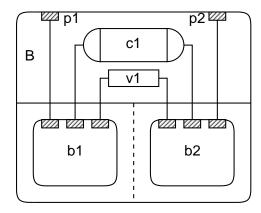

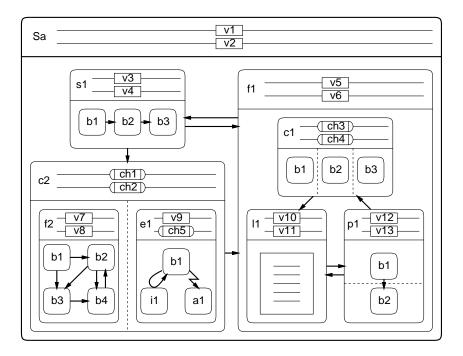

| 2.3  | Example of a SpecC model                    | 32 |

| 2.4  | Typical test bench model                    | 33 |

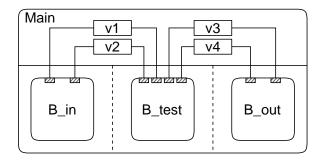

| 2.5  | Behavior models                             | 34 |

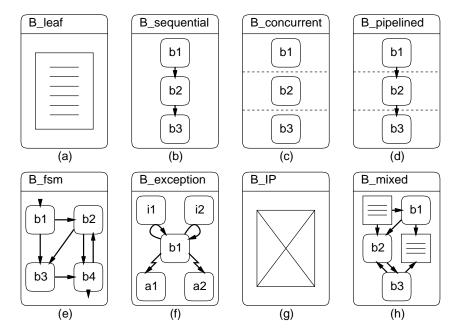

| 2.6  | Models of communication                     | 37 |

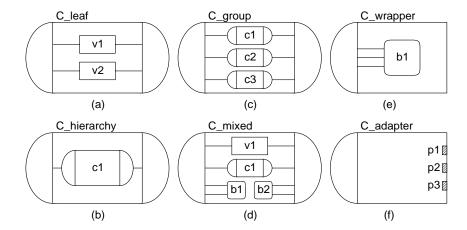

| 2.7  | Channel models                              | 38 |

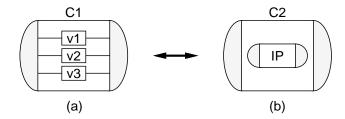

| 2.8  | IP channel model                            | 40 |

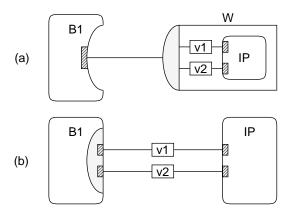

| 2.9  | IP wrapper model                            | 40 |

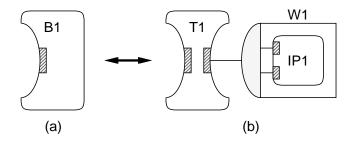

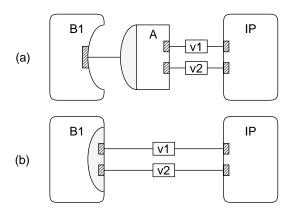

| 2.10 | IP adapter model                            | 41 |

| 2.11 | Wrapper inlining                            | 42 |

| 2.12 | Adapter inlining                            | 42 |

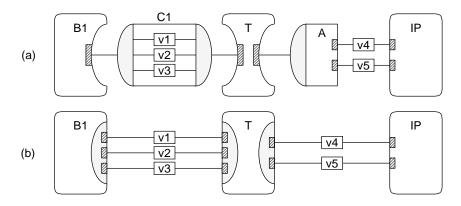

|      | Inlining with transducer                    | 43 |

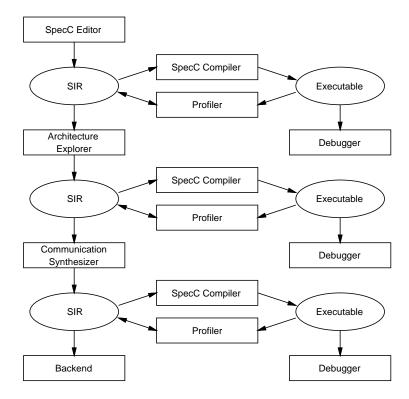

| 3.1  | SpecC system design methodology             | 46 |

| 3.2  | Specification model                         | 50 |

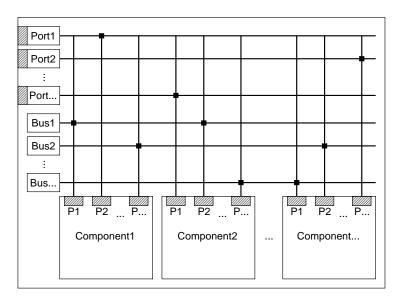

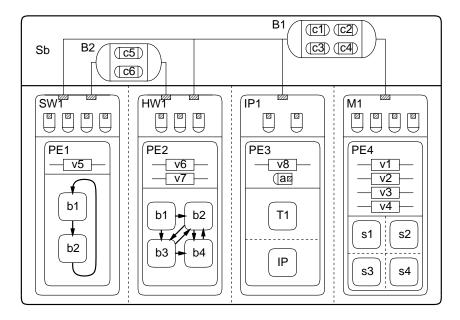

| 3.3  | Generic system architecture                 | 53 |

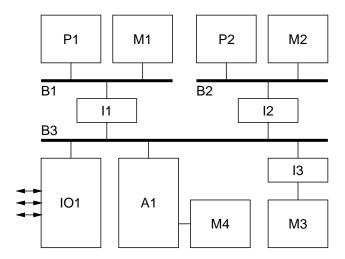

| 3.4  | Example of a system architecture            | 54 |

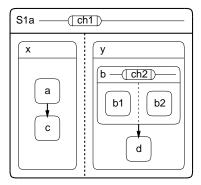

| 3.5  | Design example S1 before behavior mapping   | 55 |

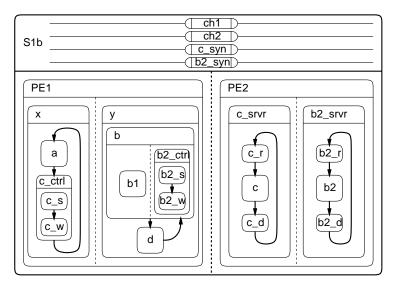

| 3.6  | Design example S1 after behavior mapping    | 56 |

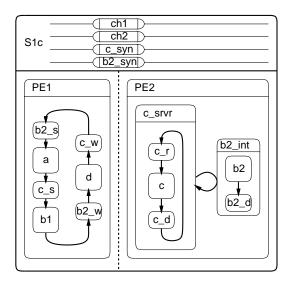

| 3.7  | Design example S1 after scheduling          | 57 |

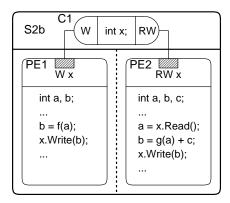

| 3.8  | Design example S2, initial specification    | 59 |

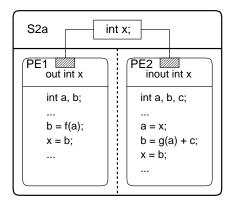

| 3.9  | Design example S2 before variable mapping   | 59 |

| 3.10 | Design example S2 after variable mapping    | 60 |

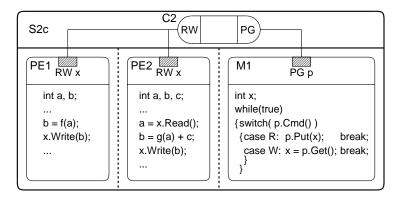

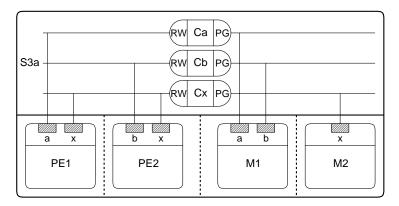

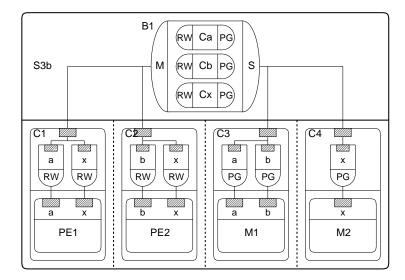

| 3.11 | Design example S3 before channel mapping    | 61 |

| 3.12 | Design example S3 after channel mapping     | 62 |

xiv LIST OF FIGURES

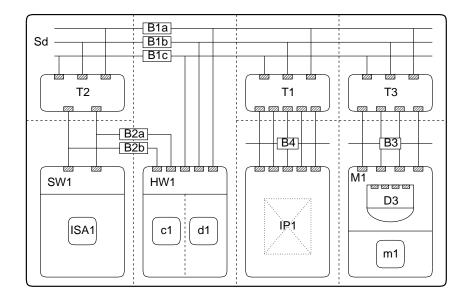

| Architecture model                               | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

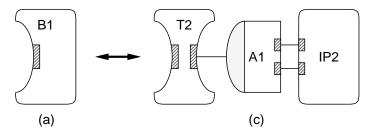

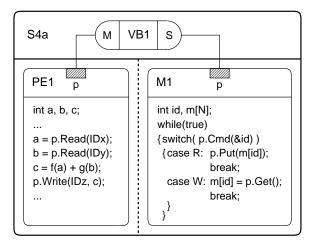

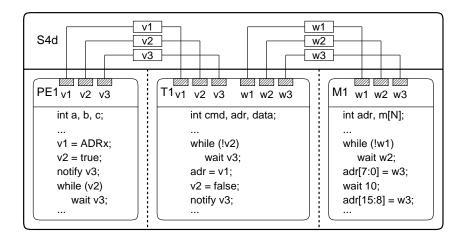

| Design example S4 before communication synthesis | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

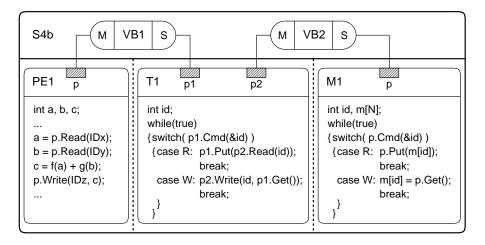

| Design example S4 after transducer insertion     | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

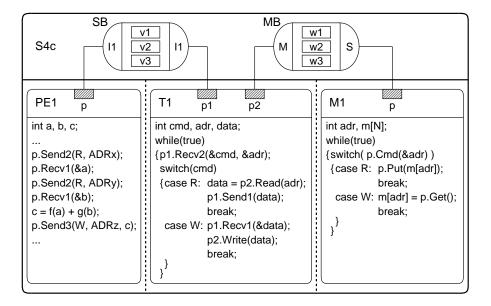

| Design example S4 after protocol insertion       | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Design example S4 after protocol inlining        | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

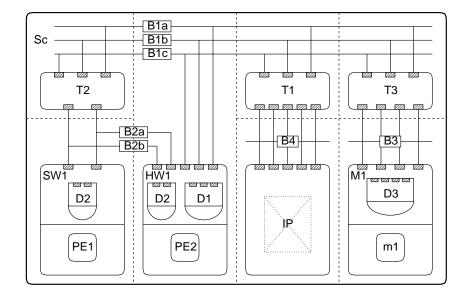

| Communication model                              | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Implementation model                             | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

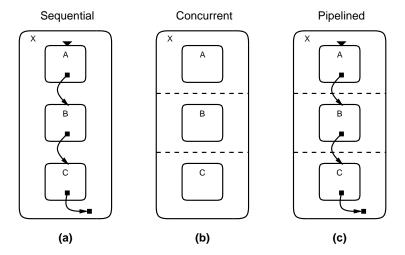

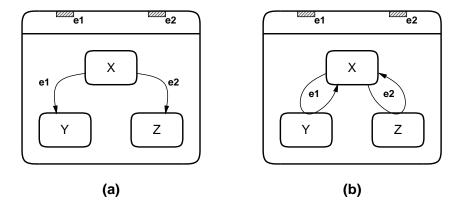

| •                                                | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                  | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

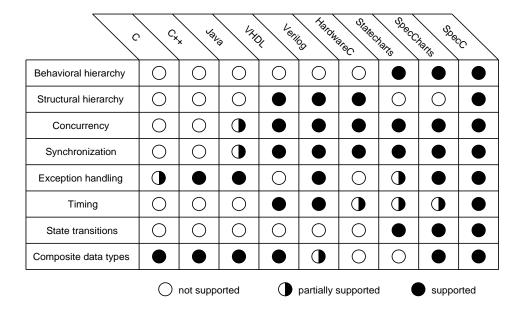

|                                                  | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

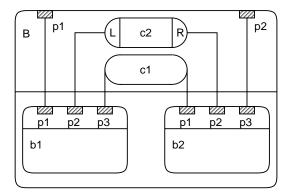

| *                                                | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

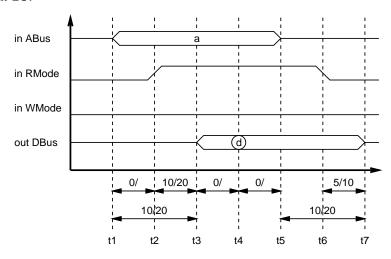

| Timing diagram example                           | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

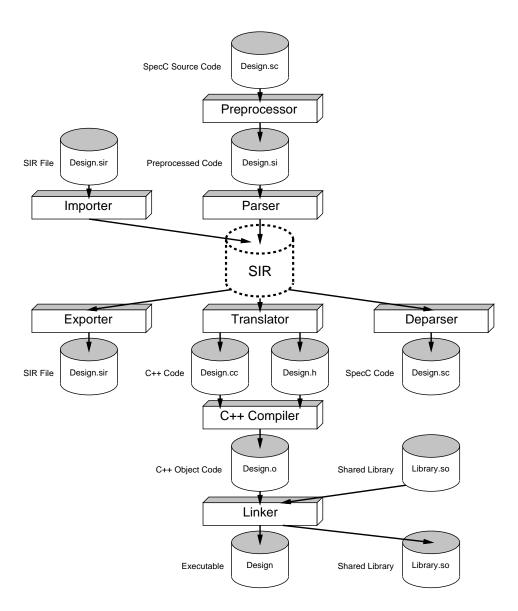

| The SpecC design environment                     | 08                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

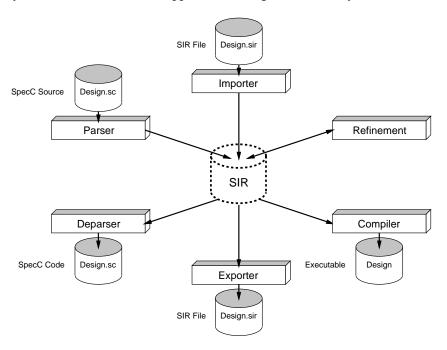

| Design representation with the SIR               | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

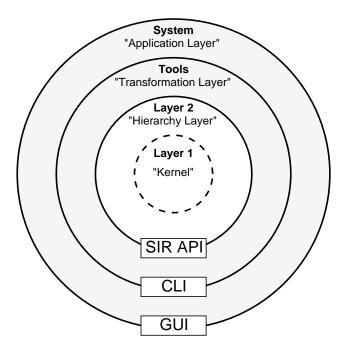

| SIR Application Programming Interface            | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

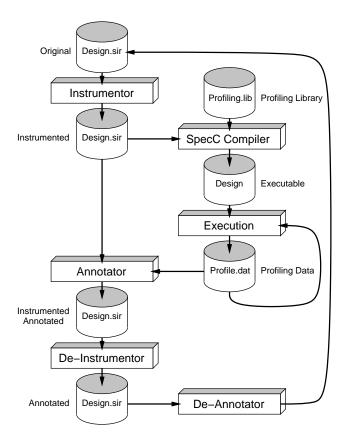

| Program flow of the SpecC profiling tools        | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Program flow of the SpecC compiler               | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

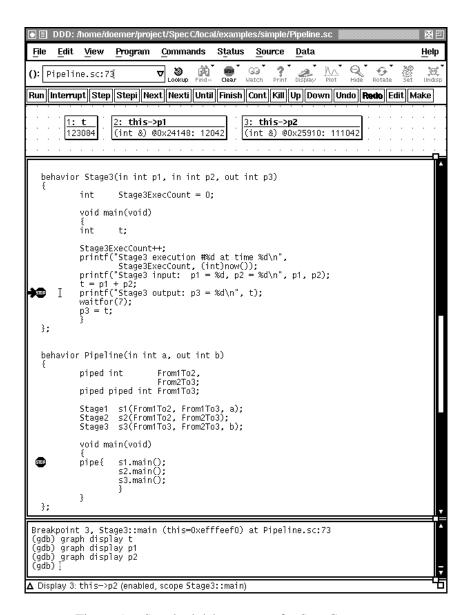

| Standard debugger use for SpecC programs         | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

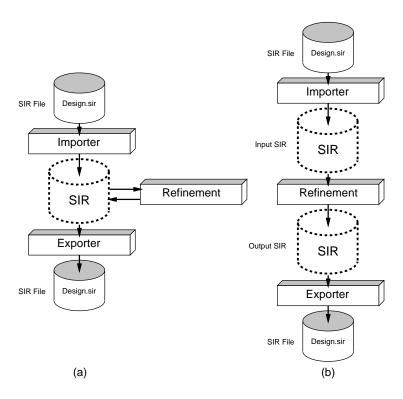

| Program flow of SpecC refinement tools           | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

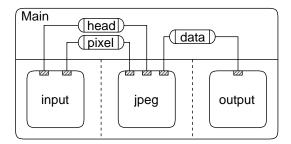

| JPEG encoder with test bench                     | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Generic SIR design tree of level 1 classes       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Generic SIR design tree of level 2 classes       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                  | Design example S4 before communication synthesis Design example S4 after transducer insertion Design example S4 after protocol insertion Design example S4 after protocol insertion Design example S4 after protocol inlining Communication model Implementation model  Behavioral hierarchy Exception handling Comparison of language features Basic structure of a SpecC model Timing diagram example  The SpecC design environment Design representation with the SIR SIR Application Programming Interface 1 Program flow of the SpecC profiling tools 1 Program flow of the SpecC compiler 1 Standard debugger use for SpecC programs 1 Program flow of SpecC refinement tools 1 IPEG encoder with test bench 1 |

## **List of Tables**

| 1.1 | System-level design projects in academia              |

|-----|-------------------------------------------------------|

| 1.2 | System-level design projects in industry              |

| 5.1 | Source components of the SpecC release 2.0.4          |

| 5.2 | Development and implementation of the profiling tools |

| 6.1 | RT level IP examples                                  |

| 6.2 | System level IP examples                              |

| B.1 | SpecC tutorial examples                               |

| B.2 | Library example                                       |

| B.3 | Composition of IP library components                  |

| B.4 | Communication examples                                |

| B.5 | Controller examples                                   |

| B.6 | JPEG encoder example                                  |

| B.7 | GSM vocoder example                                   |

xvi LIST OF TABLES

## **Chapter 1**

### Introduction

The semiconductor roadmap [SIA97], published by the Semiconductor Industry Association (SIA), estimates the design complexity for digital systems to continue to increase according to Moore's law [Ham99]. Applied to the design of embedded systems, Moore's law estimates the number of transistors on a chip to double every 18 months. The exponential growth of chip capacity is based on the continuing decrease in geometry size and increase in chip density.

In the next years, deep sub-micron design, dealing with process technologies of  $0.18\mu m$  and below, will allow to integrate 10ths of millions of logic transistors on one chip. This makes it possible to implement complex embedded systems entirely on a single chip. *System-on-Chip* (SOC) designs will integrate system components including processor cores, memories and special-purpose custom logic blocks into a complete system fitting on a single die.

SOC design is desirable especially for multi-media applications and portable devices where embedded systems save space, power and cost. In contrast to traditional ASIC design, which implements one sub-system in application-specific hardware, SOC design consists of the integration and implementation of special-purpose, complex components which are interacting with each other. Typically, a SOC includes one or more microprocessors, several peripheral units, memory blocks, and application-specific logic portions interconnected by on-chip busses.

While the availability of a huge chip capacity enables SOC designs, it, at the same time, significantly raises the complexity of these systems. The increased complexity requires substantially more effort, more efficient tools and new methodologies for building such embedded systems. In fact, the complexity of SOC design is beyond the size that currently established electronic design automation (EDA) tools and methodologies can handle.

The SIA roadmap shows that a *productivity gap* exists between the available chip capacity and the current design capabilities. While the chip capacity grows by 58% per year

(according to Moore's law), the support provided by computer-aided design (CAD) tools is estimated to increase by only 21% each year [SIA97]. If this growing gap cannot be overcome, it will result in under-utilization of the available chip capacity and thus unnecessarily increase the cost of embedded systems.

In the past, automated hardware *synthesis* was used to bridge the productivity gap. Logic synthesis and recently behavioral synthesis, also known as high-level synthesis (HLS) [GDW<sup>+</sup>91], supported designers in order to increase their productivity. Unfortunately, the help of hardware synthesis is not sufficient for SOC design, since embedded systems require more and more software content.

It should be clear that an increase in the design time for embedded systems is not an option in order to solve the productivity problem. The *time-to-market* is critical for the success or failure of a product in the market. Thus, it is necessary to develop and manufacture the next-generation product (and its embedded system) as quickly as possible in order to promote "product-on-demand". Ignoring the market pressures, which require to offer better products with more features for less money in shorter periods of time, is not acceptable.

The threatening under-utilization of available chip capacity due to the productivity gap and the strong market pressures force the electronic industry to search for new design methodologies. More efficient EDA support is required in order to build successful SOC designs. This is the motivation for system-level design which is defined in the following section.

#### 1.1 System-level Design

System-level design (SLD) addresses the problem of the increased complexity of embedded systems by raising the level of abstraction. In contrast to behavioral synthesis, which deals with the implementation of algorithms in application-specific hardware (ASIC design), system-level design focuses on the problem of mapping an abstract specification model of an entire system onto a target architecture (SOC design). As mentioned earlier, a typical target architecture consists of a set of processor cores, memories, peripheral units, and custom hardware blocks. These system components are interconnected by on-chip busses whose implementation is part of system-level design as well.

The cost-effective implementation of complex embedded systems requires a high software (SW) content. Compared to the high cost of developing dedicated hardware (HW), a software implementation is inexpensive. In addition, software can easily be modified if requirements change or new features need to be added. However, a software implementation may not be possible due to performance constraints. It is one task of system-level design to trade-off an inexpensive and flexible software solution versus a high-speed hardware implementation. Therefore, system-level design is also referred to as HW/SW codesign.

Codesign is defined as the design of systems involving both hardware and software.

The main task of codesign is the *partitioning* of a single system specification into hardware and software parts. Then, depending on whether a specific component is to be implemented in software or hardware, standard software technologies and established hardware design methods, respectively, are used for the final implementation of the component.

In general, any system consists of parts from different domains. Therefore, system design often is defined as to also include the mechanical domain in addition to the domain of electronics (see for example [CHM<sup>+</sup>99] and [Sch99]). The inclusion of mechanical aspects extends the coverage of the system model compared to the real system. It also allows tradeoffs to be made between mechanical versus electronic implementation of certain features.

On the other hand, these orthogonal domains are quite independent in most cases and thus can be treated separately. This separation significantly simplifies the design tasks as well. Hence, in this work, system design is considered exclusively within the domain of electronics.

Furthermore, some system-level design environments explicitly support the specification and use of analog and mixed signals. While this is useful for sub-systems, for example in the telecommunication area, the majority of embedded systems is specified completely digital. Also, the decision whether a signal is implemented as either analog or digital, can be viewed as an implementation issue that is resolved later in the design flow by back end tools. Within this work, system-level design targets on the design of digital systems [Gaj97], including hardware and software parts.

The system design flow usually starts from a formal, abstract specification of the intended design. After the specification has been validated for functional correctness, it is refined by a sequence of refinement tasks which eventually map the initial specification onto a selected target architecture. Section 1.1.4 discusses in detail the steps in a typical system design process including architecture selection, partitioning, scheduling and communication synthesis.

A very important issue in system-level design is the reuse of predesigned, complex components, often referred to as *Intellectual Property* (IP). In fact, the reuse of IP is the main key to cope with the complexity involved with SOC design. In contrast to redesigning a system completely from scratch, the use and integration of complex components, which are predesigned (possibly by somebody else) and well-tested, drastically reduces the design complexity. Thus, reuse of IP saves a great amount of design and testing time and, hence, allows a shorter time-to-market.

While the idea of IP reuse promises great benefits for system design, there are also problems to be solved. In order to allow easy and seamless integration in a new system, IP components need to be portable to different technologies and must provide standard or flexible interfaces. Good documentation about the IPs functionality, its requirements with respect to the environment, and its performance and other metrics are required as well.

The reuse of IP must become an integral part in the system design methodology. The selection, easy insertion and replacement of IP components ("plug-and-play") in the system

must be directly supported by the design models, the tools and the languages being used throughout the design process. These and other issues involved with the reuse of IP are addressed in more detail in Section 1.1.5.

#### 1.1.1 Levels of abstraction

In computer science, a well-known solution for dealing with complexity is to exploit hierarchy and to move to higher levels of abstraction. This effectively reduces the complexity in terms of the number of objects to be handled at one time.

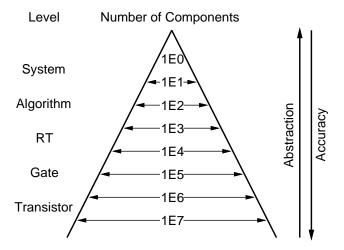

Figure 1.1: Abstraction versus complexity

Figure 1.1 illustrates this for digital systems. An embedded system, which at the lowest level consists of 10ths of millions of transistors, typically reduces to only thousands of components at the register-transfer level (RTL). Furthermore, RTL components are grouped together at the algorithm level. Finally, at the highest, the so-called system level, the one system is composed of only few components which include microprocessors, special-purpose hardware, memories and busses. From Figure 1.1, it is obvious that a complex embedded system is easier to deal with at the abstract system level than at the detailed gate or transistor level.

The level of abstraction is a trade-off with the level of *accuracy*. A high abstraction level implies low accuracy, and vice versa. The design process of a new system usually starts from a highly abstract specification model and ends with a highly accurate implementation model which reflects the real system with all its details.

The advantage of such a top-down approach is that all necessary design decisions can be made at an abstraction level where all irrelevant details are left out in the model. This allows the design tasks to work with a system model with minimum complexity.

The concepts of abstraction and hierarchy are closely related. In digital systems, *hierarchy* is inherent in the structure of a system. Every system is composed of a set of components, and each component is a (sub-) system that, again, is composed of (sub-) components. In other words, the terms *system* and *component* are recursively defined.

In order to break the recursion in this definition and to clearly identify the system and its components, it is necessary to name the current *abstraction level*. The abstraction level defines the type of the components used and, thus, also determines the system. For example, at the gate level, the components are logic gates and the system is the composition of such gates. One level below, at the transistor level, a single gate can represent an entire system that is composed of a set of transistors.

It should be pointed out that the term *system*, in general, refers to different things in different contexts. For example, a modern aircraft can be viewed as one single system or as a collection of thousands of systems. Within this work, unless stated otherwise, the term system refers to a digital, embedded system which can be implemented by use of application-specific hardware and software running on one or multiple processors.

Please note that this definition of a system is consistent with the term system-on-chip. It is also well-defined with respect to the abstraction level for SOC design, the system level. A precise definition of system-level design will be given in the following section by use of the Y-Chart.

#### 1.1.2 The Y-Chart

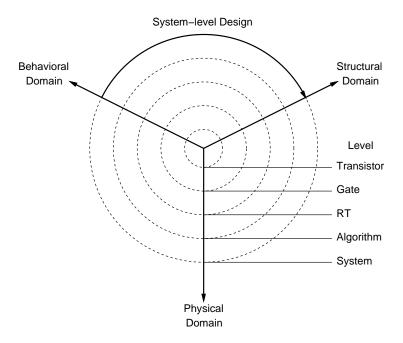

The Y-Chart [GK83], shown in Figure 1.2, is a conceptual framework which coordinates abstraction levels in different domains. This can be used to compare and classify different design tools and design methodologies.

The Y-Chart distinguishes three *domains* represented by three axes. A typical design process starts from the behavioral domain which specifies the pure behavior of the system without any implementation details, for example in form of program functions or mathematical equations. The design is then mapped onto an architecture in the structural domain. The structural architecture is composed of components, for example logic gates or RT components, depending on the level of abstraction. Finally, an implementation of the design is manufactured in the physical domain.

The level of abstraction, as introduced in Section 1.1.1, is orthogonal to the domains. Starting from the center of the chart, the abstraction level, indicated by the dashed, concentric circles, increases from the transistor level up to the system level.

The Y-Chart allows to illustrate design flows and design tasks as paths on the chart. For example, a complete system design flow starts on the behavioral axis at the system level. After step-wise refinement towards the center of the chart and mapping onto a structural and physical implementation, it finally ends on the physical axis at the transistor level.

On the Y-Chart, synthesis is represented by an arc from the behavioral to the structural

Figure 1.2: System-level design in the Y-Chart

axis. The definition of system-level design is indicated by the arrow in Figure 1.2. The task of system-level design is to synthesize a structural system architecture from a behavioral system specification.

As another example, high-level synthesis (HLS) is represented by an arc from the behavioral to the structural axis on the RT level.

Furthermore, the tasks of refinement and optimization can be demonstrated on the Y-Chart as well. *Refinement* is represented by an arrow on the behavioral axis from a high to a lower abstraction level. On the other hand, *optimization* can be represented as an arrow at any point in the chart which points back to its starting point. Thus, such optimization is a task that is performed in-place and can occur at any level in any domain.

Recently, the Rugby model [JKH99] was proposed as a new conceptual framework targeted to represent codesign tasks. In contrast to the Y-Chart, the Rugby model explicitly separates software and hardware design. Furthermore, the Rugby model distinguishes five orthogonal dimensions, namely time, data, computation, communication and transformation. As such, the Rugby model is much more complex and not as abstract as the Y-Chart<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>The "beauty" of the Y-Chart lies in its simplicity.

#### 1.1.3 Models of computation

In order to design an embedded system, a formal model of the system is needed. This section lists the models of computation which are commonly used in system-level design. For an in-depth discussion of these models, please refer to other sources in the literature. Good overviews, including detailed comparisons of the models, can be found in [GVN<sup>+</sup>94, GZD97c] or [LS96, LSS99], for example.

Models of computation can be classified into language oriented and architecture oriented models. Among the language oriented models, the *control flow graph* (CFG) represents the control flow of a program (for example, if-then-else and loop statements) in form of a directed graph. A *data flow graph* (DFG) is a (typically acyclic) graph used, for example, to represent expression trees. CFG and DFG can be easily combined into a *control data flow graph* (CDFG), which is a CFG whose nodes contain DFGs. A CDFG is commonly used as an intermediate model for systems specified with imperative programming languages.

Architecture oriented models represent an abstraction of the target architecture for a system. The basis for these models is the *finite state machine* (FSM) model which is a popular model to describe control. A FSM consists of states and transitions between the states. The output of a FSM is either state-based (Moore-type FSM), or input-based<sup>2</sup> (Mealy-type FSM). A FSM model can be easily implemented in hardware as a controller consisting of a state register and a block of combinatorial logic.

The FSM model has several extensions. Combined with the DFG model representing computation, the *finite state machine with datapath* (FSMD) is a typical target model for behavioral synthesis. The implementation of a FSMD consists of a controller and a datapath. Very similar to the FSMD model is the *finite state machine with coprocessors* (FSMC) as defined in [JDK<sup>+</sup>97].

In order to represent complete systems consisting of several concurrent processing elements, more complex models are required. For example, the *codesign finite state machine* (CFSM) model, described in [CGH<sup>+</sup>93], can be used to represent a set of concurrent executing and communicating FSMs. Alternatively, hierarchy and concurrency can be explicitly added to the FSMD model. This results in the *hierarchical concurrent finite state machine* with datapath (HCFSMD) which allows to have sequential or concurrent sub-states in each state of the FSM.

Finally, programming language constructs can also be added. The *program state machine* (PSM) model, defined in [GVN<sup>+</sup>94], is a HCFSMD whose leaf states contain program statements. The PSM is a powerful computational model that is used, for example, as the underlying model of the SpecCharts language [GVN93].

Many other models exist with focus on different features. The model of communicat-

<sup>&</sup>lt;sup>2</sup>The output of a state-based FSM depends solely on the current state, whereas the output of a input-based FSM depends on the current state *and* the current input.

ing sequential processes (CSP), described in [Hoa85], emphasizes communication. The synchronous data flow (SDF) model is used in [LM87] to represent data flow intensive applications and digital signal processing. Petri nets, first described in [Pet62], are used in several variants and provide a well-defined, formal background for the static analysis of systems.

The model of computation used for embedded systems design should meet certain requirements and objectives. First, it should be *intuitive* to understand so that it is easy to specify the intended system with the model. Second, it must be *executable* in order to allow early system simulation. Furthermore, the model should be *verifiable*, in other words, it should provide support for formal verification. Finally, it must be *synthesizable* so that an implementation of the model can be obtained.

The models listed in this section achieve these goals more or less. It is not possible to decide which model of computation is best suited for the design of embedded systems. For the SpecC system, which is described later in this work, the PSM computational model was chosen. Since the PSM model is close to the target architecture, it simplifies the development of CAD tools. The model also is easy to understand and sufficient powerful for the large complexity of SOC design. The PSM model is directly supported by the SpecC language, the SpecC CAD tools, and the SpecC methodology.

#### 1.1.4 System design process

The system design process starts with a specification of the intended design at a high level of abstraction and ends with an implementation model that accurately describes the implemented system and its components. In order to obtain the implementation from the specification, a set of refinement tasks is applied to the system model. This section defines the necessary tasks in a typical system design process.

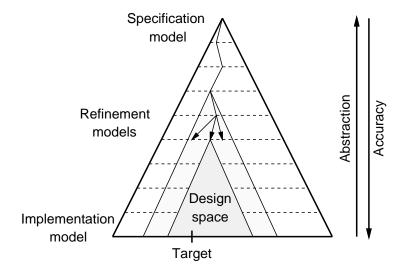

Figure 1.3 illustrates a top-down design process using step-wise *refinement*. Starting at the top of the pyramid, the specification model is transformed by a sequence of design tasks into refined models. At each stage, the available *design space*, as indicated by the shaded triangles in Figure 1.3, has to be explored. The goal of this design space exploration is to make a good design decision that will lead to an implementation model close to the target.

Each design decision affects the subsequent one in the way that the available design space shrinks. Obviously, it is important to choose the right model from the set of possible alternatives so that the target stays well inside the design space. Otherwise, if the decision is made in the wrong direction, the implementation will miss the target.

In general, each design task can be performed manually by designers or automatically by CAD tools. Also, both ways can be combined using semi-automatic refinement. Typically, it is up to the designer to make the design decision. Then automated tools are used to actually perform the tedious refinement with the design such that the decision made is reflected in the refined model.

Figure 1.3: Design process using step-wise refinement

It should be noted that the terms *specification* and *implementation* are relative to a particular design task or abstraction level. The implementation model generated by one task usually serves as the specification model for the next task.

#### 1.1.4.1 Specification

The specification of the intended system is the starting point for the design process. The specification must meet several requirements. First, it should be *complete*. In other words, it should cover the entire design with all its features, its functionality and its requirements. On the other hand, the specification should also be *abstract*. It should not include any premature implementation details.

Furthermore, it is required that the specification is captured unambiguously in a *formal* language so that it can be processed by automated tools. More specifically, the specification must be *executable* so that simulation can be used to validate the functionality of the system from the beginning.

The specification is the first formal and functional description of the system. It serves as an initial model against which all subsequent, refined models will be compared.

#### 1.1.4.2 Validation

In order to ensure the correctness of a system model, it has to be validated. *Validation* can be performed either statically by model analysis or dynamically by simulation.

As mentioned earlier, *simulation* requires the system model to be executable. Simulation validates the functionality of the system model in terms of the outputs generated for given input vectors. At different levels of accuracy, it can also be used to check the correctness of communication, synchronization, and timing.

Simulation usually is performed by a software simulator running on a host work station. However, system simulation in software is typically several orders of magnitude slower than the real system, in particular at low levels of abstraction. Hence, the system can only be validated for a short period of simulation time and a small set of test vectors. If this is not sufficient and more effort and higher cost are acceptable, *rapid prototyping* can be used to increase simulation speed by use of reprogrammable hardware, for example, field programmable gate arrays (FPGA) [Ros97].

It should be emphasized that simulation only validates a system model for the given test vectors and therefore, unless exhaustive simulation is performed, does not cover all possible cases. In contrast to validation, *verification* yields a 100% test coverage. Formal verification is a static analysis technique which can be used to prove certain properties of the system model. Formal verification requires a well-defined, formal model and, because of its complexity, can usually only be applied to very small systems.

In order to evaluate characteristics of a system which are not directly observable from the model, estimation techniques can be used. The task of *estimation* is to quickly determine critical quality metrics of the system such as performance, power consumption, size, cost, and others. Estimation can be performed either statically by analysis of the system model, or dynamically during simulation, for example, by use of profiling.

For estimation, there is a trade-off of accuracy versus time. The emphasis of estimation is on fast, rather than exact, system evaluation. Thus, the use of estimation enables the designer to make a reasonable design decision in short time. This is in contrast to a conservative approach which actually synthesizes all alternatives in order to make an optimal decision, as proposed in [Nie98], for example.

When finally a system has been manufactured, it must be tested for full functionality and no manufacturing defects. The high complexity of SOC designs requires that the chip is prepared for its *testing* already during the design process. Typically, built-in self-test (BIST) and other techniques are used to allow testing of chips with IP cores [ZMD99].

#### 1.1.4.3 Refinement

After the system specification is captured and validated, it is the task of *architecture explo*ration to allocate the system architecture, to partition the specification into hardware and software parts, and to map all parts of the design to the components in the architecture. During architecture exploration, estimation is used to determine the quality characteristics of the architecture under consideration. If the metric goals are not satisfied, the system is repartitioned or a different architecture or different components are selected. In the worst case, if no acceptable solution is found, the specification must be changed in terms of goals, constraints, or features.

It is the task of architecture *allocation* to determine the number and types of the processing elements (PE) and the connectivity for the system architecture. The components in the target architecture typically include processors, application-specific hardware, memories, peripheral units and IP cores. These components are interconnected by system or local busses. All components and busses are selected from the component library.

Most parts in a system specification can be implemented in either software or hardware. It is the task of HW/SW *partitioning* to trade off an inexpensive software solution versus a high-speed hardware implementation. Typically, only performance-critical parts of the system are implemented in hardware and all other parts are compiled into software to be executed on the allocated processors.

In general, *scheduling* has to be performed for the software parts of the system, since sequential processors can only execute one thread at a time. Scheduling determines the order of execution for the tasks assigned to a processor. Scheduling can be static or dynamic. A static schedule can be computed at design time if all constraints, including task execution times, delays, and dependencies, are known beforehand and do not change at run-time. Otherwise, dynamic scheduling must be used. In that case, the execution order for all tasks is determined dynamically at run-time, for example, by use of a real-time operating system (RTOS).

At the end of architecture exploration, each object in the specification is mapped to a particular hardware or software component. The quality of this *mapping* depends very much on the granularity of the objects. A coarse grained granularity, which, for example, considers entire processes as smallest, indivisible units, simplifies the refinement tasks since less objects need to be handled, but also limits the implementation options. On the other hand, a fine granularity enables more options allowing a possibly better implementation, but also increases the complexity and, thus, the refinement time.

After architecture exploration, *communication synthesis* must be performed. This includes the selection of communication protocols for the selected busses, hardware interface synthesis, and software driver generation. More specifically, accesses to data, which is assigned to a different PE, must be converted to remote procedure calls (RPC). Then, the RPCs can be implemented by use of the native bus protocol provided by the bus connecting the PEs. For hardware, interfaces need to be synthesized, and for software, device drivers must be generated. In case busses with different protocols need to be connected, protocol transducers must be inserted. In summary, the task of communication synthesis is to refine the abstract communication between the components in the architectural model into an implementation using the actual bus protocols.

The system-level design process is completed with the *back end*. The task of the back end is to make the refined system model available to established design methodologies for behavioral synthesis and standard software design. In order to allow a seamless integration,

it is important that the output generated by the back end can be used without modification as input to the subsequent tools.

For the software parts of the system, program code, for example C or assembly code, is generated so that standard compiler, assembler and linker tools can be used for the software implementation. If available, a retargetable compiler can generate code for all the allocated processors. Otherwise, a processor-specific tool set is needed for each type of processor in the system.

For the hardware parts, a synthesizable hardware description is generated, typically in VHDL or Verilog. This description can then be fed into high-level synthesis tools in order to implement the custom hardware.

#### 1.1.4.4 Methodology

In the previous sections, the typical tasks used in the system-level design process have been discussed. It must be emphasized that most of these tasks are interdependent. Moreover, there are cyclic dependencies. For example, the architecture allocation heavily influences the partitioning task, and vice versa. Also, timing constraints are input and output for both scheduling and communication synthesis. Because of these dependencies, there is no sequence of tasks which guarantees an optimum solution.

A heuristic solution to this problem uses an iterative approach. A set of tasks is repeated until an acceptable solution is found. The decision, whether a solution is "good enough" to proceed to the next task, is made by the system designer based on estimation data and his experience.

However, the design tasks must be supported by CAD tools and CAD tools place restrictions on the order they are executed. Thus, the system designer has to follow the guidelines under which the CAD tools were developed. Such a set of guidelines, which refine the abstract specification model into a detailed implementation model ready for manufacturing, is called a *methodology*.

A top-down methodology starts with a specification at the highest level of abstraction and moves down to lower levels while step-wise refining the model. With each step, the design model becomes a more accurate representation of the final implementation.

On the other hand, a bottom-up methodology starts from the lowest level, composing components together. These composed components then can be used in the next step to build even more complex components.

Both methodologies can be combined in order to achieve the best productivity. Usually, the top-down methodology is used until the system is decomposed into components which can be selected from the component library. The component library, on the other hand, is built using the bottom-up strategy.

With this combined approach, only the top-down phase affects the crucial *time-to-market* for the product, because the component library can be built beforehand. Thus, the

key to a short design time enabling "product-on-demand" is the use of IP components, which are predesigned and can be easily integrated in order to build the product. The system design methodology, which is based on the integration of IP components, is called *IP-centric* [GDZ99a, GDZ99b].

#### 1.1.5 Intellectual Property

As stated earlier, the reuse of IP is a key issue in SOC design. In fact, it is considered a paradigm shift that can be compared to the introduction of high-level synthesis a few years ago. This section elaborates on IP components and the benefits, problems and requirements with IP reuse.

#### 1.1.5.1 IP components

At the system level, predesigned components are frequently called IPs. IP components are independent processing elements, in other words, they have their own flow of control and interact with the other system components via the system busses. Unlike full-custom components, which are synthesized from scratch specifically for the application, IP components are selected from an IP library and are fixed or allow only limited customization.

Typical IP components include memories, processors, and industry standard circuits. Memory IPs, like RAM and ROM blocks, can usually be customized in their size, whereas processor IPs come typically as fixed cores. Processor IPs include embedded microcontrollers, general-purpose, and digital signal processors (DSP). Special-purpose IPs implement industry standards, for example, encoding and decoding algorithms like MPEG, JPEG, etc., or communication devices like PCI or VME bus interfaces.

IP components can be categorized into hard and soft IPs. *Hard IP* components are developed by use of a standard design process and are fully implemented in a specific technology. In particular, for hard IPs, there is a physical representation of the layout, for example, in form of a GDS-II file [KB98]. Since hard IPs are fully implemented, their performance characteristics and other metrics are very accurate and predictable. However, hard IPs are inflexible and limited to a specific target technology.

Soft IP components, in contrast, are very flexible IPs which come typically in form of synthesizable RTL code. Usually, soft IPs can be parameterized or are user-configurable in terms of data size, features, etc. Since soft IPs are synthesizable, they can be implemented in any target technology as well. However, the implementation metrics of soft IPs are not as predictable as for hard IPs, because the final implementation has yet to be synthesized.

IP components can also be classified into internal and external IPs. Since the process of developing the system is decoupled from the development of the IP components, these tasks can be performed independently by separate design teams in possibly different companies. *Internal IPs* are developed inside the same company which builds the system. Typical

internal IPs include legacy designs which can be reused from former products that have been proven to be successful.

The use of *external IP* is part of a new business model in the EDA industry. External IP components are developed and provided by IP providers outside the company building the system. While the system house, also called IP integrator, can focus on the problem of the system specification, integration and implementation, IP vendors develop and offer the required IP components. With this approach, the system house benefits from a large library of optimized, well-tested and well-documented components which are available when needed. The IP providers, on the other hand, can take advantage of their expertise in specialized design areas without the need to build and sell complete systems. This business model works well because, in many cases, it is cheaper for the system house to purchase an IP component as to invest time and money to develop it from scratch.

#### 1.1.5.2 IP reuse

The reuse of predesigned components is well-known in the EDA. For example, at the RT level, reuse includes the instantiation of components from the RTL library, such as registers, multipliers, arithmetic-logic units (ALU), etc. Similar to IPs, the components in a RTL library can be internal legacy components or external components supplied by another company.

The advantages of reuse are similar at the RT and the system level. At both levels, reuse of components drastically reduces the time and the cost of the design because the reused components are already designed, optimized, and tested. However, in order to exploit these benefits, several problems have to be overcome.

The main two problems involved with design reuse are component matching and component integration. First, the task of *matching* is to find a corresponding counterpart in the component library for a part of the design specification. A component can only be used in the implementation, if it matches the functionality and meets the constraints in the specification.

Then, the task of component *selection* is to choose one component from the set of matching components which best meets the design goals. Typical design goals are minimal cost or best performance.

Finally, when a suitable component is chosen, it must be integrated with the rest of the design. The task of *integration* is to ensure that the component is properly connected and controlled so that it cooperates with the other system components and works with the right data at the right time.

Component matching and integration are more difficult at the system level than at the RT level because of the higher level of abstraction. At the RT level, the behavioral and structural models of the components are close to the behavioral specification so that mapping and integration are usually straightforward.

For example, the behavioral model of an adder is simply an add operation indicated by a plus sign. The structural model is a component with two bit vector input ports and one bit vector output port. With these models, it is easy to map an addition onto an adder component by feeding the left and right arguments into the input ports and reading the result from the output port<sup>3</sup>.

At the system level, however, the tasks of component matching and component integration are not as straightforward because the behavioral and structural models of system components are much more complex.

The functionality of both, the system specification and the IP components, is described by *algorithms* rather than primitive arithmetic operations. Hence, IP matching essentially has to deal with the comparison of algorithms. Whether two algorithms match, however, is undecidable in the general case. Therefore, IP matching requires special handling by the tools<sup>4</sup> or the help of the designer.

The integration of IPs includes similar problems. Instead through plain ports, IP components usually communicate via non-trivial interfaces by use of possibly complex communication protocols. Hence, IP integration typically requires interface synthesis and protocol translation to be performed.