### **Overview**

### • Electronic System-Level (ESL) design tools

- Many that provide single hardware unit only (see HW design tools)

- > True system-level design across hardware and software boundaries

### • System-level design flow

- Frontend

- Application & architecture mapping

- Design space exploration (DSE)

- > System models (TLMs) for virtual prototyping

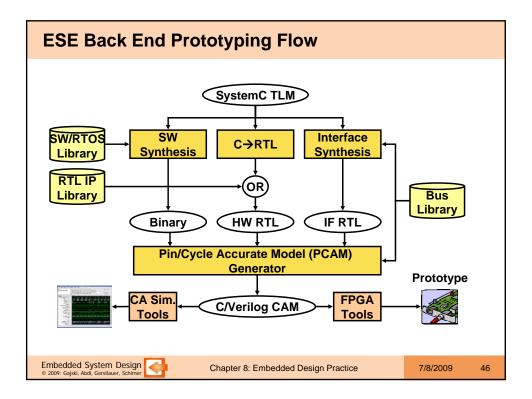

- Backend

- Hardware and software synthesis

- Commercial or proprietary (see SW & HW design tools)

- Physical system prototype or implementation

Commercial tools for modeling and simulation

Academic tools for synthesis and verification

Embedded System Design © 2009: Gajski, Abdi, Gerstlauer, Schirner

Chapter 8: Embedded Design Practice

7/8/2009 5

| Academic Tools                                                                                                                                                                                                                                                                                                                  |          |   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---|

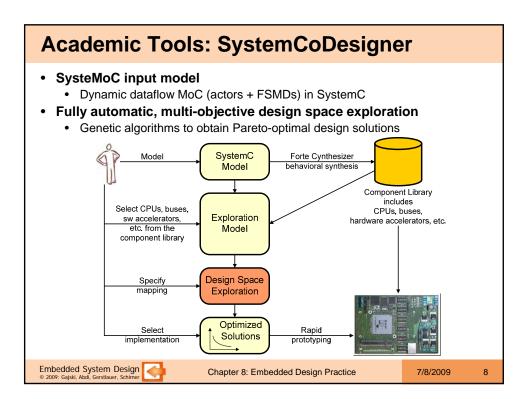

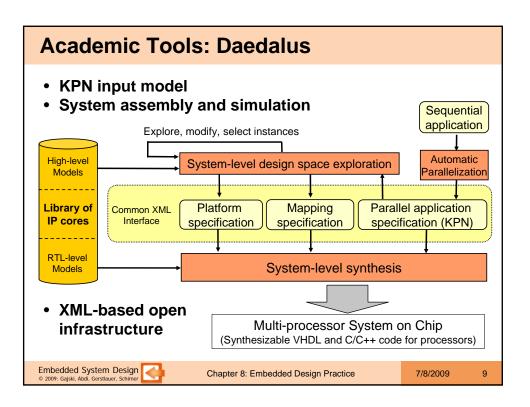

| <ul> <li>Metropolis <ul> <li>Platform-based design (PBD)</li> </ul> </li> <li>SystemCoDesigner <ul> <li>Dynamic dataflow MoC</li> <li>Automated design space exploration</li> </ul> </li> <li>Daedalus <ul> <li>KPN MoC for streaming, multi-media applications</li> </ul> </li> </ul>                                          |          |   |

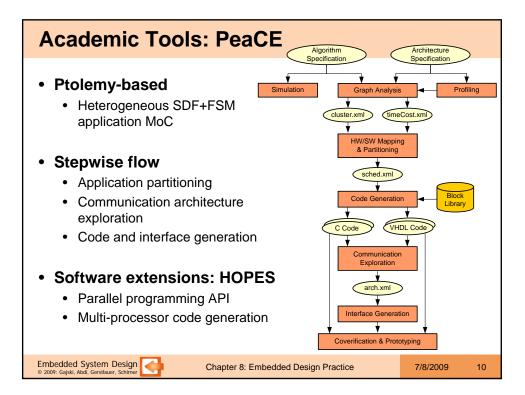

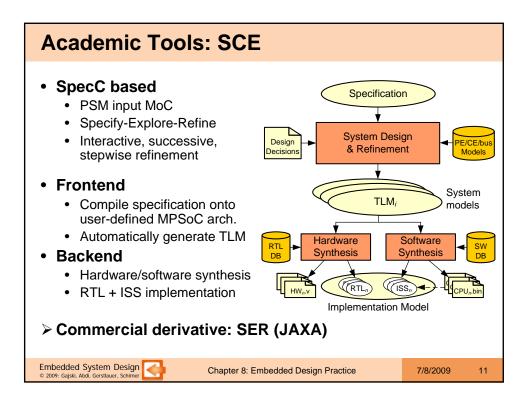

| <ul> <li>IP-based MPSoC assembly</li> <li>PeaCE <ul> <li>"Ptolemy extension as a Codesign Environment"</li> <li>Recent extensions for software development (HOPES</li> </ul> </li> <li>SCE <ul> <li>SpecC-based "System-on-Chip Environment"</li> <li>Successive, stepwise Specify-Explore-Refine method</li> </ul> </li> </ul> | ,        |   |

| Embedded System Design Chapter 8: Embedded Design Practice                                                                                                                                                                                                                                                                      | 7/8/2009 | 6 |

| Commercial Tools (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                              |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----|

| <ul> <li>• CoFluent</li> <li>SystemC-based modeling and simulation <ul> <li>Networks of timed processes</li> <li>Communication through queues, events, variables</li> </ul> </li> <li>• Early, high-level interactive design space exploration <ul> <li>Graphical application, architecture and mapping capture</li> <li>Fast TLM simulation with estimated timing</li> </ul> </li> <li>• Space Codesign <ul> <li>Graphical application, architecture and mapping capture</li> <li>Process network with message-passing or shared-memory</li> <li>SystemC TLM simulation <ul> <li>Annotated, host-compiled or cycle-accurate ISS models</li> </ul> </li> <li>• FPGA-based prototyping <ul> <li>Cross-compilation and third-party hardware synthesis (Fermion</li> </ul> </li> </ul></li></ul> | re (Eclipse)<br>ory channels |    |

| Embedded System Design Chapter 8: Embedded Design Practice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7/8/2009                     | 12 |

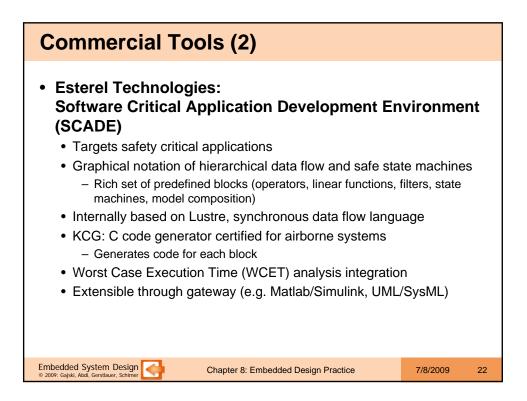

## **Commercial Tools (2)**

### CoWare

- Virtual system platforms

- SystemC TLM capture, modeling and simulation

- Extensive library of IP, processor and bus models

- Application-specific processor ISS models (LISAtek acquisition)

- Proprietary SystemC simulation framework

- Optimized SystemC kernel

- Graphical debugging, visualization and analysis capabilities

#### Soc Designer

- Proprietary, C++ based modeling and simulation

- Fast, statically scheduled cycle-accurate simulation

- Special cycle-callable component models

### VaST and Virtutech

- Proprietary SW-centric virtual platform modeling and simulation

- Fast, cycle-approximate binary translated or compiled ISS + peripherals

Embedded System Design © 2009: Gajski, Abdi, Gerstlauer, Schirner

Chapter 8: Embedded Design Practice

7/8/2009 13

| Overview                                                                                       |          |    |

|------------------------------------------------------------------------------------------------|----------|----|

| Tight connection to underlying HW     – Processor, custom hardware, physical process integrati | on       |    |

| <ul> <li>Requires:         <ul> <li>Processor-specific code generation</li></ul></li></ul>     | uite     |    |

| Embedded System Design Chapter 8: Embedded Design Practice                                     | 7/8/2009 | 16 |

# Academic Tools (1)

### POLIS

- HW/SW co-design environment

- Input: Esterel or graphical FSM notation

- Centered around Codesign Finite State Machine (CFSM)

Locally synchronous, globally asynchronous

- · Formalism for verification, co-simulation, partitioning and synthesis

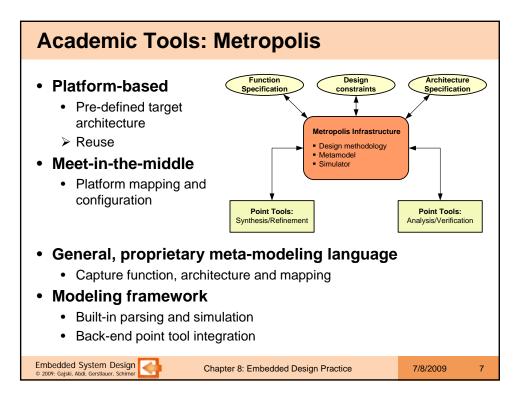

### METROPOLIS

- Platform based design

- Meta-model; supports many MoCs

- Separate function, architecture and MoC into separate inputs

- Co-simulation heterogeneous PEs with different MoCs

Embedded System Design 2009: Gajski, Abdi, Gerstlauer, Schirner

Chapter 8: Embedded Design Practice

7/8/2009 17

| Outlook                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Status <ul> <li>Vendor specific solutions / domain specific solutions <ul> <li>E.g. processor, FPGA fabric or OS vendors</li> <li>Automotive, signal processing</li> </ul> </li> <li>More attention to reusable and scalable implementations</li> <li>Component-based approaches (e.g. AUTOSAR)</li> <li>Integrated documentation / design (e.g. UML, SysML)</li> </ul> </li> <li>Platform complexities increase <ul> <li>Many-core platforms, heterogeneity</li> <li>Manual implementation increasingly inefficient</li> </ul> </li> <li>Increasing focus on generation / synthesis</li> <li>Develop systems as composition of algorithms</li> <li>Automatic generation of embedded software</li> <li>Focus on essential function aspects instead of implementation detail</li> </ul> |

| Embedded System Design e 2009: Gajki, Abdi, Gerstauer, Schimer 7/8/2009 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Commercial Tools (1)                                                                                                                                                                                |             |      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|

| <ul> <li>Catapult Synthesis</li> <li>C++-to-RTL</li> <li>Block architecture for different C functions with complementation</li> </ul>                                                               | munication  |      |

| <ul> <li>channels between</li> <li>User directives for interface and memory mappings<br/>and pipelining, HW hierarchy, block communication<br/>allocation, latency and cycle constraints</li> </ul> | •           | ling |

| Cynthesizer                                                                                                                                                                                         |             |      |

| <ul> <li>Pin- and protocol-accurate SystemC as input</li> </ul>                                                                                                                                     |             |      |

| <ul> <li>Hybrid scheduling approach for protocol and compu-<br/>sections</li> </ul>                                                                                                                 | Itation     |      |

| <ul> <li>Gate-level library generated for estimation</li> </ul>                                                                                                                                     |             |      |

| <ul> <li>Custom datapath components are created from use<br/>C++ code</li> </ul>                                                                                                                    | r indicated |      |

| Embedded System Design                                                                                                                                                                              | 7/8/2009    | 32   |

# **Commercial Tools (2)**

#### • PICO

- C-to-RTL mapping under performance constraints (throughput, cycletime) for data streaming applications

- Complex application engines for system platforms

- Compile-time configurable architecture template based on Khan-processnetwork model

- Advanced parallelizing compiler

#### CyberWorkBench (CWB)

- C-based HLS and verification tool ("All-in-C" approach)

- Legacy RTL blocks as black boxes

- · Cycle-accurate simulation model generated for validation

- Input C code verified through assertions

- Bluespec

- An alternative to loop-and-array paradigm

- Bluespec System Verilog (BSV) language specifies concurrent system behavior as a collection of rewrite rules

Chapter 8: Embedded Design Practice

7/8/2009

33

• BSV is translated into Verilog or SystemC RTL by Bluespec Compiler

Embedded System Design © 2009: Gajski, Abdi, Gerstlauer, Schirner

### **Outlook** Status Designers acceptance of C-to-RTL concepts Increasing supply of HLS tools • C/C++ is favored as input description Pre-synthesis optimization for better results Open Issues Synthesized architecture needs additional features - Control and datapath pipelining - Programmable controllers - Architecture cells or custom-processor templates - Retargetable compilers Platform generation and synthesis - Merging components into platform and mapping application Interfacing synthesized components (Interface cells) Embedded System Design Chapter 8: Embedded Design Practice 7/8/2009 34

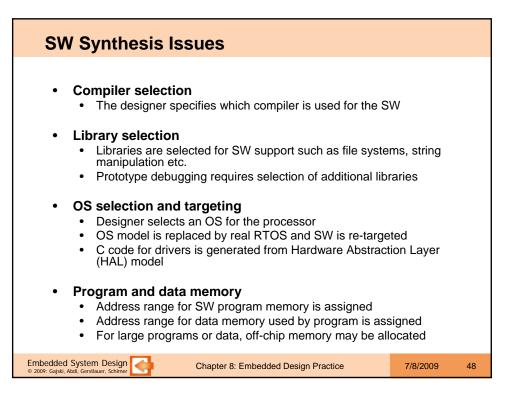

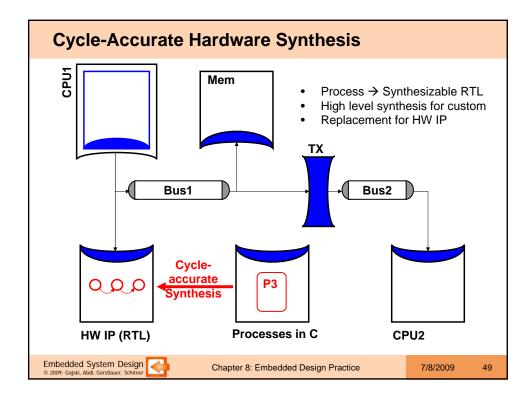

| HW Synthesis Issues                                                                                                                                                                                      |             |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----|

| <ul> <li>IP insertion</li> <li>C model of HW is replaced with pre-designed RTL IP, i</li> <li>RTL synthesis tool selection</li> </ul>                                                                    | f available |    |

| <ul> <li>RTL synthesis tool must be selected for custom HW de</li> <li>C code generation</li> <li>C code for input to RTL synthesis tool is generated</li> </ul>                                         | sign        |    |

| <ul> <li>Synthesis directives</li> <li>RTL architecture and clock cycle time is selected</li> <li>UBC calls are treated as single cycle operations, to be expanded during interface synthesis</li> </ul> | later       |    |

| <ul> <li>HDL generation</li> <li>RTL synthesis result in cycle accurate synthesizable Ve code</li> </ul>                                                                                                 | erilog      |    |

| Embedded System Design Chapter 8: Embedded Design Practice                                                                                                                                               | 7/8/2009    | 50 |

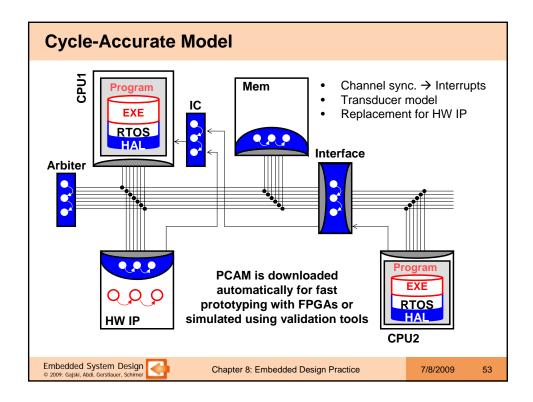

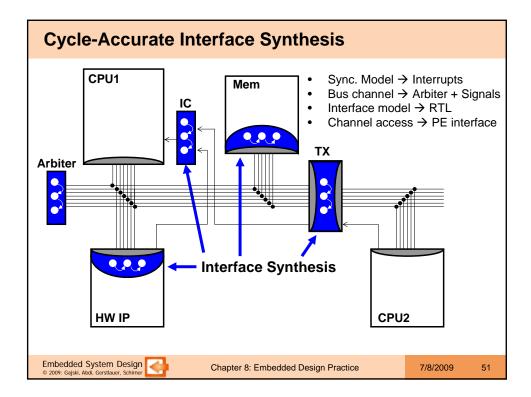

| Interface Synthesis Issues                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Synchronization</li> <li>UBC has unique flag for each pair of communicating processes</li> <li>Flag access is implemented as polling or CPU interrupt</li> </ul>               |

| <ul> <li>Arbitration</li> <li>Selected from library or synthesized to RTL based on policy</li> </ul>                                                                                    |

| <ul> <li>Bridge</li> <li>Selected from library or synthesized using bridge generator</li> </ul>                                                                                         |

| <ul> <li>Addressing</li> <li>All channels are assigned unique bus addresses</li> </ul>                                                                                                  |

| <ul> <li>SW communication synthesis</li> <li>Bus channel function calls are replaced by C drivers</li> </ul>                                                                            |

| <ul> <li>HW communication synthesis</li> <li>DMA controller in RTL is created for each custom HW component</li> <li>Send/Recv operations are replaced by DMA transfer states</li> </ul> |

| Embedded System Design<br>• 2009: Gajski, Abdi, Gerstlauer, Schimer Chapter 8: Embedded Design Practice 7/8/2009 52                                                                     |