# The Design of a USB Device Controller IYOYOYO

Tomoaki Kouyama†

Hibiki Nano††

Chiaki Kon†

Naohiko Shimizu††

†Graduate School of Engineering, Tokai University ††Dept. Communications Engineering, Tokai University Hiratsuka, Kanagawa 259-1292

E-mail: {2aepm025, 9jet1239, 1aepm024, nshimizu}@keyaki.cc.u-tokai.ac.jp

#### Abstract—

USB(Universal Serial Bus) is a very popular interface in recent computer systems. USB replaces legacy interface, such as serial port, pararel port, and so on. We designed USB device controller IYOYOYO, and USB Gamepad device with it. This Gamepad device was implemented on an FPGA, with IYOYOYO.

#### I. DESIGN POLICY

IYOYOYO supports Low Speed mode, which is defined in *Universal serial bus specification revision 1.1*[1].

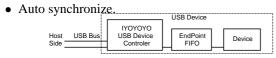

IYOYOYO pursues USB protocol. The device which uses IYOYOYO can transfer data to EndPoint without knowledge of USB. A USB device is configured as Figure.I. We used **SFL**[8] for the description language. We designed a USB Gamepad device with IYOYOYO.

#### II. USB DEVICE CONTROLLER IYOYOYO

Many of existing USB controllers pursue up to Transfer level. These controllers can not handle non-supported Transfers.

We intended IYOYOYO USB Controller to pursue only packet level. All the high level jobs are left for firmware. Hence, IYOYOYO can process any type of Transfers.

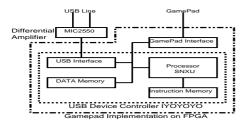

Figure.II is a block diagram of USB device with IYOYOYO. IYOYOYO consists of USB interface module and MPU module SNXU. The interface module is memory mapped in the MPU's address space. MIC2550[7] is a level converter between differential bus signal and digital signal.

Table.I show the protocol stack and the role of module.

#### A. USB Interface

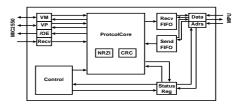

Figure.III is the block diagram of USB Interface. It pursues subordinate layer protocols.

USB Interface provides following services.

Fig. I. The configuration of USB Device with IYOYOYO

Fig. II. The block diagram of USB gamepad device with IYOYOYO

- NRZI Encoding and Decoding.

- 16bit CRC Encode, 16bit 5bit CRC Check.

- Stuff bit detect and remove, insert.

- Detect EOP(End Of Packet) Bus state.

- Detect Reset Bus state, and system Reset.

- Auto device address check. Auto reject illegal device address token packet.

- Auto split and byte align packet elements. Endpoint, Packet ID, Address, CRC, DATA.

- Receive Packet ID to PID register. Send Packet ID from PID register.

### i. Packet Receive Operation

On sync pattern of a packet, the interface makes the synchronization of the device. It decodes NRZI and removes stuff bits of receive packets. When it receives packet ID, it sets the ID to packet ID register.

If Packet ID designates a DATA, the interface sets next data to Recv FIFO. And it checks the DATA by CRC16. If packet ID designates a TOKEN, next 7bits is address, and 4bits is endpoint, and 5bits is CRC code, respectively. The interface also checks device address in the packet. The interface extends the received endpoint to 8bit and set it into Recv FIFO. And, it checks the data by CRC5 and sets status flag.

TABLE I USB Protocol stack

| Protocol          | Contents                      | Cover Modules     |

|-------------------|-------------------------------|-------------------|

| Application       | HID GamePad                   |                   |

| Transfer Level    | Control, Interrupt            | SNXU, Firmware    |

| Transaction Level | IN, OUT, SETUP                |                   |

| Packet Level      | Packet distinction, analysis. |                   |

|                   | Token, Data, Handshake        |                   |

| Error check       | CRC5, CRC16                   | USB Interface     |

| Signal Encode     | NRZI, stuff bit, sync         |                   |

| Electrical Level  | differential signal           | MIC2550 & Pull-up |

|                   |                               | resister          |

Fig. III. The block diagram of USB Interface module

Fig. IV. Detect Dialog on MS Windows

TABLE II USB INTERFACE REGISTER MAP

| Name          | Address | Type(from MPU) |

|---------------|---------|----------------|

| Recv FIFO     | 0x8000  | ReadOnly       |

| Recv STAT     | 0x8002  | ReadOnly       |

| Send FIFO     | 0x8003  | WriteOnly      |

| Send STAT     | 0x8006  | WriteOnly      |

| DeviceAddress | 0x8008  | WriteOnly      |

| Packet ID     | 0x8009  | ReadWrite      |

#### TABLE III USED MEMORY

| Memory Type | Used Word |

|-------------|-----------|

| Instruction | 242       |

| Data        | 300       |

#### TABLE IV SNXU SPECIFICATION

| 16Bit RISC like Harvard architecture Processor |                      |  |

|------------------------------------------------|----------------------|--|

| General Register 16Bit×4                       |                      |  |

| Non-Pipeline, Average Instruction Cycle 2clk   |                      |  |

| Instruction set                                | ADD AND SLT NOT SR   |  |

|                                                | LD ST LDA BZ BAL TAG |  |

Packet receive operation is terminated when it receives End of packet(EOP).

### ii. Packet Send Operation

MPU initiates the packet send operation. The interface sends SYNC pattern and packet ID with the send request from MPU. If also carries our stuff bit insertion and NRZI encoding. For HANDSHAKE packet, the interface send SYNC and packet ID. For DATA packet, it sends SYNC, packet ID, and the DATA. The interface adds 16bit CRC following the DATA. At the end of the packet, it sends EOP.

### B. MPU SNXU

Table.IV shows the specification of SNXU. SNXU is a RISC processor which have only 11 instructions.

We added a special instruction TAG for the USB interface. It read 1byte from Recv FIFO of USB interface. If the FIFO is empty, SNXU will wait for the arrival of the data in Recv FIFO.

## C. Firmware

The firmware uses TAG instruction for the packet data from FIFO. It uses Load(LD) instruction for Packet ID.

In Control Transfer, the device sends Descriptors or configuration data depending on the receiving data packet. Those operations use EndPoint 0.

In Interrupt Transfer, the device sends EndPoint data. End-Point is designated by the received TOKEN packet. Our USB device has EndPoint 1 for interrupt transfer. EndPoint1 is used for the GamePad data in the USB device.

Table.III shows the used memory words for the device. We use the internal memory of FPGA.

#### III. CONCLUSION

We designed a Low Speed HID Gamepad with IYOYOYO.

The Gamepad interface module has a memory mapped FIFO for the pad data. It detects Gamepad state change and pushes Pad state on FIFO.

We also designed firmware and descriptors(Device, Configuration, EndPoint, HID, Report, and String) compliant to USB specification 1.1[1].

Fig. V. Implemented USB Gamepad on FPGA Board

Fig. VI. USB Gamepad configuration packet log

#### TABLE V LOGIC SYNTHESIS SUMMARY

| Device                  | Gates(LE)       | Max Frequency |

|-------------------------|-----------------|---------------|

| ALTERA EP20K160EFC484-3 | 1645/6400 (25%) | 28.48MHz      |

| NEC cmos9               | 14747gates      | 44.62MHz      |

We used an ALTERA APEX 20KE, and Quartus II1.1[9] for fitting. Table.V shows the Logic Synthesis statistics. The picture of the board is shown in the Figure.V.

We successfully use our device as a Gamepad with the control panel and DirectX Games on MS-Windows. The packet log is shown in the Figure.VI, and the detecting dialog is shown in the Figure.IV.

IYOYOYO is a compact and flexible USB core. We will use it for many projects in our laboratory.

#### REFERENCES

- [1] USB ORG: Universal Serial Bus Specification Revision 1.1

- Triceps: The Design Method of USB Interface

- His Publisher, 1998.

- CO Publishing Co.,Ltd.

- TECHI Vol.8 The All of USB Hard & Soft Development His Publisher, 2001.

- Moroboshi Ramu: The Trial Development of USB Host System, Dos/v danyo His Publisher, 2001 C61.

- USB Acceleration Sensor Mouse

- http://www.yellowsoft.com/contents/usersamp/user5/

- USB Communication Programing Technique http://www.picfun.com/usbframe.html

- MICREL

- MIC2550 Universal Serial Bus Transceiver Specification

- Parthenon: http://www.kecl.ntt.co.jp/parthenon/

- ALTERA : http://www.altera.co.jp/