# **CMOS VCOs for Frequency Synthesis in Wireless**

**Biotelemetry**

Rafael J. Betancourt-Zamora Stanford University 420 Via Palou Mall, CIS-26 Stanford, CA 94305-4070 (650) 725-4565 betasoft@smirc.stanford.edu

# **1. ABSTRACT**

A new phase noise model was used to optimize a differential ring VCO for minimum power consumption. We compare the phase noise performance of three buffer stages using clamped, symmetric and cross-coupled loads, respectively. We propose a cross-coupled buffer topology that achieves lower phase noise by exploiting symmetry. Measured phase noise for a 1.2mW, 150MHz VCO fabricated in  $0.5\mu m$  CMOS is -103.9dBc/Hz at 500KHz offset, showing good agreement with the theory.

## 1.1 Keywords

Cmos, frequency synthesis, phase noise, ring oscillator, vco

# 2. INTRODUCTION

The most important parameters of an implanted biotelemetry system are size and power dissipation. A significant portion of the power budget for any implantable telemetry system is allocated to the generation of the RF carrier. Given the need for small, low-power wireless devices for biotelemetry, a low-power, integrated frequency synthesizer is required.

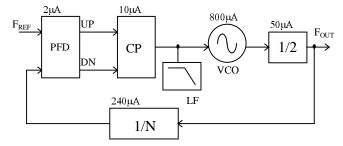

Figure 1 shows the block diagram and power budget for a CMOS PLL synthesizer used in microprocessor clock generation [1]. The major sources of power dissipation are the VCO (73%) and the frequency divider (22%). The VCO's power dissipation is determined by the frequency of operation and the phase noise performance required. In biotelemetry, low data rates and wide channel spacing relax the phase noise requirement, making phase noise at a 500KHz offset a valid measure.

#### 3. VCO DESIGN

Phase noise performance of a synthesizer is a function of the phase noise of the VCO. The Hajimiri phase noise model [2],

Thomas H. Lee Stanford University 420 Via Palou Mall, CIS-205 Stanford, CA 94305-4070 (650) 725-3725 tomlee@smirc.stanford.edu

Figure 1. Typical PLL frequency synthesizer power budget

[6] was used to minimize the power dissipation of the VCO.

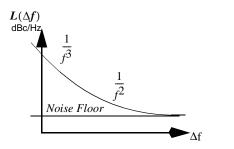

Phase noise in the  $1/f^2$  region is due to white device thermal noise (Figure 2). For a differential ring oscillator using short-channel devices, one may derive the following lower bound on the single-sideband phase noise in the  $1/f^2$  region:

$$L\{\Delta f\} = 10 \cdot \log\left\{\frac{18kT}{\pi^2 I_{DD}} \cdot \left(\frac{2.5}{E_C L_{EFF}} + 1\right) \cdot \left(\frac{f_o}{\Delta f}\right)^2\right\}, dBc/Hz \quad (1)$$

where  $I_{\text{DD}}$  is the tail current of a single stage,  $E_{\text{C}}$  is the critical field in silicon, and  $L_{\text{EFF}}$  is the gate length of the differential-pair devices.

Phase noise in the  $1/f^3$  region is due to device 1/f noise. It is usually assumed that the  $1/f^3$  corner frequency is the same as the 1/f corner of device noise. This is not true, as the  $1/f^3$  corner is actually given by:

$$f_{1/f^3} = f_{1/f} \cdot \left(\frac{c_o}{2\Gamma_{rms}}\right)^2 \tag{2}$$

where  $c_0$  is the DC Fourier coefficient and  $\Gamma_{rms}$  is the RMS value of  $\Gamma(x)$ , the impulse sensitivity function (ISF). The ISF accounts for the time-variant sensitivity of the oscillator to its noise sources. The upconversion of device 1/f noise occurs through  $c_0$ , the DC value of the ISF. However, the DC value of the ISF is governed by the symmetry properties of the single-ended output waveform. This model thus predicts the upconversion of 1/f device noise into close-in phase noise as a function of the symmetry of the output waveform.

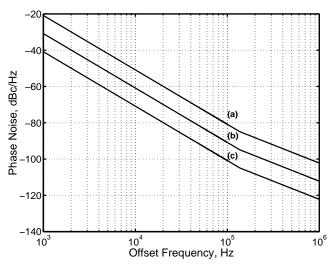

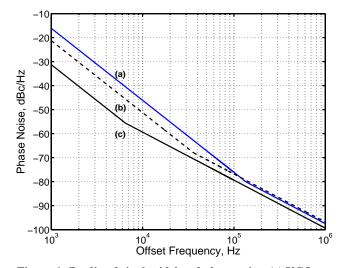

To start the design, we plotted a series of phase noise curves (Figure 3) for a typical 0.5µm CMOS process ( $f_{1/f}=3MHz$ ). We selected the 100µA curve, for a total current drain of 400µA at 200MHz for the VCO core.

Figure 2. Oscillator close-in phase noise due to upconversion of thermal and 1/f device noise

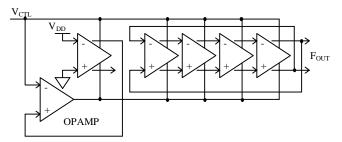

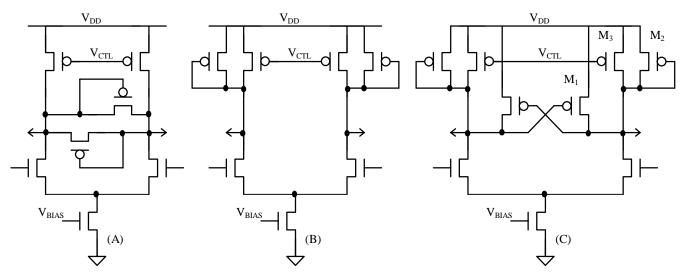

The VCO consists of a 4-stage ring oscillator (Figure 4) that uses differential buffer delay stages with replica-feedback biasing [3]. Frequency control is achieved by changing the biasing of the buffer stages which determines the delay through each cell. The layout of the ring oscillator is symmetrical and load balanced to avoid any skewing between the phases. Three ring oscillators were designed, each using a different load circuit for the delay buffer stage: VCO<sub>1</sub>-clamped load, VCO<sub>2</sub>-symmetric load, and VCO<sub>3</sub>cross-coupled load, respectively.

The clamped-load differential buffer (Figure 5a) used in VCO<sub>1</sub> has excellent noise and PSR characteristics [4]. The cross-coupled diode loads clamp the output swing making the buffer delay insensitive to common-mode noise. Symmetric load buffers (Figure 5b), as used in VCO<sub>2</sub>, also have very good supply noise rejection characteristics and have been used extensively in PLL and clock generator designs [5].

For the proposed cross-coupled load (Figure 5c) design of VCO<sub>3</sub>, we started with a symmetric load stage with no cross-coupling and swept the width of the cross-coupling devices while maintaining the total width (capacitance) of the loads constant. The maximum symmetry of the output waveform was observed when the widths of  $M_1$  and  $M_2$  were equal to half the width of  $M_3$ .

Figure 3. Lower bound on phase noise for ring oscillator at 200MHz for: (a)  $I_{DD}$ =10µA, (b)  $I_{DD}$ =100µA, (c)  $I_{DD}$ =1000µA

Figure 4. Differential ring oscillator VCO with replica bias

#### 4. SIMULATION AND MEASUREMENTS

To compare the three topologies, a more detailed noise analysis was performed. The predicted noise for a 4-stage oscillator is given by:

$$L\{\Delta f\} = 10 \cdot \log\left\{ \left( \frac{\Gamma_{rms}}{\pi V_{swing} C_{node} \Delta f} \right)^2 \cdot \frac{i_n^2}{\Delta f} \right\}, dBc/Hz$$

(3)

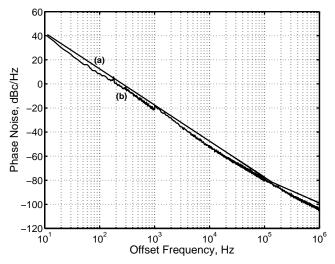

where  $i_n^2/\Delta f$  is the total noise contribution from all sources at the output node,  $C_{node}$  is the total capacitance at the output node, and  $V_{swing}$  is the voltage swing across  $C_{node}$ . Figure 6 shows the predicted phase noise for VCO<sub>1</sub>, VCO<sub>2</sub>, and VCO<sub>3</sub>. The  $1/f^2$  regions are within 2.6dB of each other as it is to be expected for similarly sized noise sources. The model also predicts lower phase noise in the  $1/f^3$  region for VCO<sub>3</sub> as it has better symmetry than the other two.

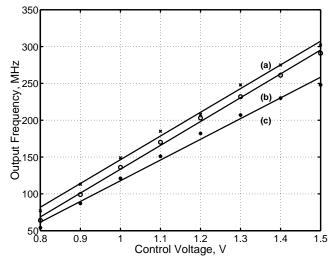

A test chip was fabricated through MOSIS using the HP  $0.5\mu$ m CMOS process. The VCO<sub>1</sub> voltage-to-frequency transfer characteristics was measured for different supply voltages (Figure 7). Test results for VCO<sub>1</sub> are shown in Figure 7 for operation at 150.9MHz, along with the phase noise predicted by the model. The phase noise was measured at -103.9dBc/Hz for a 500KHz offset which is very close to the predicted value of -103.2dBc/Hz (Figure 8). These results are well within the 2dB measurement accuracy of the RDL NTS-1000A instrument used.

## 5. CONCLUSION

To minimize power dissipation of the VCO, a design technique based on a new phase noise model was presented. We have demonstrated a 150MHz VCO fabricated in a standard CMOS 0.5 $\mu$ m process. Measurements of phase noise show good agreement with the theory. We also compared the phase noise performance of three differential buffer stages. We proposed a cross-coupled load buffer that achieves lower phase noise in the  $1/f^3$  region well below 500KHz by exploiting single-ended symmetry in the oscillator's waveform.

## 6. ACKNOWLEDGEMENTS

We wish to thank Ali Hajimiri, and Miguel Gabino-Perez for their assistance, and Rockwell Semiconductor for providing access to the NTS-1000A test set. This work was partially supported by NASA-Ames Research Center through a Training Grant No. NGT 2-52211.

Figure 5. Differential delay buffer cells: (a) VCO<sub>1</sub>, clamped-load; (b) VCO<sub>2</sub>, symmetric load; (c) VCO<sub>3</sub>, cross-coupled load

Figure 6. Predicted single-sideband phase noise: (a) VCO<sub>1</sub>, (b) VCO<sub>2</sub>, (c) VCO<sub>3</sub>

# 7. REFERENCES

- V. von Kaenel, D. Aebischer, C. Piguet, and E. Dijkstra. A 320MHz, 1.5mW @ 1.35 V CMOS PLL for microprocessor clock generation. IEEE JSSC 31, 11 (1996), 1715-1722.

- [2] A. Hajimiri and T.H. Lee. A General theory of phase noise in electrical oscillators. IEEE JSSC 33, 2 (1998), 179-194.

- [3] J. Maneatis and M. Horowitz. Precise delay generation using coupled oscillators. IEEE JSSC 28, 12 (1993), 1273-1282.

- [4] M. Horowitz, et al. PLL Design for a 500MB/s Interface. ISSCC Digest (1993), 160-161.

- [5] J. Maneatis. Low-Jitter and process-independent DLL and PLL based on self-biased techniques. ISSCC Digest (1996), 130-131, 430.

- [6] A. Hajimiri and T.H. Lee. Correction to "A General Theory of Phase Noise in Electrical Oscillators". IEEE JSSC 33, 6 (1998), 928.

Figure 7. Frequency vs. voltage characteristic for VCO<sub>1</sub>: (a)V<sub>DD</sub>=3.0V, (b)V<sub>DD</sub>=2.7V, (c)V<sub>DD</sub>=1.8V

Figure 8. Single-sideband phase noise for VCO<sub>1</sub> at 150.9MHz: (a) predicted, (b) measured