### **SYSTEM-LEVEL SYNTHESIS:**

#### **From Specification to Transaction-Level Models**

### Daniel D. Gajski

Center for Embedded Computer Systems University of California, Irvine http://www.cecs.uci.edu/~ese/

### **Three Models Needed**

Source: G Schirner

Embedded System Environment

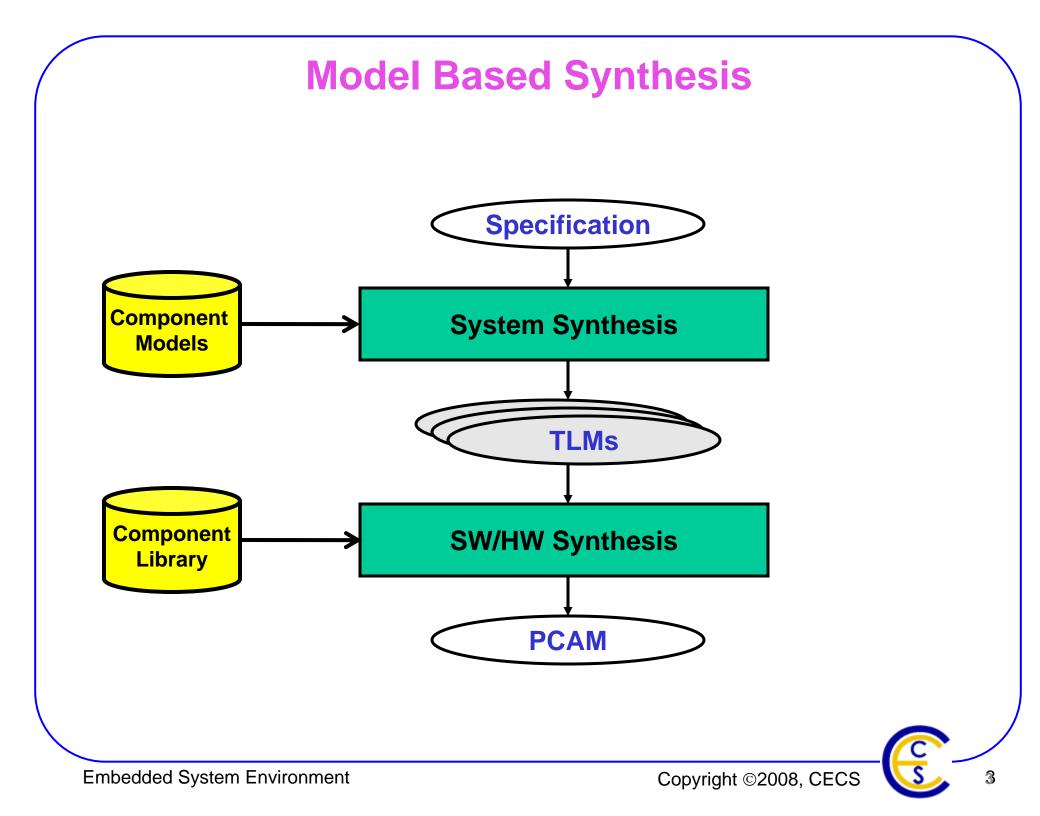

#### **Model-Based-Synthesis Advantages**

- No basic change in design methodology required

- Design flow follows present design process

- Productivity gain of more than 1000X demonstrated

- Designers do not write models

- Simple design update: 1-day change

- No rework for new design decisions

- High error-reduction: Automation + verification

- Error-prone tasks are automated

- Simplified globally-distributed design

- Fast exchange of design decisions and easy impact estimates

- Benefit through derivatives designs

- No need for complete redesign

- Better market penetration through customization

- Shorter Time-to-Market through automation

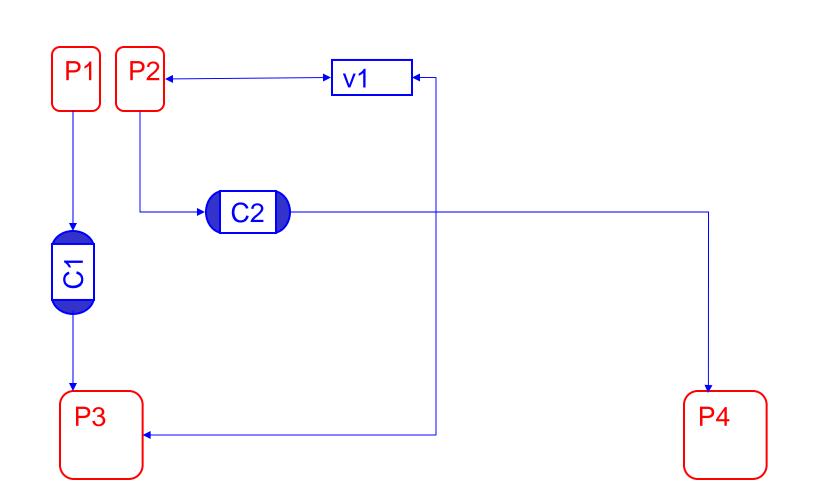

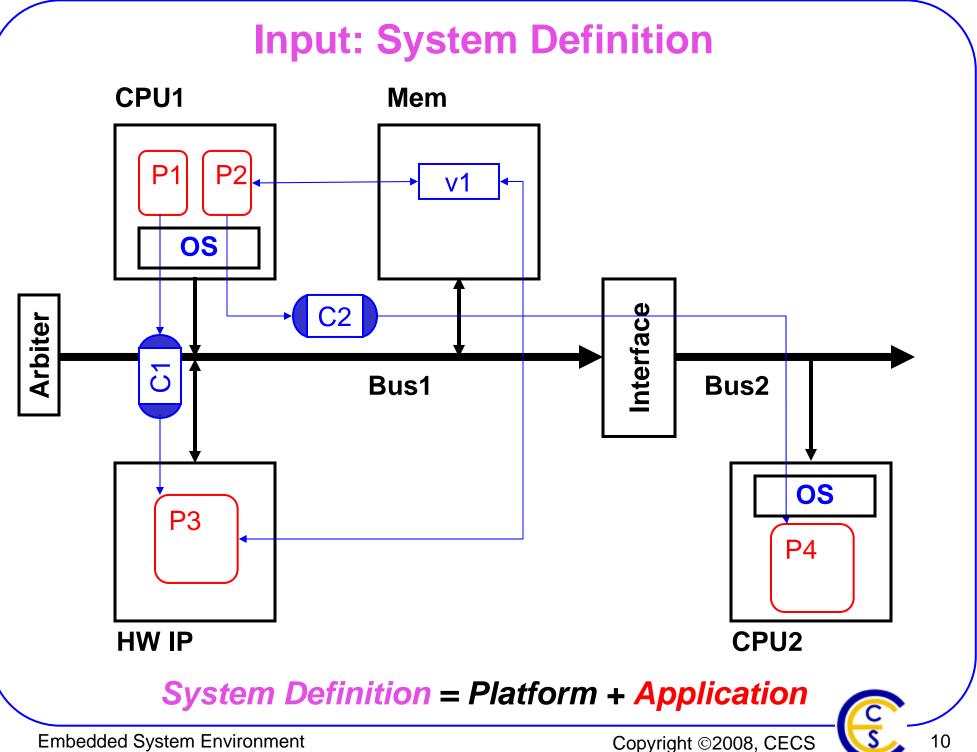

#### **Application Model**

#### **Application Model: set of communicating processes**

Embedded System Environment

8

Embedded System Environment

11

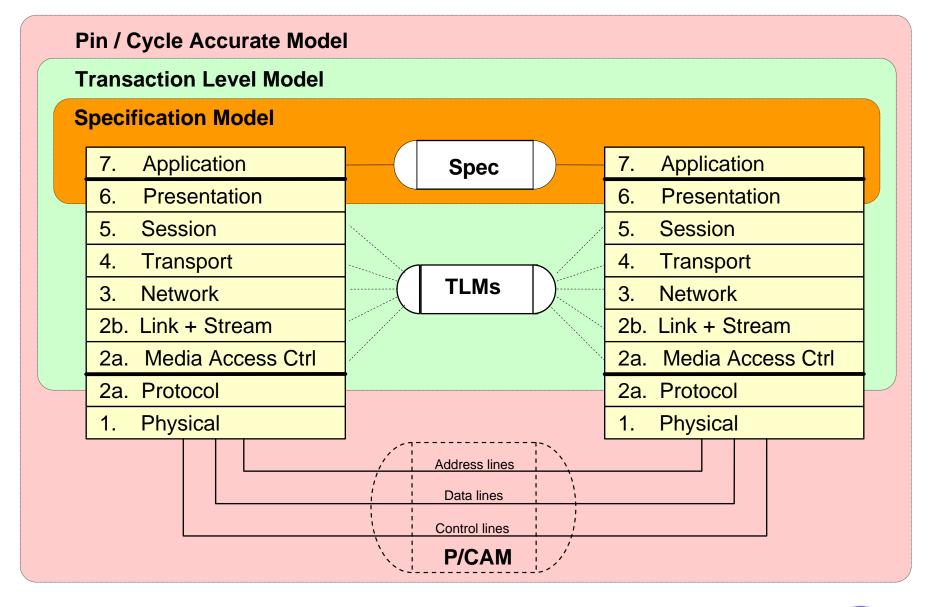

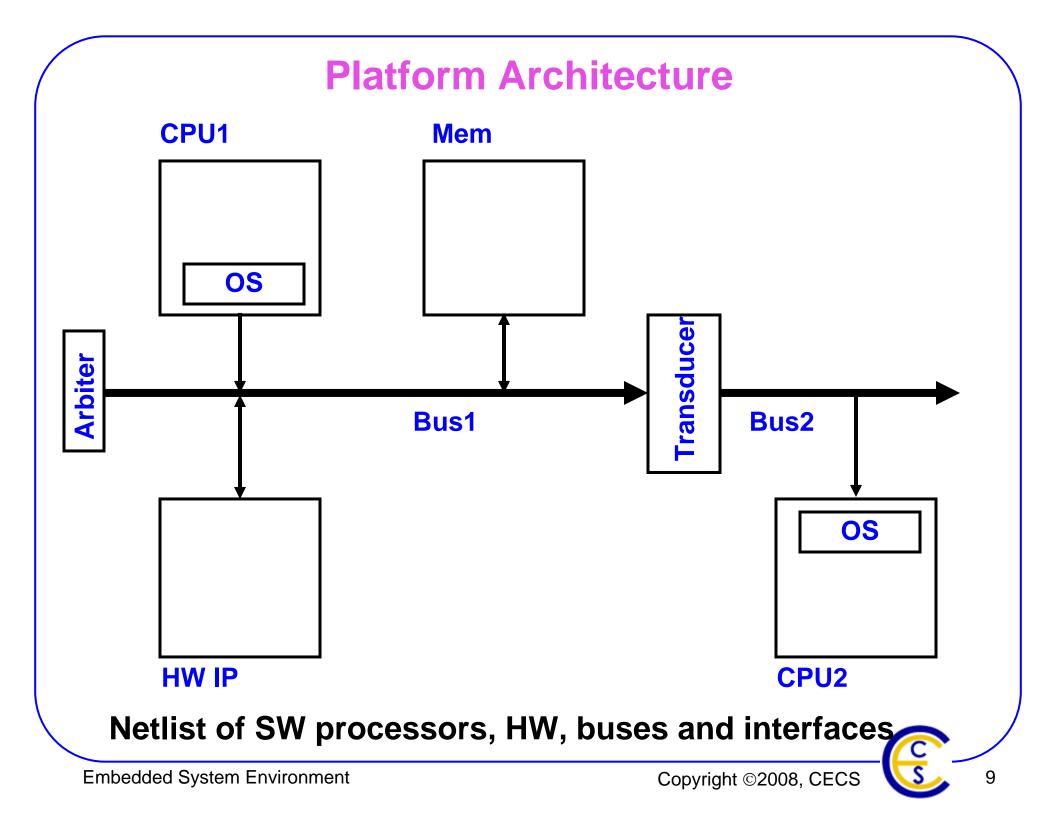

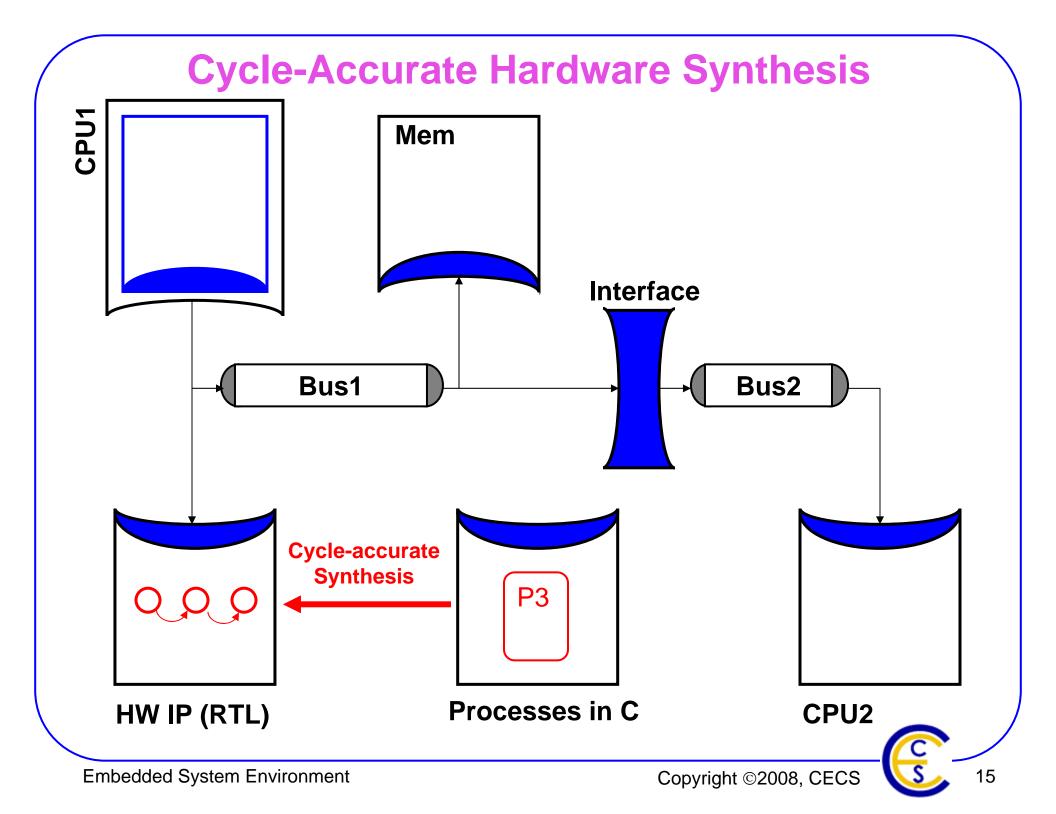

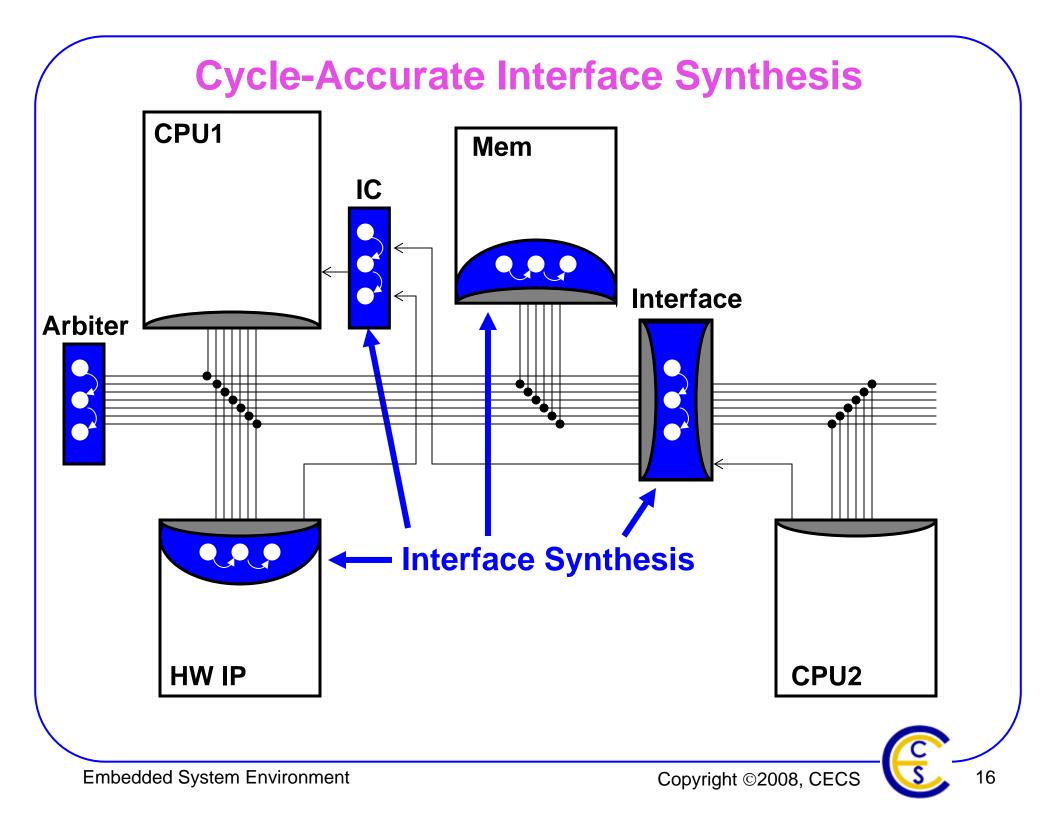

#### **Pin/Cycle-Accurate Model** CPU1 Program Mem IC EXE **RTOS** HAL Interface $\leftarrow$ Arbiter

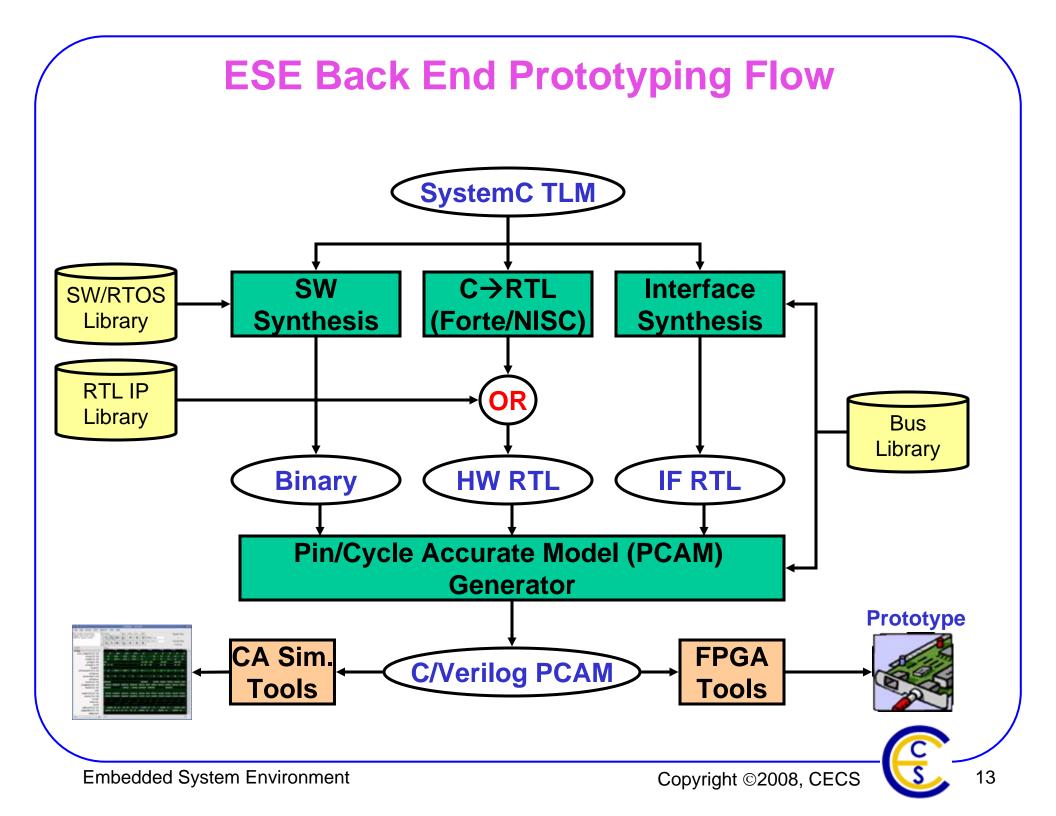

PCAM is downloaded automatically for fast prototyping with FPGAs or simulated using validation tools

**HW IP**

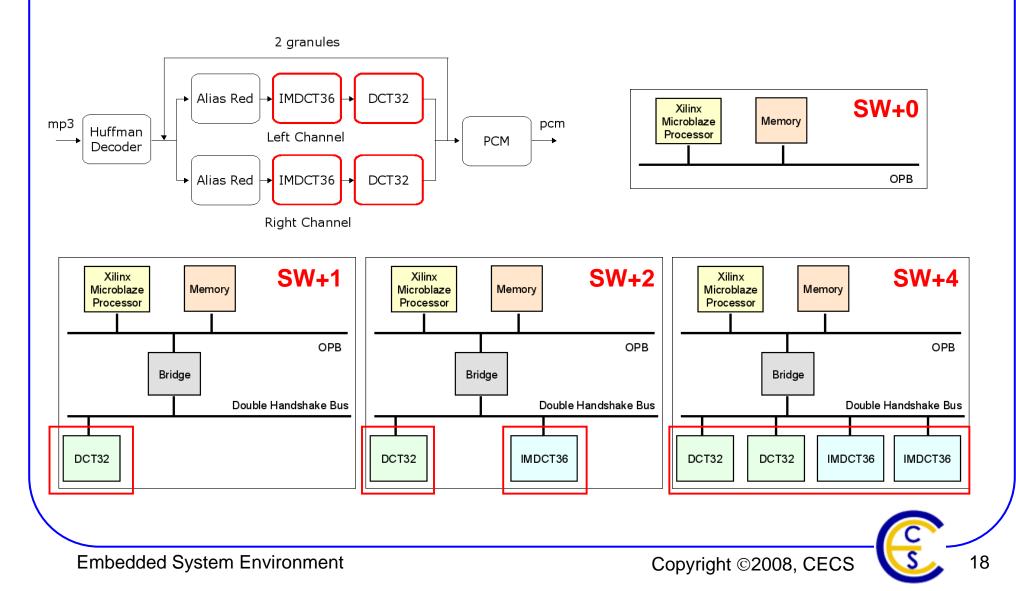

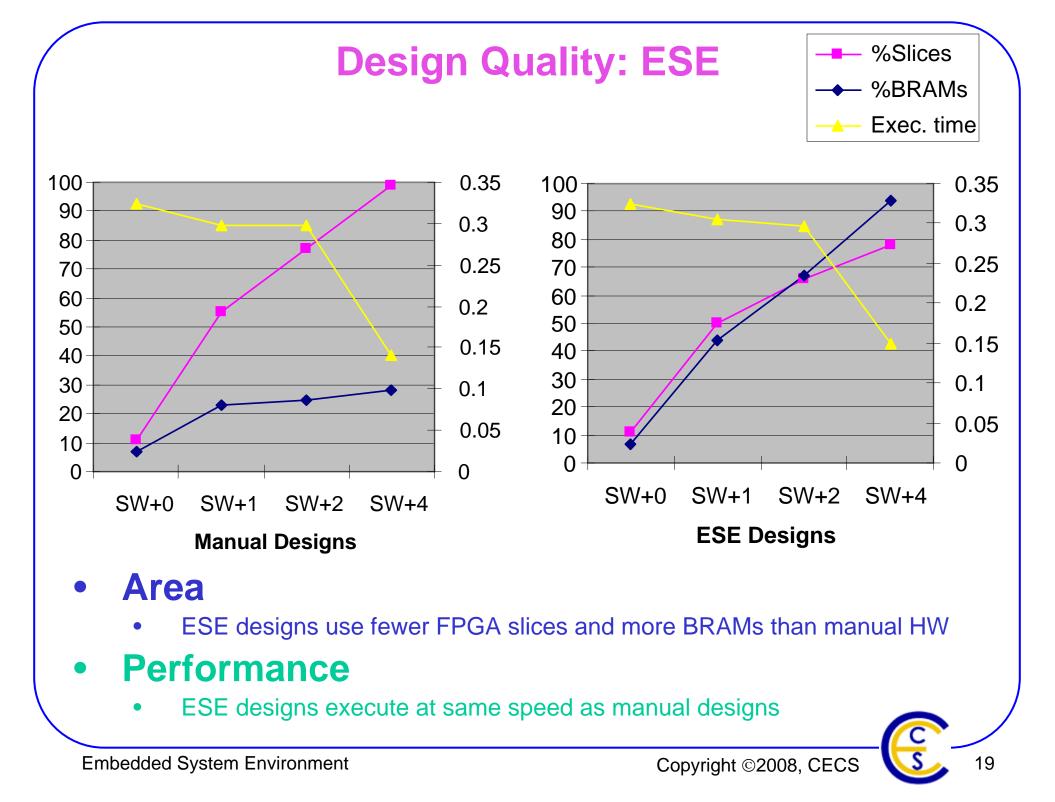

### **MP3 Design with ESE**

- MP3 Decoder(>12K LOC) on Xilinx Multimedia FPGA board

- Microblaze soft-core with 0/1/2/4 HW components

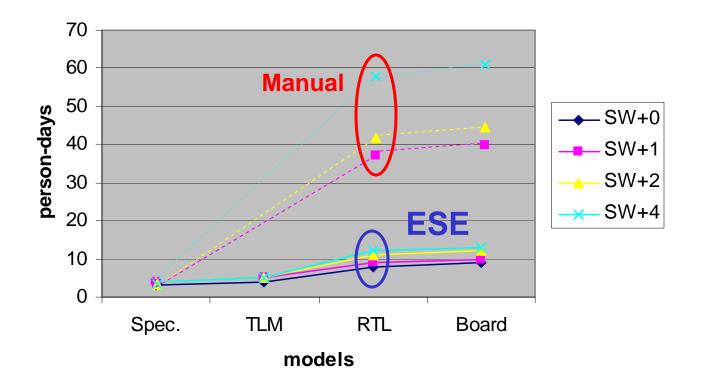

### **Development Time: ESE vs. Manual**

#### • ESE drastically cuts RTL and Board development time

- Manual development includes months of RTL coding

- Models can be developed at Spec level with ESE

- TLM, RTL and Board models are generated automatically by ESE

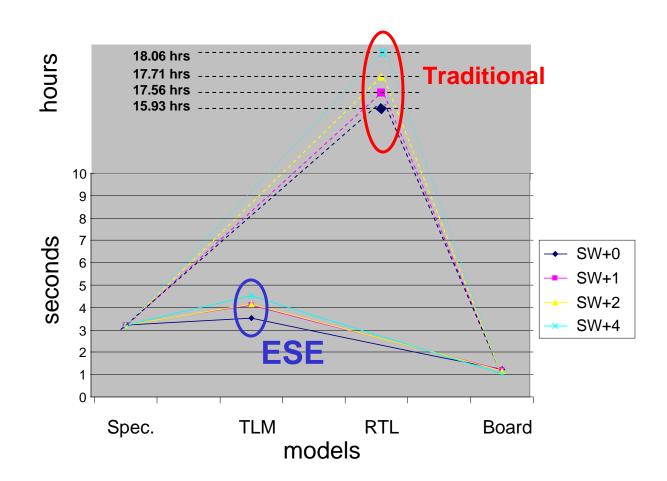

### Validation Time: ESE vs. Traditional

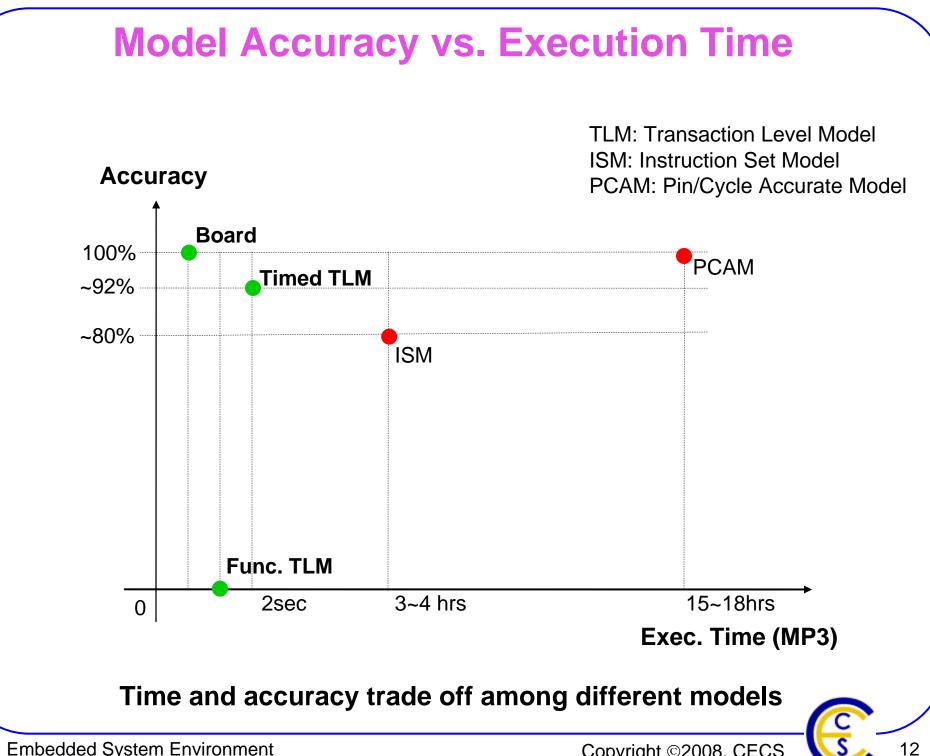

#### • ESE cuts validation time from hours to seconds

- No need to verify RTL models for every design change

- Designers can perform high speed validation with TLM and board

## **Technology Summary**

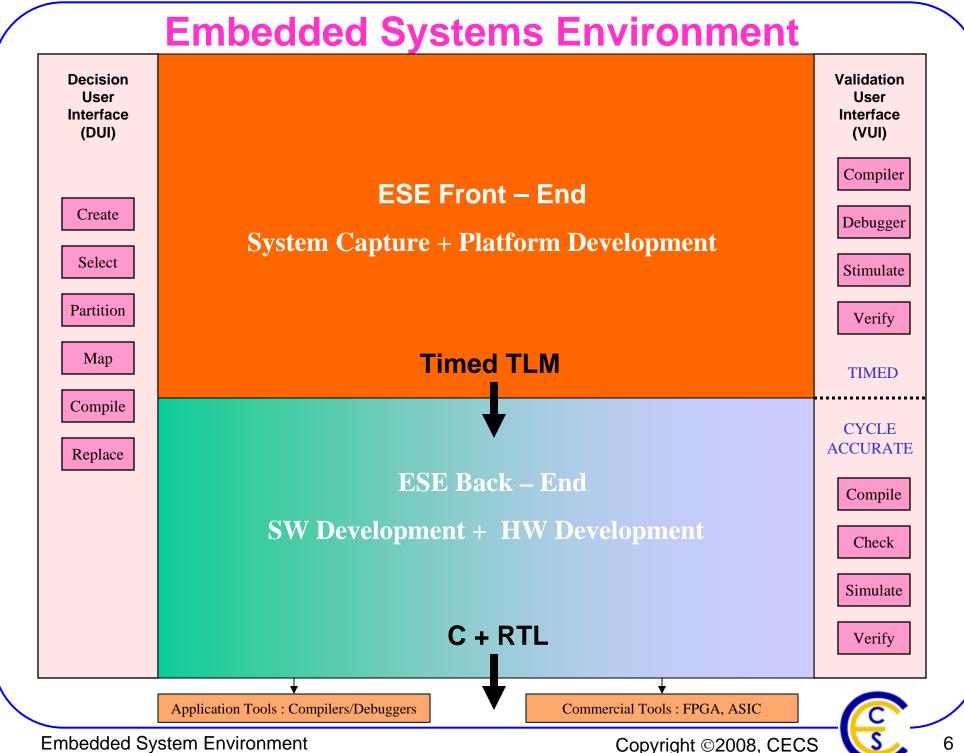

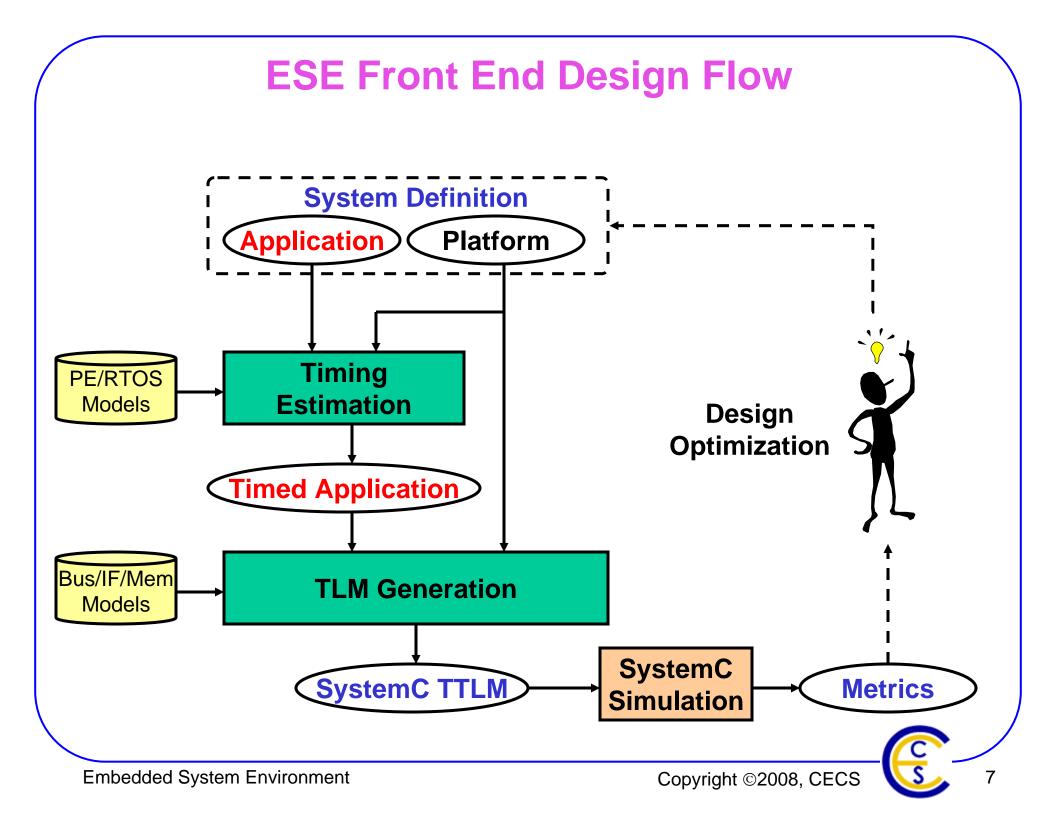

- C based application input

- Supports model based design and legacy reuse

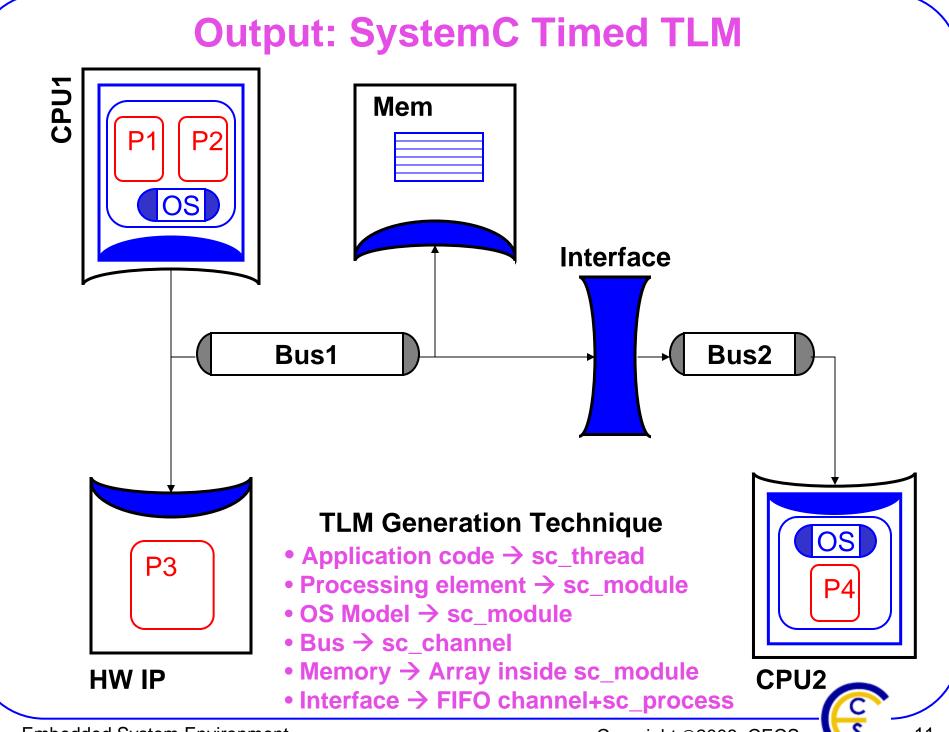

- Automatic functional and timed TLM generation

- Enables early design validation and reliable estimation

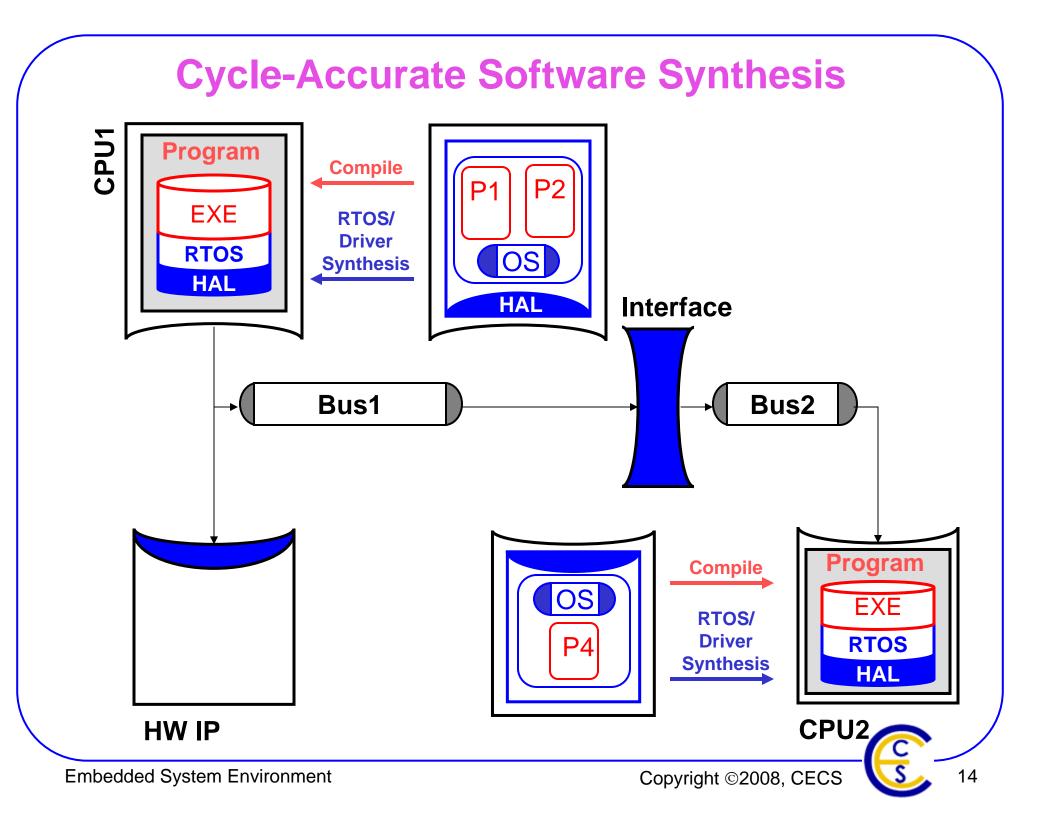

- Automatic SW synthesis

- Provides modular, verifiable, platform specific SW code

- Automatic interface synthesis

- Allows rapid implementation of heterogeneous networks

- FPGA and C/HDL export

- Generates standard input for commercial prototyping and CA validation tools

### **Business Benefits**

- Huge productivity gain

- Easy change and upgrade management

- Model-based design and manufacturing

- Executable specification for suppliers

- Easy verification of supplied parts

- Easy integration, assembly, repair

- New platform exploration and definition possibilities

- In-house early prototyping possibilities

- Early evaluation and implementation of standards

- Huge competitive edge

Acknowledgement

I would like to thank ESE team at CECS that has contributed many ideas through numerous discussions and made ESE tool work: Samar Abdi Lochi Yu Yonghyun Hwang Hansu Cho and Gunar Schirner

# **Thank You**

#### Embedded System Design

Modeling, Synthesis, Verification

> Daniel D. Gajski Andreas Gerstlauer Samar Abdi Gunar Schirner

🙆 Springer