# Co-design of Emulators for Power electric Processes Using SpecC Methodology

Slim Ben Saoud, Daniel D. Gajski

Technical Report ICS-01-46 July 25, 2001

Center for Embedded Computer Systems

Department of Information and Computer Science

University of California, Irvine

Irvine, CA 92697-3425, USA

(949) 824-8059

Slim Ben Saoud

Fulbright Visitor @ CECS

INSAT-Tunis-TUNISIA

sbensaou@ics.uci.edu

http://www.cecs.uci.edu/~sbensaou

Daniel D. Gajski

CECS

UCI-California-USA

gajski@ics.uci.edu

http://www.cecs.uci.edu/~gajski

# Co-design of Emulators for Power electric Processes Using SpecC Methodology

Slim Ben Saoud, Daniel D. Gajski

Technical Report ICS-01-46 July 25, 2001

Center for Embedded Computer Systems

Department of Information and Computer Science

University of California, Irvine

Irvine, CA 92697-3425, USA

(949) 824-8059

Slim Ben Saoud

Fulbright Visitor @ CECS

INSAT-Tunis-TUNISIA

sbensaou@ics.uci.edu

http://www.cecs.uci.edu/~sbensaou

Daniel D. Gajski

CECS

UCI-California-USA

gajski@ics.uci.edu

http://www.cecs.uci.edu/~gajski

#### Abstract

Emulation of CMS systems is an interesting approach to complete the validation of new digital control unit and to perform the diagnosis tasks. However to be efficient, the emulator have to run in real time in order to reproduce exactly the physical process functioning.

Today, realization of this emulator is not possible using standard electronic components. Therefore, we oriented our work to the development of new embedded systems specific to these applications of emulation.

This report describes the design of this emulator employing the system-level design methodology developed at CECS-UC Irvine (SpecC methodology). Starting from the abstract executable specification written in SpecC language, different design alternatives concerning the system architecture (components and communications) are explored and the emulator is gradually refined and mapped to a final communication model. This model can then be used with backend tools for implementation and manufacturing. For illustration of this approach, we discuss at the end of this report the case of a DC system emulator and we describe in details the different stages undergone.

# Contents

| 1                     | Introduction 1                                                         |                                                                             |                            |  |

|-----------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------|--|

| 2 Emulator Principles |                                                                        |                                                                             | 1                          |  |

| 3                     | Spe                                                                    | ecC Methodology [1,2]                                                       | 2                          |  |

| 4                     | Spe                                                                    | ecification Model                                                           | 4                          |  |

| 5                     | Arc                                                                    | chitecture Exploration                                                      | 5                          |  |

|                       | 5.1.1<br>5.1.2<br>5.1.3                                                | 2 Variable Partitioning and Scheduling                                      | <b>6</b> 6 7               |  |

|                       | 5.2.1<br>5.2.2<br>5.2.3                                                | 2 Variable Partitioning and Scheduling                                      | <b>7</b><br>7<br>8<br>8    |  |

| 5                     | 5.3                                                                    | Remarks                                                                     | 8                          |  |

| 6                     | Cor                                                                    | mmunication Synthesis                                                       | 9                          |  |

| (                     | 6.1.1<br>6.1.2                                                         |                                                                             | <b>9</b><br>9<br>10        |  |

|                       | 6.2.1<br>6.2.2<br>6.2.3                                                | Protocol Inlining Results                                                   | 12<br>12<br>14<br>15       |  |

| 7                     | Example of a DC System                                                 |                                                                             | 16                         |  |

|                       | 7.1                                                                    | Specification Model                                                         | 17                         |  |

|                       | DSP                                                                    | Architecture Model  Communication Model racteristic  56KCC Format  E Format | 17<br>17<br>19<br>19<br>19 |  |

| 8                     | 3 Conclusion                                                           |                                                                             |                            |  |

| Re                    | fere                                                                   | nces                                                                        | 20                         |  |

| A                     | Specification Model for the DC Emulator (Integer Form)                 |                                                                             |                            |  |

| В                     | 3 Architecture Model for the DC Monitored - Emulator (Integer Form) 21 |                                                                             |                            |  |

| C                     | C Communication Model for the Monitored - Emulator (Integer Form)      |                                                                             |                            |  |

| D                     | Architecture Model for the DC Autonomous - Emulator (Integer Form)     |                                                                             |                            |  |

| F.                    | Communication Model for the Autonomous - Emulator (Integer Form)       |                                                                             |                            |  |

# **List of Figures**

| Figure 1: Structure of the emulation application                                               | 2  |

|------------------------------------------------------------------------------------------------|----|

| Figure 2: Structure of the diagnosis application                                               | 2  |

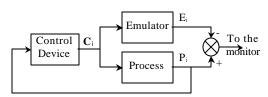

| Figure 3: SpecC methodology                                                                    | 3  |

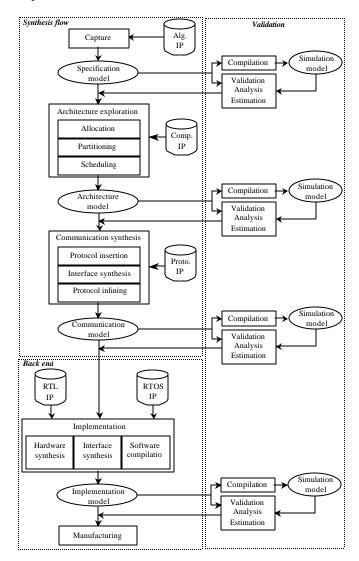

| Figure 4: Specification model of the emulator                                                  | 4  |

| Figure 5: Detailed Specification model of the emulator                                         | 5  |

| Figure 6: Architecture model after allocation and behavior partitioning (monitored emulator)   | 6  |

| Figure 7: Architecture model after variable partitioning and scheduling (monitored emulator)   | 7  |

| Figure 8: Architecture refined model after channel partitioning (monitored emulator)           | 7  |

| Figure 9: architecture model after allocation and behavior partitioning (autonomous emulator)  | 8  |

| Figure 10: architecture model after variable partitioning and scheduling (autonomous emulator) | 8  |

| Figure 11: Architecture refined model after channel partitioning (autonomous emulator)         | 9  |

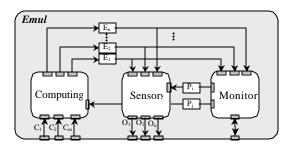

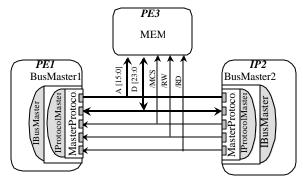

| Figure 12: Decomposed architecture of the emulator                                             | 9  |

| Figure 13: IP component insertion into the architecture model                                  | 9  |

| Figure 14: Intermediate communication model after protocol insertion (monitored emulator)      | 9  |

| Figure 15: Protocols of the DSP56600 external bus                                              | 10 |

| Figure 16: Communication model after protocol inlining (monitored emulator)                    | 11 |

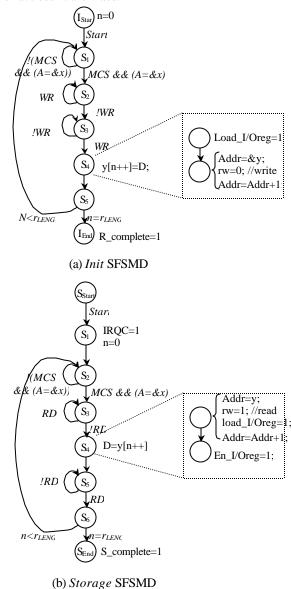

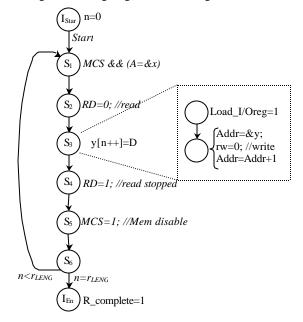

| Figure 17: HW communication SFSMDs                                                             | 11 |

| Figure 18: HW/SW interfacing model (monitored emulator)                                        | 12 |

| Figure 19: Communication model after protocol insertion (autonomous emulator)                  | 12 |

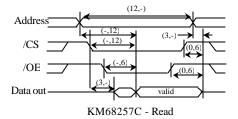

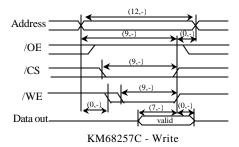

| Figure 20: Memory bus protocol (KM68257C)                                                      | 13 |

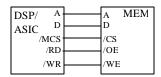

| Figure 21: Interfacing with memory block                                                       | 13 |

| Figure 22: Communication model after protocol inlinig (autonomous emulator)                    | 14 |

| Figure 23: HW communication SFSMDs (Autonomous emulator)                                       | 14 |

| Figure 24: DSP/Memory interfacing model                                                        | 15 |

| Figure 25: EIO sensor specifications                                                           | 16 |

| Figure 26: Emulator specification (case of a DC system)                                        | 17 |

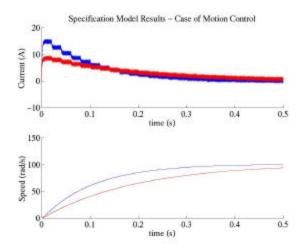

| Figure 27: Specification model results                                                         | 17 |

| Figure 28: Architecture refined model of the monitored emulator (case of DC system)            | 18 |

| Figure 29: Architecture model of the autonomous emulator (case of DC system)                   | 18 |

| Figure 30: Communication refined model (a-monitored emulator, b-autonomous emulator)           | 18 |

| Figure 31: Specifications of the C compiler floating-point format (DSP56600)                   | 19 |

|                                                                                                |    |

# Co-design of Emulators for Power electric Processes Using SpecC Methodology

#### Slim Ben Saoud, Daniel D. Gajski

Center for Embedded Computer Systems University of California, Irvine Irvine, CA 92697-3425, USA

#### ABSTRACT

Emulation of CMS<sup>1</sup> systems is an interesting approach to complete the validation of new digital control unit and to perform the diagnosis tasks. However to be efficient, the emulator have to run in real time in order to reproduce exactly the physical process functioning.

Today, realization of this emulator is not possible using standard electronic components. Therefore, we oriented our work to the development of new embedded systems specific to these applications of emulation.

This report describes the design of this emulator employing the system-level design methodology developed at CECS-UC Irvine (SpecC methodology). Starting from the abstract executable specification written different design alternatives SpecC language. concerning the system architecture (components and communications) are explored and the emulator is gradually refined and mapped to a final communication model. This model can then be used with backend tools for implementation and manufacturing.

For illustration of this approach, we discuss at the end of this report the case of a DC system emulator and we describe in details the different stages undergone.

# 1 Introduction

In this project we propose to design a real time emulator for electrical system using SpecC methodology [1,2]. This emulator will be used with the control device either for complete validation of this one at the development and validation stage or for diagnosis at normal functioning stage. In both cases, the emulator should behave like the physical system in real time.

Realization of this emulator is essentially faced to the execution time constraints. Indeed the emulator has to replace high dynamic systems in real time. So we distinguish three approaches in which real time emulator can be implemented: Digital, Analog and Hybrid. These approaches are discussed in previous publications [3,4,5].

The main difficulty in this realization is to satisfy both specifications of real time functioning and of flexibility.

On the other side, improvements in VLSI technology have to led the wide spread use of specific processor, which may also be used to realize complete system.

According to these considerations, our work is oriented to

Association of these characteristics imposed uses of

digital approaches, which guaranty user-friendliness.

According to these considerations, our work is oriented to the design of embedded systems specific to the emulation application. Therefore, we study the synthesis process of the emulation systems directly from their specification. This approach requires the ability to synthesize specified functions into software or hardware to meet the given constraints. It has the most flexibility since software, architecture and each component are custom made. However, it requires a well-defined methodology with clear steps, easy transformations and efficient tools to help the designer in the synthesis process.

In this project, we apply the SpecC methodology for the design of this real-time emulator.

In this report, we describe this new approach and we present the case of a DC system as an example. We present at the beginning an introduction to the emulation principles. From this description and according to the SpecC methodology, we deduce the specification model of the emulator. Then, we describe he different steps and transformations used to convert this model to a communication model according to the SpecC methodology. This model can be then transformed to an implementation model ready for manufacturing.

### 2 Emulator Principles

The objective of the emulation approach in the electric drive applications is to design an electronic system, which can reproduce the physical system functioning in real time and with high precision. This system, called emulator, will be used for both of the new control device validation and of diagnosis:

Validation of control device: before using the control device on the physical system and in order to avoid any design surprise (usually destructive and expensive), the control device is validated on the emulation step where it is connected to the emulator. This emulator should behave exactly like the physical

<sup>&</sup>lt;sup>1</sup> Static Converters / electric Motors / Sensors

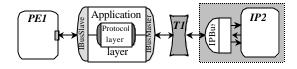

system, in sense to make the control device believe that it is connected to the real CMS<sup>2</sup> system. Thereby it has to generate and receive information similarly to the physical process: it receives control signals and generates information about the system state in forms identical to those obtained by sensors. After this step, the control device is completely validated and can be switched for use with the physical process as shown on figure 1.

C<sub>i</sub> Control signals / E<sub>i</sub> Emulator outputs / P<sub>i</sub> Process outputs

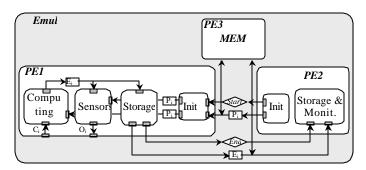

#### Figure 1: Structure of the emulation application

Diagnosis: The emulator is used in parallel with the process and must receive the same control signals as this process. Outputs of the emulator will be continuously compared in real time and in order to detect any dysfunction of this process. Stored results of the emulator will be used to analyze problems and to avoid or detect their origins.

$C_i$  Control signals /  $E_i$  Emulator outputs /  $P_i$  Process outputs

Figure 2: Structure of the diagnosis application

In both cases, the emulator has to reproduce accurately the process functioning. Therefore, it has to compute the System State and to convert the obtained results in forms identical to those obtained by sensors.

\_

For this and in order to obtain precise results, we should use precise models of different components used on this process and a high performance computing system with the lowest computing step as possible ( $1\mu s$  or less).

On the other hand, this emulator must be flexible, easily configurable by the user according to her/his application, and it must allow the storage of results and if necessary monitoring.

According to these previous considerations, the emulator structure will be composed of three main modules:

- Computing module: it computes, according to the digitized models, the system state variables. This computing is performed in a loop manner with a period *hor* (computing step) equal to \(\pu\)s or less for high precision applications. This module receives digital control signals and generates corresponding numeric results representing states of different components on the process (converter, motor, load and sensors).

- Emulation sensors module: it converts numeric results on different other forms identical to those obtained by the used sensors. Different types of conversion will be done like numeric/numeric (solver, ...), numeric/digital (encoder, ...), numeric/analog (LEM, ...). The execution of each conversion will be done in a periodic manner with a period that depends on the temporal characteristics of the sensor and the captured magnitude. However, these periods constraints are usually less severe than the computing module one.

- Monitoring module: it performs the acquisition of new parameters and the storage of results. It can also some perform monitoring tasks. For applications, the initialization task is performed only at the beginning of the emulator functioning. However, for high performances applications, it can be executed several times within the emulation running in order to introduce variation of system parameters due, for example to the variation of the environment like the temperature,... On the other hand, the storage operation will be done in a periodic manner with a period, Ts = x \* hor, where x is an integer configurable by the user.

# 3 SpecC Methodology [1,2]

With the ever increasing complexity and time-to-market pressures in the design of systems-on-chip (SOCs) or embedded systems in general, both industry and EDA vendors are trying to move the design to higher levels of abstraction, in order to increase productivity. At higher levels, there is no difference between hardware and software. An SOC is the combination of hardware and

<sup>&</sup>lt;sup>2</sup> Converter/Motor/Sensors

software, and at the system-level the disciplines merge. Great productivity gains can be achieved by starting design from an executable system specification instead of an RTL description as the golden reference model, throwing away all system models developed earlier in the process. However, we are still just at the beginning of understanding the design process at the system level. No tools and no well-defined design flows are available from industry or EDA vendors.

Managing the complexity at higher levels of abstraction is not possible without having a very well defined system-level design flow. A well-defined design methodology is the basis for all, synthesis, verification, design automation, and so on. Only then can we find or create a language that actually fits the desired flow, and not vice versa.

SpecC System-level design methodology and SpecC language are the result of decades of research done in the area of SOC design at the Center for Embedded Computer Systems (CECS) at the University of Irvine California (UCI).

SpecC language was developed exactly for the purpose of supporting a system-level design flow, and it therefore satisfies all the requirements of synthesizability, verifiability, and so on. SpecC is a superset of C and adds a minimal, orthogonal set of concepts needed for system design. It is currently in the process of being standardized.

The SpecC methodology is a set of models and transformations on the models (Figure 3). The models written in programming language (SpecC language) are executables descriptions of the same system at different levels of abstraction in the design process. The transformations are a series of well-defined steps through which the initial specification is gradually mapped onto a detailed implementation description ready for manufacturing.

The SpecC design methodology is based on 4 well-defined models, namely a specification model, an architecture model, a communication model, and finally, an implementation model. In the following section, we will give a brief description of each model and of the refinement tasks leading from a functional specification model all the way to a cycle-accurate implementation model in SpecC.

Specification model: The SpecC system-level design methodology starts with the capture of the intended functionality in the form of an executable specification as shown in figure 3. This initial specification model describes the functionality as well as the performance, power, cost and other constraints of the intended design.

It does not make any premature allusions to implementation details.

During specification capture the designer may reuse existing code segments, functions or procedures by instantiating them out of an algorithm library.

Specification model is a purely functional model that abstracts the system functionality. It is the starting point of system design process and the input to architecture exploration task.

Figure 3: SpecC methodology

Architecture exploration: It refines the specification into an architecture model. It includes the design steps of allocation, partitioning of behaviors, channels, and variables, and scheduling.

Allocation determines the number and types of the system components, such as general-purpose or custom processors, memories, and busses, which will be used to implement the system behavior. Allocation includes the

reuse of intellectual property (IP), when IP components are selected from the component library.

Behavior partitioning distributes the behaviors (or processes) that comprise the system functionality amongst the allocated processing elements. Variable partitioning assigns variables to memories, and channel partitioning assigns communication channels to busses.

Scheduling determines the order of execution of the behaviors assigned to either the standard or custom processors after partitioning. In other words, scheduling is used for software and hardware components.

Architecture exploration is an iterative process culminating with an architecture model that represents a refinement of the specification model. Estimators evaluate each architecture candidate's satisfaction of the design constraints; until all constraints are satisfied, component and connectivity reallocation is performed and a new architecture with different components, connectivity, partitions, schedules or protocols is generated and evaluated.

Architecture model: It describes the system functionality as well as the overall structure of the final implementation for the design. The communication in the architecture model is through the abstract global channels.

Communication Synthesis: It refines the abstract communication between behaviors in the architecture model into implementation. The an task communication synthesis includes the insertion communication protocols, synthesis of interfaces and transducers, and inlining of protocols into synthesizable components. In the resulting communication model, communication is described in terms of actual wires and timing relationships are described by bus protocols.

**Communication model:** It is the final output of the system-level design process which describes the system structure as a set of components connected through the wires of the set of buses.

Backend: The result of the synthesis flow is handed off to the backend tools, as shown in the lower part of figure 3. The software part of the hand-off model consists of C code for compilation and the hardware part consists of behavioral C (VHDL) code for high-level synthesis. The backend tools include compilers and high-level synthesis tool. The compilers are used to compile the software C code for the chosen processor. The high-level synthesis tool synthesizes the functionality assigned to custom hardware and the functionality of transducers which are necessary for connecting different processors, memories, and IPs.

After software compilation and hardware synthesis, the final implementation model is generated.

**Implementation model:** It represents a clock-cycle accurate description of the whole system. This description, in turn, then serves as the basis for manufacturing of the system.

In each of the tasks the designer can make design decisions manually by using an interactive graphical user interface, for example, while transformations from one model into another can be accomplished automatically by following the refinement rules or model guidelines. After each refinement step in the synthesis flow, a corresponding SpecC model of the system is generated, which means that design decisions made in each design task are reflected in the generated models. Thus, in the validation flow that is orthogonal to the synthesis flow in the SpecC methodology, one can perform simulation, analysis and estimation of the SpecC models generated after each task.

After each design step, the design model is statically analyzed to estimate certain quality metrics such as performance, cost, and power consumption. Analysis and estimation results are reported to the user and backannotated into the model for simulation and further synthesis.

The design can be statically analyzed or simulated after each step for validation of design correctness in terms of functionality, performance, and other constraints. A simulation model is compiled after each step which can be run on the host computer to validate correctness for simulation.

At any stage of the refinement process, a standard software debugger can be used to locate and fix the errors if verification fails. Such debuggers enable one to set break points anywhere in the source code and to perform detailed state inspection at any time.

#### 4 Specification Model

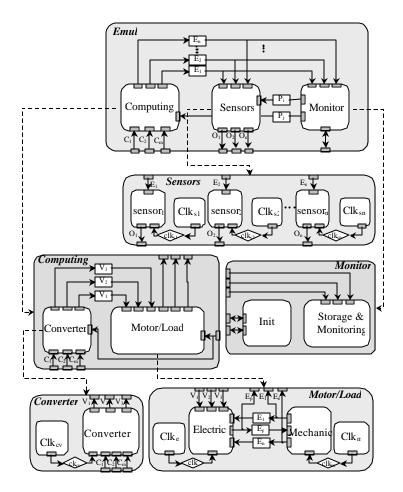

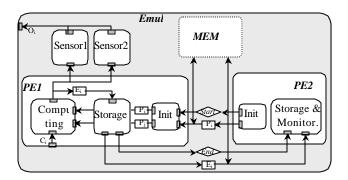

According to the previous description, the emulator can be described by a main behavior (*Emul*) including different sub-behaviors: one for the computing module, one for sensors and one for monitoring (Figure 4).

Figure 4: Specification model of the emulator

These behaviors are usually composed of other subbehavior according to the modular structure of the physical system. So, we use a sub-behavior for each of the converter, motor/load and sensor component and we add separate sub-behaviors for initialization process and for the monitoring module (including storage). These behaviors can also be decomposed of child-behaviors as we usually do with the motor/load behavior. Indeed, this behavior is usually decomposed on mechanic-child-behavior and electric-child-behavior (Figure 5).

Computing steps used with different modules are not the same since they don't have the same temporal characteristics. So we propose, for more flexibility, to add to each of the obtained child-behaviors a clock-generator behavior that controls its execution. The occurrence of the clock event is defined according to the module temporal characteristics.

However, we usually use the same computing step for the CM system (1 $\mu$ s) and different computing steps for each different type of sensor...

The obtained specification model is shown on figure 5. It was validated for the case of DC and AC systems.

Figure 5: Detailed Specification model of the emulator

Constraints: One of the most important constraints with this application is the computing time of the CM System State. Indeed, this computing must be done, according to the given models, in a periodic manner with a computing step of lus or less. While this seems to be realizable using High performance standard processors for the case of simple system using simple models, it is not possible for high performance application that needs sophisticated models and smaller computing step. Temporal problems of this computing, implemented into a processor, are related to the computing load and to the use of interruption for the periodic functioning management.

Other constraints such as the resolution of the used DAC devices and the resolution and precision of the used sensors (C.I.O, ...) will certainly influence the design procedure.

# 5 Architecture Exploration

At the architecture allocation phase, different possibilities can be used according to the application specifications (flexibility, time, cost, precision,...). However, since we need to store emulator results for monitoring and study, we distinguish two main structures according to the emulator integration on the physical system:

- Monitored emulator: with this structure, a master processor (PC or the micro-controller implemented on the control device) monitors the emulator. This master will initiate the emulator functioning by sending new parameters and will be used in parallel with the emulator to store results and treatment of these results for monitoring. Transmission of results is done in a periodic manner Ts.

- In this case, the emulator will interrupt the processor functioning at each new storage period in order to begin a transmission task. This solution imposed the use of interruption, which can disturb the running task performed by the master (case of the microcontroller).

- Autonomous emulator: the emulator is associated to an external memory on which will be stored emulation results. The emulator parameters and functioning is then independent from computing systems. At the starting step, it reads new parameters from the external memory block and then, at each new storage period, it will write new results into successive registers of this memory. Another processor used for initialization and monitoring will manage this memory when the emulation is off-line in order to initialize the process parameters and to restore emulation results. This solution is very useful when used with the micro-controller of the control device since it will not disturb the control tasks.

However it introduces some delay in the monitoring operation.

For each of these structures, different allocations can be studied. These allocations represent different possibilities of implementation of the emulation core *EmulCore* (computing and sensors emulation modules) between full-software and full-hardware solutions.

In our project, temporal constraints of our system are very severe, especially in the case of complex models. So, we chose to study the full-hardware solution.

In this case, we usually use one ASIC for computing of CM system states and a custom hardware for each (or some) sensors. This introduces communications between these different hardware blocks and the ASIC component. In order to simplify this presentation, we consider that all modules are included in the same HW component EmulCore.

In the following sections, we present the study of this solution when applied to the two described emulation structures (Monitored and Autonomous). Therefore, we will present for each of these structures the different modifications applied to the specification model in order to obtain the architecture model.

#### **5.1** Monitored Emulator

In this structure, the emulator is supervised by a software application, which initiates the emulator functioning and receives results from it. This solution is useful for monitoring and the software can be implemented on the control device microcontroller. However, in this case, cautions should be taken about the management of communication without disturbing the control tasks (since these transfers will be done using interruption of the microcontroller...).

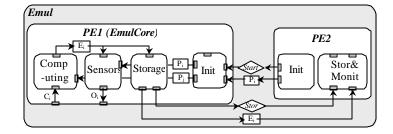

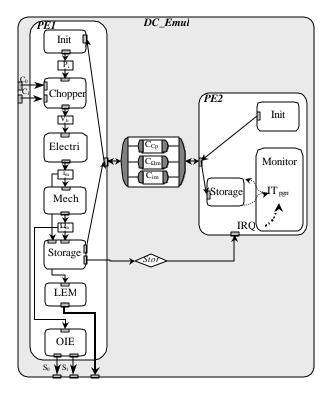

#### **5.1.1** Allocation and Behaviors Partitioning

The first step in architecture exploration is to allocate a set of processing elements (PEs) and to map the behaviors of specification onto the allocated PEs. In this structure and according to the previous considerations, the emulation system will be composed of two PEs: the hardware component *EmulCore* that performs emulation tasks and the software component used for initialization and results storage.

The obtained refined model after behavior partitioning is represented by figure 6. In this model, two behaviors are added to *EmulCore-PE1* (*init & storage* behaviors) in order to synchronize and establish communication with the software component. This communication becomes system-global and it is moved to the top-level connecting the PE behaviors.

Figure 6: Architecture model after allocation and behavior partitioning (monitored emulator)

#### 5.1.2 Variable Partitioning and Scheduling

The number of exchanged variables between HW and SW components is very limited (usually less than 10), so we chose to use local copies for these variables in each PEs. Therefore in the refined model obtained after variable partitioning, global variables for results and parameters are replaced with their respective abstract channels  $C_{\rm Pi}$  (for parameter Pi) and  $C_{\rm Ei}$  (for result magnitude Ei). Code is inserted into behaviors to communicate variable values over these channels. Note that data are exchanged in a vector type: one for parameters and one for results.

Scheduling The next step in the architecture exploration process is to schedule behavior executions on the inherently sequential processing elements. Processing elements have a single thread of control only. Therefore, behaviors mapped to the same PE can only execute sequentially and have to be serialized.

In this application, at the starting point, the emulator is waiting for a start order from the master. Then, it receives new parameters of the system sent by the master and begins its functioning tasks. At each x computing steps (storage period), the emulator will send results (im, Wm) to the master. Two functioning mode can be used with the master:

- It can be used only for monitoring of the emulation: initiating and receiving results. In this case after sending parameters, the master will wait for the results. In this solution, implementation of communication will be easy, however the master can't do any thing else at the same time.

- In this case, behaviors are executed in a fixed and predetermined order. The static scheduling approach will be applied easily by converting all concurrent statements into sequential compositions.

- The master is also used for other tasks such as control or treatment of these results for monitoring and diagnosis. Therefore, a dynamic scheduling approach is required.

In this case synchronization for information exchanges will be done using interruption. The emulator will send an interruption signal to the master each storage period in order to begin transfer. This solution is more adequate for embedded systems since it can be integrated easily in the control device, allowing then both application of validation and diagnosis.

In order to preserve the shared semantics of the variables keep the local copies inside synchronization, updated data values are exchanged between the components two at the existing synchronization points. Therefore, these updated data values are communicated over the existing messagepassing channels together with synchronization of the behaviors execution among the PEs.

According to these purposes, the intermediate architecture model obtained after variable partitioning and scheduling is represented by figure 7.

Figure 7: Architecture model after variable partitioning and scheduling (monitored emulator)

# 5.1.3 Channel Partitioning

The goal of the channel partitioning is to group and encapsulate all the channels existing between the communicating blocks into one bus. The bus is also a type of channels in SpecC and it implies that the future implementation would be wired busses.

In our application, we have only two components communicating with each other. Therefore, only one

system bus is allocated connecting PE1 and PE2, and all communication channels are mapped onto that bus.

The obtained refined model is represented by figure 8.

Figure 8: Architecture refined model after channel partitioning (monitored emulator)

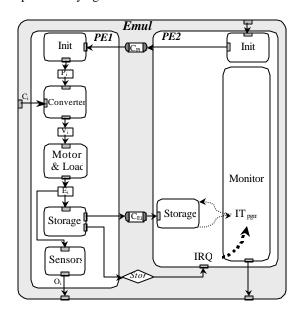

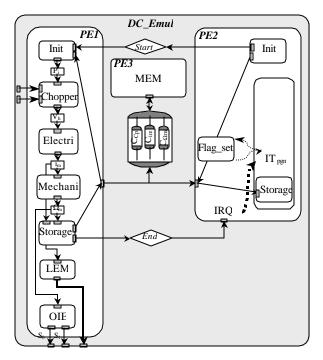

#### **5.2** Autonomous Emulator

A memory is added to the emulator system in order to obtain an independent emulation system. In this memory will be stored both the system parameters and the emulation results. At he beginning, the emulator starts by reading of parameters at corresponding addresses on the memory, and then it will store, at each storage period, the obtained results. Both the emulator and the monitor will manage this memory.

This solution can be used either alone or with a software component (as on the control device). The main advantage is the portability and the autonomy of this emulator since it will not interrupt the software component. This last can at each time ask memory for information. The start/stop of the emulator can be done by the SW component.

To simplify the application, we assumed that the monitor manages this memory only when the emulator is stopped. So, there's no management of transfer conflicts to perform. However, synchronization between Hardware and Software components must be done at the beginning and at the end of the emulation procedure.

#### 5.2.1 Allocation and Behaviors Partitioning

As specified before, the architecture target will be composed of three components: the EmulCore hardware

component, the software component (processor) and the memory block. This memory, shared by the two active components, is used for storage of parameters and emulation results.

However, local copies are added, especially, to the emulator component in order to perform its computing as fast as possible without asking the memory at each computing step for data. These local copies correspond to the used parameters and to the results obtained in the last computing step (or in the n last computing steps according to the used method for digitizing).

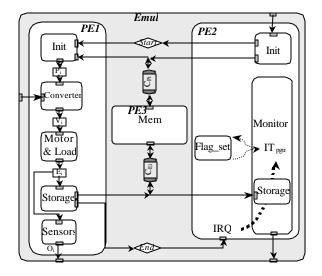

The obtained refined model after behavior partitioning is represented by figure 9. In this model, two behaviors are added to EmulCore (init & storage behaviors) in order to synchronize and establish communication with the software and memory components.

This communication becomes system-global and it is moved to the top-level connecting the PE behaviors. Synchronization is done at the beginning and the end of the emulation procedure by using two events *Start* and *End*. The processor generates the *Start* event after computing the new system parameters according to the user configuration. It signals to the init behavior in the EmulCore component that parameters are ready. Then, the emulator starts its computing and storage procedures. At the end of its functioning, it sends the *End* event to the software component signaling that emulation is stopped and that data are ready in the memory block.

Figure 9: architecture model after allocation and behavior partitioning (autonomous emulator)

### 5.2.2 Variable Partitioning and Scheduling

In this case and according to the previous specifications, synchronization between HW and SW components are performed by using of two events *Start* and *End*.

The *Start* event can be associated to the parameters variables Pi and encapsulated into a Message-Passing channel that models the abstract communication semantics of blocking, unbuffered message-passing between any two client-behaviors.

On the other hand, the *End* event will be connected to a processor interrupt input. The interruption program is

used to set a flag  $F\_end$  when this interruption is activated. When the software program needs the emulation results for monitoring, it tests this flag. If it is set, it performs the data read sequences from memory, otherwise it waits for the interruption activation.

The obtained refined model after variable partitioning and scheduling is shown on figure 10.

Figure 10: architecture model after variable partitioning and scheduling (autonomous emulator)

Note that, the emulation can generate the digital signal  $F\_end$  instead of the event End. And then, no interruption is required for the synchronization.

#### **5.2.3** Channel Partitioning

The obtained architecture target is composed of two active PEs (PE1 and PE2) that share a memory block (PE3). Therefore, only one bus is used into which all the global channels and their implementation are encapsulated (figure 11).

#### 5.3 Remarks

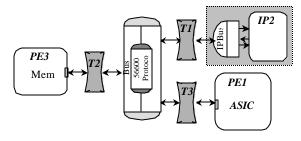

These structures can be decomposed into others components according to the complexity of the studied system. This bursting will usually concern the distribution of sensors on others hardware components as shown on figure 12.

We can also distribute a complex child behavior like the *Motor/Load* behavior on several components. However this will introduce communication protocols and then cautions must be taken in order to obtain the best compromise "performance/cost". These distributions have to be studied in more details with estimation tools according to the defined application.

Figure 11: Architecture refined model after channel partitioning (autonomous emulator)

Figure 12: Decomposed architecture of the emulator

#### 6 Communication Synthesis

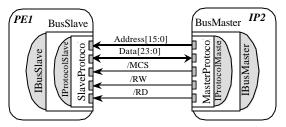

SpecC architecture model, obtained architecture exploration, the communication components is still modeled on a high level through abstract channels. The channels were obtained by simple encapsulation of global variables and their corresponding synchronization. Although the channels represent the grouping according to the mapping onto busses, they do not yet contain any information about the actual implementation of the communication primitive's semantics (send(), receive(),...). The communication synthesis, therefore, is to gradually refine the channels in the system model down to an actual implementation with data transfers over wires. This comprises the steps of protocol insertion, transducer synthesis and protocol inlining [6].

In our application, the software component is usually chosen from standard processors (IP components). Therefore, PE2 will be replaced at the communication synthesis by this predesigned processor chosen from the

component library. This processor has predefined functionality and fixed external interfaces and communication protocols.

In the process of protocol insertion, the SW component will then be replaced with a model of the IP component that includes the IP component behavior and the protocol wrapper (Figure 13). The wrapper provides the abstract canonical interface for communication with the environment.

Note that in case of protocol incompatibilities, transducers components will have to be inserted between the IP component and the bus to translate between the protocols.

Figure 13: IP component insertion into the architecture model

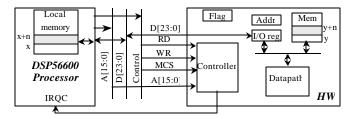

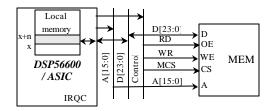

For the illustration of our application we will use the DSP56600 (Motorola) as the chosen IP component for implementing the software behaviors [7].

#### **6.1 Monitored Emulator**

#### 6.1.1 Protocol Insertion

Figure 14 shows the emulator model after insertion of a bus protocol for the system bus, and after the processor behavior has been replaced with a model of the real processor with a wrapper.

Figure 14: Intermediate communication model after protocol insertion (monitored emulator)

In this case, we propose to use the processor protocol as the system protocol. Then the transducer will be removed during inlining, since processor and bus protocol are identical. However, transducer will be added, if needed, between hardware protocol and the system bus protocol. This transducer will be later synthesized with the hardware component.

Usually, no protocol is defined for the hardware part, so we need to analyze the HW datapath to generate the I/O protocol and then insert the transducer component.

Note that in order to simplify this illustration, we suppose that the hardware component has the same protocol as the system bus (DSP56600 protocol). Then, the transducer is not required.

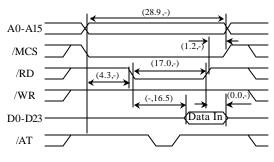

The protocol channel in the system bus and the wrapped processor model describe and implement the processor bus protocol according to its timing diagram, shown in figure 15. The protocol layer provides primitives for performing read/write transfers and for raising interrupts over the processor bus.

On top of the protocol layer, the application layer created during protocol insertion implements the semantics of the abstract communication of the bus channel, using the primitives provided by the encapsulated protocol channel.

On the software side, the communication primitives of the application layer are customized I/O routines inside the processor that become part of the generated RTOS. The I/O routines together with customized interrupt handlers perform the necessary handshaking and data conversions to implement the semantics of the communication primitives using the processor's I/O instructions.

On the hardware side, the communication primitives are part of the system bus application layer. They will later be inlined into hardware and realized as additional FSMDs that implement the low-level bus protocol and the high level handshaking and data conversions.

DSP56600 - SRAM Read

Figure 15: Protocols of the DSP56600 external bus

DSP56600 - SRAM Write

In the monitored emulator of the emulator example and after protocol insertion, the DSP is the central component and the master of the system bus. The software on the DSP initiates all data transfers on the system bus between software and hardware components. However, this

software is associated to a DSP interrupt, which is triggered by the hardware by using asynchronous events.

The DSP is the communication master, the required blocking, synchronous message passing semantics are realized as follows: the ASIC signals its ready state by raising an interrupt whenever it reaches a communication point (at the beginning of each new Ts period). The software on the DSP performing the task of control or of monitoring will be interrupted in order to execute the transfer program. So, it begins by transferring the data one word at a time by repeatedly executing instructions that initiate read or write cycles on the external bus.

The hardware has a dedicated address that corresponds to a location in the DSP memory space. Once software and hardware at both ends are synchronized, the DSP as the master on the bus initiates and controls data transfers by reading from or writing to the memory location with the address of the custom hardware. The ASIC, on the other hand, detects its own address and answers DSP requests by supplying or storing the requested data from and to their local registers or memories.

On top of the actual low-level transfers, synchronization and handshaking between hardware and software is handled by sending and receiving events on both sides. On the processor side, the operating system sends events to the custom hardware by writing to the external bus address assigned to it. Than, signaling an event is implemented by initiating a data transfer over the processor bus and to the hardware component and therefore both can be combined. The hardware component listening on the bus receives the transfer request event and supplies or stores the data. On the other hand, the Custom hardware PEs sends event to the software by interrupting processor. Indeed. the hardware signals availability of new computation results to the processor by raising an interrupt line.

Note that the interrupt assigned to the hardware component should be with the highest priority in order to perform emulation in real time.

#### 6.1.2 Protocol Inlining

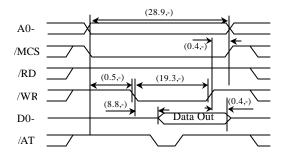

Finally, inlining of the wrapper functionality into hardware components is performed (Figure 16): the resulting SFSMDs for interrupt generation, address decoding and bus protocol handling functionality are combined with the SFSMD executing the behavior originally assigned to the custom hardware coprocessor. Both parts will then be synthesized together to generate the final custom hardware. After inlining, the actual ports and connections are exposed and visible, resulting in the final system model as actually seen after implementation.

Figure 16: Communication model after protocol inlining (monitored emulator)

In the case of the ASIC emulator system, communication primitives are inlined into the *init* and *storage* behaviors that have been created during partitioning for synchronization and communication between the ASIC and the processor. Both the applications and protocol layers of the communications primitives that had been created during protocol insertion are inlined into the custom hardware behaviors.

The application layer performs synchronization with the DSP and converts the complex data structures into bus transfers. The protocol layer performs the actual bus transfers according to the protocol shown in figure 15.

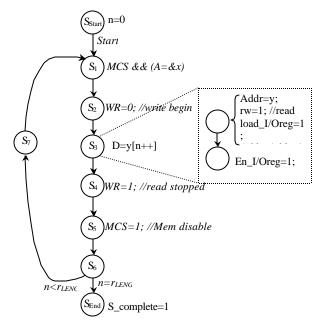

The *Init* SFSMD synchronizes with the software on the DSP, receives the process parameters over the processor bus, and starts the emulator computing. At each new storage period (Ts=Xs cycles), the storage SFSMD synchronizes with the DSP (by generating an interruption) in order to transfer the emulation results back to the processor. For their bus transfers, the SFSMDs (figure 17) implement the bus protocol according to the timing diagram shown in figure 15.

The Init SFSMD waits for a falling edge of the chip select signal MCS and samples the bus address in state S1 until a transfer with the address of the ASIC is recognized. In state S2, the WR control signal is sampled until a falling edge has been detected that signals the beginning of a bus write cycle. In state 3, the Init SFSMD waits for the rising edge of signal WR before latching the data bus contents into I/O register, writing the data from the I/O reg into local memory Mem, and incrementing the address register Addr in superstate S4. Finally, it increments and checks the loop counter in state S5, and branches back to wait for the start of the next word transfer until all data tems have been received. Then it will activate the emulator computing.

The storage SFSMD synchronizes with the DSP by raising the processor's interrupt line *IRQC* in its first state *S1*. Then it waits for a falling edge of the chip select signal MCS and samples the bus address in state S2 until a transfer with the address of the ASIC is recognized. In state S3, the RD control signal is sampled until a falling edge has been detected that signals the beginning of a bus read cycle. In superstate S4, the storage SFSMD reads the

data word from the custom hardware memory Mem into the I/O reg, increments the local address register Addr, and enables I/O reg on the data bus. It then waits for the rising edge of RD in state S5. Finally, it increments and checks the loop counter in state S6, and branches back to wait for the start of the next word transfer until all data items have been transmitted.

Figure 17: HW communication SFSMDs

In case of this application, we assume that the synthesized hardware for the Init and Storage SFSMDs will be fast enough to handle bursts of successive transfers initiated by the master processor at the maximal processor bus speed (2 processor cycles per bus transfer). Therefore, the delay of the loops in the SFSMDs has to be less than 2 processor cycles. Otherwise, wait states have to be added to the bursts of bus transfers on the processor side, or

more elaborate handshaking scheme (e.g. DMA or interrupt-based acknowledgment of single transfers) would become necessary.

Figure 18 shows the implementation of the interface between hardware and software after final inlining.

Figure 18: HW/SW interfacing model (monitored emulator)

The sequence for transferring data and control from the DSP to the ASIC is:

- 1- Under the assumption that the coprocessor is ready whenever the software on the DSP wants to initiate the emulator parameters, the DSP starts writing these parameters onto the DSP bus. The processor successively writes the block of data for the hardware onto the bus one word at a time by initiating a sequence of bus write cycles with the address assigned to the coprocessor.

- 2- The Init SFSMD of the HW component is triggered by an address match, receives the data word over the bus, latches it in its I/O reg and finally stores the latched data in the local memory of the ASIC as described previously.

- 3- When the last data has been received, control in the ASIC model is transferred from the Init SFSMD to the SFSMD corresponding to the emulatorcomputing behavior.

- 4- The emulator computing SFSMD reads the process parameters from the local memory and starts the emulator computing process.

The transfer of emulator results to the DSP is handled in a similar manner:

- 1- The emulator computing SFSMD writes the obtained results back into the memory. At the beginning of each Ts period, control is transferred to the Storage SFSMD in the hardware component.

- 2- The Storage SFSMD interrupts the processor and then waits for the start of the bus data transfer.

- 3- The interrupt program on the DSP starts the communication software. The processor reads the data from the hardware component I/O reg over the bus one word at a time by initiating a sequence of successive bus read cycles. The data is read one

- word at a time using the address assigned to the I/O reg in the ASIC.

- 4- The storage SFSMD in the ASIC decodes the bus address, reads the results from the local memory, and puts the requested data on the bus.

- 5- After each read, the ASIC loads the I/O reg with the next data word until the complete complex data is sent to the DSP.

Note that for each message, the processor transfers the data items sequentially over the bus one word at a time in a predefined, fixed order. Hence, at each step in the sequence of data transfers it is implicitly defined which word of which data item is currently being transferred. The custom hardware and the DSP keep track of the sequence of data transfers, and according to their internal sides determine how to process the transferred item.

The interrupt priority assigned to the ASIC must be with high priority in order to not interrupt the transfer between the emulator and the DSP. This allows a real time functioning of the emulation system.

#### **6.2** Autonomous Emulator

#### **6.2.1** Protocol Insertion

Figure 19 shows the emulator model after the insertion of the DSP bus protocol as the system bus protocol, and after the processor behavior has been replaced with a model of the real processor with a wrapper. Transducer will be added, if needed, between hardware protocol and the system bus protocol. On the other hand, memory must be able to respond to the read and write requests from DSP and ASIC. This again requires design of a bus interface for memory to respond to bus read/write requests. The behaviors and complexity of such interfaces depends on the time-constrained behavior of these components at their ports. So, we must discuss the timing behavior of these components and then analyze these interfaces [8].

Figure 19: Communication model after protocol insertion (autonomous emulator)

Note that in order to simplify this illustration, we assume that the hardware component has the same protocol as the system bus (DSP56600 protocol).

On the other hand, we experimented with Samsung memory KM68257C [9], which is a CMOS static RAM

and has 8 common input and output lines. The different pins and the memory specification for read and write cycles are shown in figure 20.

Figure 20: Memory bus protocol (KM68257C)

According to these specifications, this memory is fast enough and will be used directly without any additional interface according to the schema of figure 21. Therefore, no interfaces are required with this architecture model.

Figure 21: Interfacing with memory block

Parameters and results are stored in the memory at precise corresponding locations with precise addresses that correspond to free locations in the DSP and ASIC memory spaces.

According to this structure architecture model, we distinguish two masters sharing the same bus and the same memory component:

- DSP: it writes at the beginning parameters values to their corresponding locations in the memory block, and reads results tables;

- ASIC: it reads at the beginning parameters from their corresponding locations, and writes results at each execution of the storage behavior (Ts period).

So, cautions must be taken in order to avoid communication conflicts. Two solutions can be considered:

- Without management of the bus: The DSP initiates the emulator functioning after initialization of the memory with new parameters. Indeed, it sends to the emulator the start event to start the emulator functioning. At the reception of this signal, the emulator, begins by reading parameters from the corresponding memory locations and then starts the computing process. According to the previous specifications, the emulator writes results to the memory at each Ts period. These results are written in a table. Along this time, the DSP can perform others tasks; however it is not allowed to do transfer on its external bus while the emulator is running. When the emulation process is finished, the hardware informs the DSP by sending an external event that can be used with interruption that sets a corresponding flag or by setting a signal connected to a processor digital input. So the DSP, when it is ready for results acquisition will test this flag, and then perform the acquisition of the result table for analysis. The two main advantages of this solution are that the required management of the bus is very simple and the monitoring processor performs other tasks while running emulator. However, the DSP has some functioning restrictions (forbidden access to the external bus during emulation) and cannot read results before the end of the emulator computing.

- With management of the bus: The beginning of operation is done like the previous solution: the DSP initialize the memory then initiate the emulation functioning. Then, both the DSP and the ASIC can access to the memory for read/write. Specific primitives in the application layer will manage conflicts and priority is given to the ASIC. The main advantage of this solution is to allow the access of the DSP to the memory to change parameters or read results in order to perform the monitoring operations. However, this solution requires a sophisticated protocol to manage conflicts. This solution can be used for high performance application indeed it can introduce, for example, in real time parameters variations due to the temperature variation and to asynchronous events and it can perform monitoring in real time since it has not to wait the end of the emulation and the DSP can at each time read results from the memory.

As described in previous sections, the application layer, used in the components (ASIC and DSP), wraps around the protocol layer and implements the abstract communication semantics required by the behaviors in the application over the primitives supported by the protocol. In this structure of the emulator system, this layer has to perform tasks like synchronization, arbitration, addressing

of data on the bus, slicing of abstract data types into bus words.

In this project, we implement the case of the first solution (without management of the bus), which represents a simple bus management protocol.

In this case the required synchronous passing semantics are realized as follows: The DSP determines new parameters and it stores them in their locations inside the memory block. Then, it signals by an asynchronous event to the emulator that data are ready and it continue execution of other tasks without using its external bus. The emulator waiting for the start signal from the DSP, receives this event and then execute the init behavior before beginning emulator computing. At each Ts period, the emulator increments the memory address and store new results in a table. At the end of its computing, the ASIC signals by an asynchronous event to the DSP that results are ready in the memory. This event will interrupt the DSP program and set a flag. The DSP, tests this flag when results are required in order to perform new acquisition.

#### 6.2.2 Protocol Inlining

The communication model obtained after inlinig is represented by figure 22. As detailed in the previous section, the applications and protocol layers are inlined into the *init* and *storage* behaviors that have been created during partitioning for synchronization and communication between the ASIC and the processor. The application layer performs synchronization with the DSP and converts the complex data structures into bus transfers. The protocol layer performs the actual bus transfers according to the protocol shown in figure 15.

Figure 22: Communication model after protocol inlinig (autonomous emulator)

The *Init* SFSMD synchronizes with the software on the DSP, it receives the start signal from it. Then, it reads the process parameters over the processor bus from the memory, and starts the emulator computing. At each new storage period ( $Ts=x_s$  hor), the storage SFSMD writes

emulation results into the memory table. When finished, the ASIC send an event to the DSP signaling that data are ready in the memory and that bus is "free". For the bus transfers, the SFSMDs implement the bus protocol according to the timing diagram shown in figure 23.

#### (a) Init SFSMD

(b) Storage SFSMD

Figure 23: HW communication SFSMDs (Autonomous emulator)

The *Init* SFSMD waits for a falling edge of a signal *start* generated by the DSP. Then it begins the parameters read from the memory: it begin by enabling the address

register on the address bus and falling the signal MCS for the memory selection (S1). Then, it falls the signal RD in state S2 for signaling the beginning of a bus read cycle. In the superstate S3, it latches the data bus contents into the I/O reg and writes the data from the I/O reg into local memory Mem and increments the address reg Addr. In state S4, it ends the read cycle by raising the RD and the MCS signals (S5). Finally, it increments and checks the loop counter in state S6, and branches back to start the next word read cycle until all data items have been received. Then it will activate the emulator computing. In this transfer, parameters have same address in both the memory block and ASIC local memory.

At each new storage period, the storage SFSMD performs the writing process into the memory of the emulator computing results. It begins by enabling the address reg on the address bus and falling the signal MCS for the memory selection (S1). Then, it falls the signal WR in state S2 for signaling the beginning of a bus write cycle. In the superstate S3, the storage SFSMD reads the data word from the custom hardware memory Mem into the I/O reg, increments the local address register Addr, and enables I/O reg on the data bus. In state S4, it ends the write cycle by raising the WR signal and then it disables the memory selection by raising the MCS signal (S5). In state S6, it increments and checks the loop counter in state S4, and branches to state S7 until all data items have been received. In state S7, it increments the address corresponding to the next register to write in the external memory block. At the end of this transfer sequences, the Storage SFSMD gives control to the emulator computing SFSMD in order to continue the emulation process.

Note that in the SFSMDs description in figure 23 we omitted the temporal synchronization representation in order to simplify the schema. This synchronization is done according to the protocol diagram of figure 15.

Figure 24 shows the implementation of the interconnection between the three used components after final inlining.

Figure 24: DSP/Memory interfacing model

The sequence for transferring data and control between the DSP and the memory is:

- 1- When the software on the DSP wants to initiate the emulator parameters in the memory, the DSP starts writing these parameters onto the DSP bus. The processor successively writes the block of data onto the bus one word at a time by initiating a sequence of bus write cycles with the corresponding addresses assigned to the parameters registers in the memory block.

- 2- Then, it sends an event to the ASIC signaling that new parameters are already stored in the memory and begins another task without using the external bus

- 3- Once the software on the DSP is ready to receive the results, it performs an operating system call that checks the interrupt flag. If the flag is set, the RTOS call returns immediately. Otherwise, the RTOS waits until the interrupt has been received before returning to the caller. In both cases, the RTOS resets the flag before returning.

- 4- The DSP reads the data from the memory block over the bus one word at a time by initiating a sequence of successive bus read cycles. The data is read one word at a time using the address assigned to the corresponding register in the memory component.

The sequence for transferring data and control between the ASIC and the memory is:

- 1- The emulator computing SFSMD waits for the starting signal generates by the DSP then control is given to the Init SFSMD.

- 2- The Init SFSMD performs read of parameters from the external memory then it gives control to the emulation computing behavior.

- 3- At each Ts period, the Storage SFSMD is activated in order to perform writing of new results.

- 4- At the end of the emulation procedure, the emulator sends an event to the DSP signaling that results are ready in the memory block.

Note that for each message, the processor transfers the data items sequentially over the bus one word at a time in a predefined, fixed order. Hence, at each step in the sequence of data transfers it is implicitly defined which word of which data item is currently being transferred. The custom hardware and the DSP keep track of the sequence of data transfers, and according to their internal sides determine how to process the transferred item.

#### 6.2.3 Results

A final simulation of these communication models including interrupt handling, external data transfers, and so on, was done. As described before, the communication model is a bus functional model. The behaviors in the

component are simulated on a functional level in native C language annotated with estimated delays. On the other hand, communication between components is modeled accurately over actual wires of the processor bus.

In the backend, these models will be synthesized into a structural view of all components in the system architecture. The functionality of each component will be implemented on top of the component's RTL or instruction-set micro-architecture. In the process, timing will be refined down to the level of individual clock cycles based on each component's clock period.

# 7 Example of a DC System

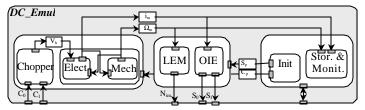

To validate this new approach of emulator design, based on SpecC methodology, we describe in this section the case of a DC system emulator. This system is composed of a DC motor fed by a four-quadrant chopper and associated to a Hall sensor for the current capture and to an Optical Incremental Encoder for the speed capture.

For the computing of this system state, we use simple models for the chopper and the electrical motor. These models are digitized using Runge-Kutta 2 and obtained equations are as follows:

#### - Motor/load

$$\begin{cases} i_{m}(k+1) = \mathbf{a}i_{m}(k) + \mathbf{b}\Omega_{m}(k) + \mathbf{g}V_{h}(k) \\ \\ \Omega_{m}(k+1) = \mathbf{I}i_{m}(k) + \mathbf{m}\Omega_{m}(k) + \mathbf{n}sign(\Omega_{m}(k)) \end{cases}$$

(1)

$\alpha$ ,  $\beta$ ,  $\gamma$ ,  $\lambda$ ,  $\mu$  and  $\nu$  are obtained from system parameters and computing step *hor*.

- Chopper

$$V_h = (C_0 - C_1)V_e \tag{2}$$

$V_e$  is the input voltage,  $V_h$  the output voltage and  $C_0$ ,  $C_1$  control signals.

The Hall sensor output is a voltage magnitude that represents the current value. This output voltage depends on the Hall sensor characteristics and the current value. In our case this dependency is represented by a simple model as described by equation1: Vout=im\*5/15 volts. A more sophisticated model (including influence of noises, temperature, wear,...) can be specified in this behavior in order to reproduce more precisely the Hall sensor output.

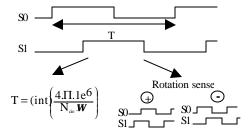

The optical incremental encoder generates two quadrature square wave signals (S0 and S1) with the same frequency (proportional to the motor frequency) as represented by the figure 25.

Figure 25: EIO sensor specifications

In our project we studied two solutions according to the used data format. The first one used Floating-point format (floating emulator) and the second one used integer format (integer emulator).

For the integer emulator, models equations used for computing are converted into integer form. This translation is made according to two main considerations in order to have the best computing precision:

- We take the same precision level of the system parameters when coding them in integer form (1e<sup>-6</sup>);

- We used  $\Delta i_m$  and  $\Delta w_m$  instead of  $I_m$  and  $\Omega_m$ , which represent variations of  $i_m$  and  $w_m$  where:

$$\begin{cases} i_m = \frac{1}{1024} I_m \\ \mathbf{w}_m = \frac{1}{1024} \Omega_m \end{cases}$$

This allows obtaining a good precision of computing.

According to these considerations, we obta

following equations:

$$\begin{cases} 128.\Delta i_{m}(k+1) = \frac{a.i_{m}(k)}{1024} + \frac{b.\frac{\mathbf{w}_{m}(k)}{8}}{1024} + g_{v}(C_{0}(k) - C_{1}(k)) \\ \Delta W_{m}(k+1) = l.i_{m}(k) + m.\mathbf{w}_{m}(k) + n.sign(\mathbf{w}_{m}(k)) \end{cases}$$

where:

$$\begin{cases} a = 128.1024.(\boldsymbol{a} - 1) \\ b = 1024.1024.\boldsymbol{b} \\ g_v = 1024.128.\boldsymbol{g}.V_e \end{cases}$$

and:

$$\begin{cases} I = 1024.1024.I \\ m = 1024.1024.(\ m-1) \\ n = 1024.1024 \mathbf{n} \\ \Delta W_m(k+1) = 1024.1024.\Delta \mathbf{w}_m(k+1) \end{cases}$$

a, b,  $g_v$ , l, m and n will be the new parameters of this system.

The main advantage of the integer form is to simplify the computing unit.

# 7.1 Specification Model

According to the previous description, the specification model of the emulator can be represented as shown on figure 26.

Sp Sensors parameters / Cp Computing parameters

## Figure 26: Emulator specification (case of a DC system)

The execution of these different behaviors is well scheduled by using different clock behaviors. Note that for simplification reason, clock generator behaviors are not represented in this figure (Figure 26).

The *init* behavior is executed only one time at the beginning of this model execution. It performs the computing of different parameters and the initialization of intermediate variables. Parameters are obtained, as specified in previous equations, according to the system characteristics, to the digitizing method and to the retained computing step.

All the other behaviors are executed in a periodic manner with different periods. These periods are specified in the clock generator behaviors by using the instruction **waitfor**(*Time\_delay*). When the *Time\_delay* is reached, the clock behavior generates an event that will activate corresponding computing behavior.

Note that at this stage, there is not any notion of time. Therefore, values ( $Time\_delay$ ) used with these clock behaviors serve only to the scheduling of behaviors execution. Execution procedure is supposed to be done with 0 time\\_delay.

These behaviors execution is scheduled as following:

- The storage behavior is used, in our example, only for the capture of emulator results (no monitoring task is employed). Therefore it is executed at each  $T_s = X_s$ . hor period  $(X_s = 10)$ .

- The computing core of the system state (chopper & motor/load) is executed at each Tc=hor period. It performs the computing of the needed System State magnitudes, which are in our case  $i_m$  (current) and  $W_m$  (speed).

- The LEM behavior is used to emulate the LEM running, which generates a voltage corresponding to the current magnitude. This behavior will be associated with a DAC component. So, it generates the corresponding integer  $N_{\rm im}$  according to the obtained current value im and to the resolution of the

- used DAC. According to the high dynamic of the electrical mode, the execution period of this behavior must be fast enough to cover the current variation with high precision. However, it is limited by the temporal characteristics of the DAC (time needed for conversion). In our case we use a delay equal to 5  $(X_i=5)$ .

- The OIE behavior is used to generate two digital signals identical to those obtained by the OIE sensor and according to the speed value  $W_m$ . Since, the variation of the speed magnitude is very slow, we usually use an important delay time for the execution of this module. In our case we used  $x_0$ =1000.

The obtained specification model is validated by simulation. Figure 27 represents the obtained results for the current magnitude im.

Figure 27: Specification model results

Note: The specification model represent different modules in parallel like the physical system. However, the execution is done in a sequential manner!!!

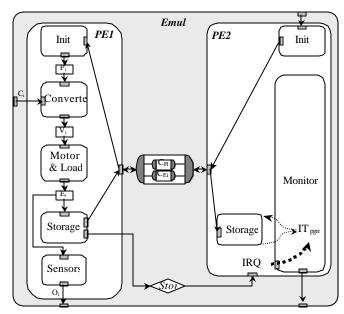

# 7.2 Architecture Model

The Architecture exploration has been done following the described steps and transformations of section 5. Therefore, two refined architecture models are retained and validated for each of the floating emulator and the integer emulator.

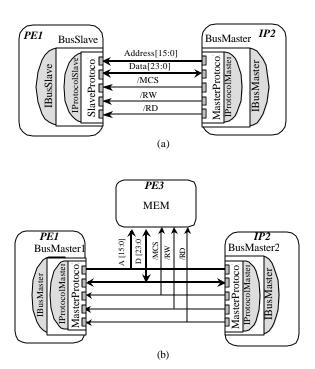

#### 7.3 Communication Model

The two studied structures, described in section 6, are applied to the case of the DC system. So for each of the floating emulator and integer emulator, we designed a communication model for the monitored structure and another for the autonomous structure.

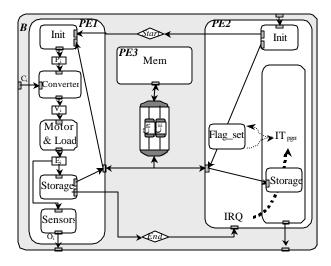

Figure 28: Architecture refined model of the monitored emulator (case of DC system)

Figure 29: Architecture model of the autonomous emulator (case of DC system)

For this design, we used the DSP56600 as a software component and for the autonomous structure we add a

block of High Speed Static RAM (32Kx8 bit) type KM68257C (Samsung). The communication exploration is done according the transformations described in section 6.

In this example, we used the DSP external bus protocol as the system bus protocol and we suppose that the hardware and software protocols are compatible. The memory, as specified in section 6, is fast enough and it doesn't require any other interface. Therefore, we didn't include transducers in the communication model (figure 30).

Figure 30: Communication refined model (a-monitored emulator, b- autonomous emulator)

However, actually we should determine the HW SFSMD in order to study accurately the compatibility with the system bus protocol. Otherwise, transducer must be included and synthesized.

Communication and synchronization are specified as mentioned in section 6. the Data transfer is performed in a vector type by the application layer. This layer performs several tasks like synchronization, addressing of data on the bus, slicing of abstract data types into bus words...

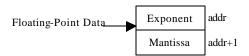

Especially, in our example and in the case of the floating emulator, this application layer performs the conversion of floating data to words in order to transfer them from a component to another over the system bus. This conversion is done according to the DSP56600 C compiler specifications and to the floating format implemented on the hardware. In this example we

suppose that the hardware use the same format as described on the DSP56600 C compiler.

In DSP56600, the C data float and double are both implemented as single precision in a format different to the IEEE STD 754-1985 standard format for binary floating-point arithmetic. Figure 31 represents some specifications of this format. For more details, refer to Motorola technical books.

| Characteristic  | DSP56KCC         | IEEE Format       |

|-----------------|------------------|-------------------|

|                 | Format           |                   |

| Mantissa        | 23 bits          | 24 bits           |

| precision       |                  |                   |

| Hidden leading  | No               | Yes               |

| One             |                  |                   |

| Mantissa Format | 24 bit Two's     | 23 bit Unsigned   |

|                 | Complement       | Magnitude         |

|                 | Fraction         | Fraction          |

| Exponent Width  | 16 bits (14 bits | 8 bits / 11bits   |

|                 | used)            |                   |

| Format Width    | 48 bits          | 32 bits / 64 bits |

Figure 31: Specifications of the C compiler floatingpoint format (DSP56600)

The obtained communication models including interrupt handling are validated by simulation. Therefore they are ready for synthesis in the backend process. A long this process, these models will be transformed into cycle-accurate implementation models according to the following tasks:

- HW component will be synthesized into a netlist of register-transfer level (RTL) components;

- SW will be converted into a C program, compiled into the processor's instruction set and possibly linked against an RTOS;