VLSI DESIGN 2009 • IMPROVING PRODUCTIVITY THROUGH HIGHER ABSTRACTION PROCEEDINGS OF THE 22nd INTERNATIONAL CONFERENCE ON VLSI DESIGN 5-9 January 2009 I Ū 0 L THE 7th INTERNATIONAL CONFERENCE **N** EMBEDDED SYSTEMS COMPUTER SOCIETY

Published by the IEEE Computer Society 10662 Los Vaqueros Circle P.O. Box 3014 Los Alamitos, CA 90720-1314

IEEE Computer Society Order Number P3506 BMS Part Number: CFP09041-PRT ISSN 1063-9667 ISBN 978-0-7695-3506-7

#### **PROCEEDINGS OF**

# **Table of Contents**

# **VLSI Design 2009**

| Message from the General Chairs            | XV      |

|--------------------------------------------|---------|

| Message from the Program Chairs            | xvii    |

| Message from the Organizing Chair          | xix     |

| Conference Steering Committee              | xx      |

| Conference Committee                       | xxi     |

| Technical Program Committee                | xxiv    |

| Reviewers                                  | xxvii   |

| Tutorial Committee                         | xxxii   |

| VLSI Design 2008 Fellowship Recipients     | xxxiii  |

| VLSI Design 2008 Awards                    | xxxviii |

| VLSI Design Conference History             | xxxix   |

| Embedded Systems Design Conference History | xl      |

| About the Cover                            | xli     |

| Invited Keynote Speakers                   | xlii    |

#### Invited Talks/Special Sessions Chair: Rajiv Kapur

| A Decade of Platform-Based Design: A Look Backwards, a Look Forwards<br>Grant Martin, Chief Scientist, Tensilica                | .3 |

|---------------------------------------------------------------------------------------------------------------------------------|----|

| Analog IC Design in Nanometer CMOS Technologies<br>Willy Sansen, K.U. Leuven Belgium                                            | .4 |

| Common Power Format: A User-driven Ecosystem for Proven Low Power Design Flows<br>Sumit DasGupta, Senior Vice President, Si2    | .5 |

| The Future of Low Power Design is Here: IEEE P1801, aka, UPF 2.0<br>Stephen Bailey, Director Product Marketing, Mentor Graphics | .6 |

| Making Sense Out of the Potential Babble of Low Power Standards<br>Gary Delp, Distinguished Engineer, LSI Corp                  | .7 |

| DFX and Productivity<br>Robert C Aitken, R&D Fellow, ARM                                                                        | .8 |

| Computational Lithography – Moore Bang for Your Buck<br>Vivek Singh, Senior Principal Engineer, Intel                           | .9 |

#### Made For India Forum

| Made For India Forum |  |

|----------------------|--|

| Chair: Rajiv Kapur   |  |

### VLSI Design Conference 2009 – Panels Chair: Rajiv Kapur

| IP Panel Topic: Why is Design Automation and Reuse of Analog Designs<br>Increasingly Trailing the Digital World?<br>Organizers: Ghasi Agarwal and Prakash Bare | 17 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| EDA Panel Topic: EDA Made-in-India: Fact or Fiction?<br>Organizers: Raman Santhanakrishnan and Yatin Trivedi                                                   | 18 |

| Made For India Panel Topic: Solutions for a Small Car – Made for India<br>and Made in India<br>Organizers: India Semiconductor Association                     | 19 |

| Embedded SW Panel Topic: Accelerating Embedded System Design<br>Organizers: Techonline                                                                         | 20 |

### Tutorials

| Defect Aware to Power Conscious Tests – The New DFT Landscape<br>Nilanjan Mukherjee, Janusz Rajski, and Jerzy Tyszer                                           | 23 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Techniques for the Design of Low Voltage Power Efficient Analog<br>and Mixed Signal Circuits<br>J. Ramirez-Angulo, Ramon G. Carvajal, and Antonio Lopez-Martin | 26 |

| Power Reduction Techniques and Flows at RTL and System Level<br>Anmol Mathur and Qi Wang                                                                       | 28 |

| Security and Dependability of Embedded Systems: A Computer Architects' Perspective<br>Jörg Henkel, Vijaykrishnan Narayanan, Sri Parameswaran, and Roshan Ragel | 30 |

| Design for Manufacturability and Reliability in Nano Era<br>Goutam Debnath and Paul Thadikaran                                                                 | 33 |

| Negative Feedback System and Circuit Design<br>Nagendra Krishnapura and Shanthi Pavan                                                                          | 35 |

| Synthesis and Testing for Low Power<br>Ajit Pal and Santanu Chattopadhyay                                                                                      | 37 |

| Power Management for Mobile Multimedia: From Audio to Video and Games<br>Samarjit Chakraborty and Ye Wang                                                      | 39 |

| Robust Circuit Design: Challenges and Solutions<br>Saurabh K. Tiwary, Amith Singhee, and Vikas Chandra                                                         | 41 |

#### Session 1A: Low Power Design for Wireless Communication

| Design-Space Exploration of Energy-Delay-Area Efficient Coarse-Grain<br>Reconfigurable Datapath                     | 45 |

|---------------------------------------------------------------------------------------------------------------------|----|

| Sohan Purohit, Marco Lanuzza, Stefania Perri, Pasquale Corsonello,<br>and Martin Margala                            |    |

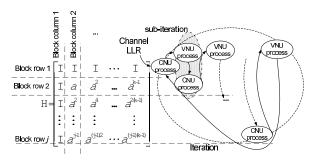

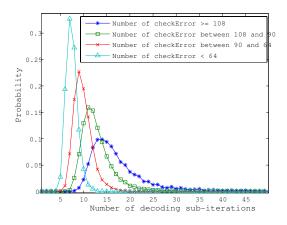

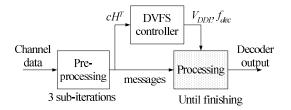

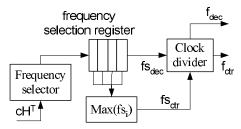

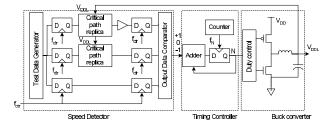

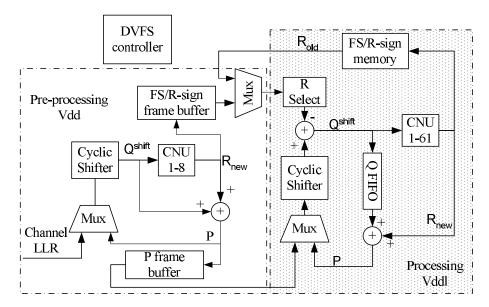

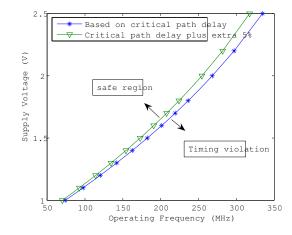

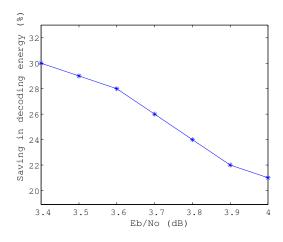

| Low-Power VLSI Design of LDPC Decoder Using DVFS for AWGN Channels<br>Weihuang Wang, Gwan Choi, and Kiran K. Gunnam | 51 |

| Environment and Process Adaptive Low Power Wireless Baseband Signal Processing<br>Using Dual Real-Time Feedback     | 57 |

| Muhammad Mudassar Nisar and Abhijit Chatterjee                                                                      |    |

#### Session 1B: SoC Verification

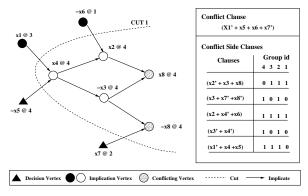

| Efficient Techniques for Directed Test Generation Using Incremental Satisfiability<br>Prabhat Mishra and Mingsong Chen                           | .65 |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Inline Assertions – Embedding Formal Properties in a Test Bench<br>Aritra Hazra, Priyankar Ghosh, Pallab Dasgupta, and Partha Pratim Chakrabarti | .71 |

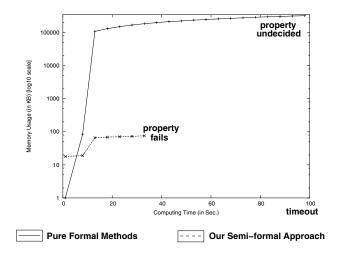

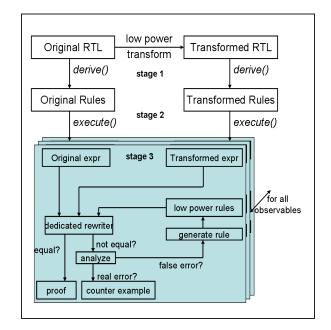

| Dedicated Rewriting: Automatic Verification of Low Power Transformations in RTL<br>Vinod Viswanath, Shobha Vasudevan, and Jacob A. Abraham       | .77 |

#### Session 1C: Fault Diagnosis

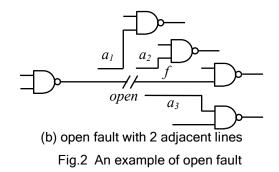

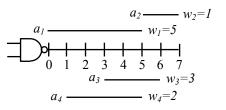

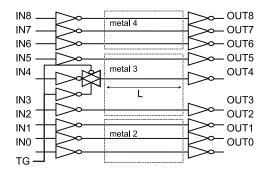

| A Novel Approach for Improving the Quality of Open Fault Diagnosis<br>Koji Yamazaki, Toshiyuki Tsutsumi, Hiroshi Takahashi, Yoshinobu Higami,<br>Takashi Aikyo, Yuzo Takamatsu, Hiroyuki Yotsuyanagi, and Masaki Hashizume          | 85 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

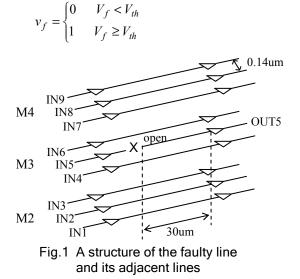

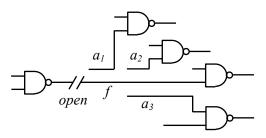

| Fault Effect of Open Faults Considering Adjacent Signal Lines in a 90 nm IC<br>Hiroyuki Yotsuyanagi, Masaki Hashizume, Toshiyuki Tsutsumi, Koji Yamazaki,<br>Takashi Aikyo, Yoshinobu Higami, Hiroshi Takahashi, and Yuzo Takamatsu | 91 |

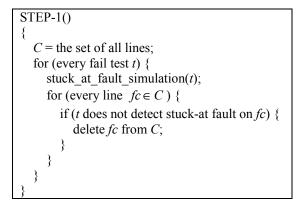

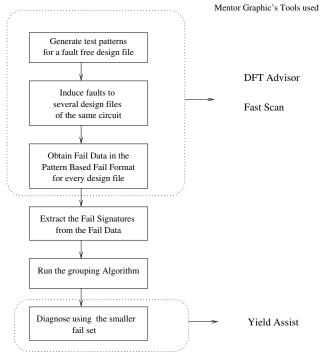

| Efficient Grouping of Fail Chips for Volume Yield Diagnostics<br>Lavanya Jagan, Ratan Deep Singh, V. Kamakoti, and Ananta K. Majhi                                                                                                  | 97 |

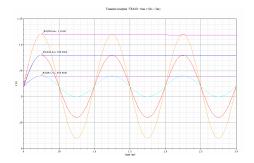

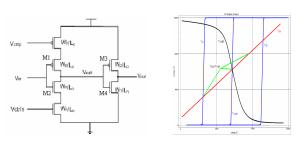

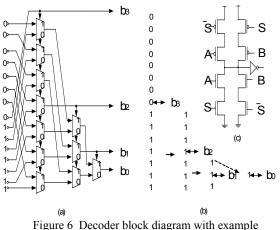

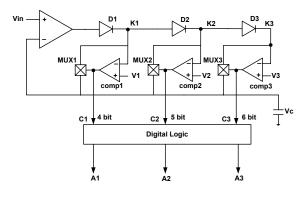

# Session 2A: Analog and Mixed Signal I

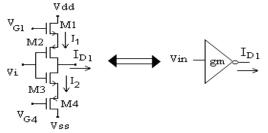

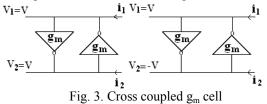

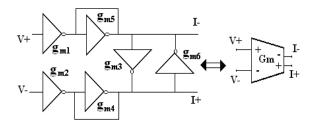

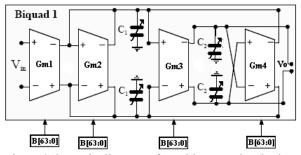

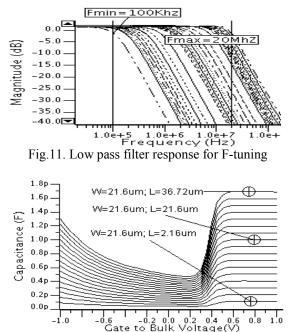

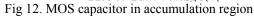

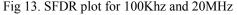

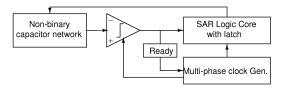

| 100KHz-20MHz Programmable Subthreshold G <sub>m</sub> -C Low-Pass Filter<br>in 0.18µ-m CMOS   | 105 |

|-----------------------------------------------------------------------------------------------|-----|

| S. Ramasamy, B. Venkataramani, R. Niranjini, and K. Suganya                                   |     |

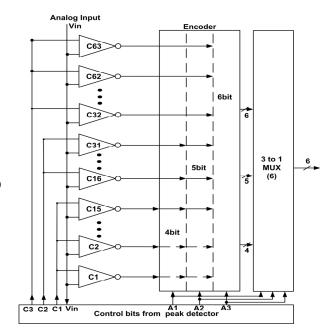

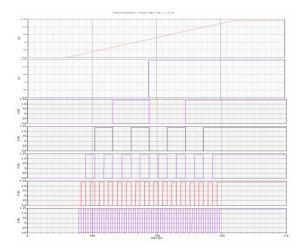

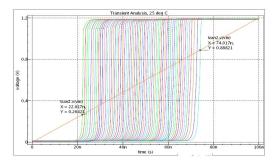

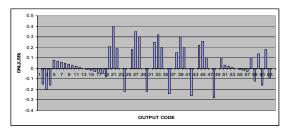

| A 20MS/s 5.6 mW 6b Asynchronous ADC in 0.6μm CMOS<br>Theja Tulabandhula and Yujendra Mitikiri | 111 |

| Design of a Low Power, Variable-Resolution Flash ADC                                          | 117 |

| Sreehari Veeramachanen, A. Mahesh Kumar, Venkat Tummala, and M.B. Srinivas                    |     |

# Session 2B: Floorplanning and Analog Layout

| Floorplanning for Partial Reconfiguration in FPGAs                    |

|-----------------------------------------------------------------------|

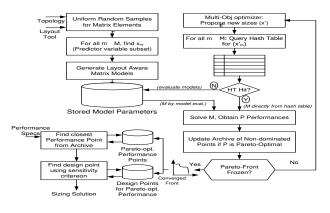

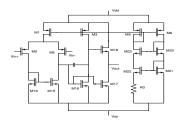

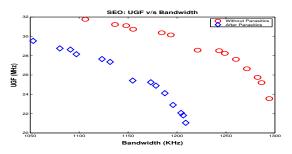

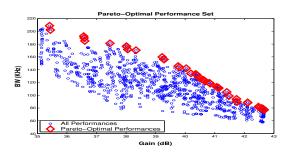

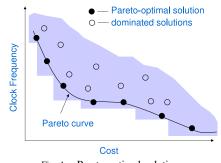

| Efficient Synthesis of a Uniformly Spread Layout Aware Pareto Surface |

| for Analog Circuits                                                   |

| Almitra Pradhan and Ranga Vemuri                                      |

| Efficient Analog/RF Layout Closure with Compaction Based Legalization |

# Session 2C: Network on Chip

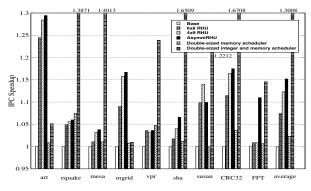

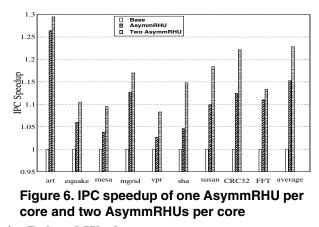

| Improving Scalability and Per-core Performance in Multi-cores through Resource Sharing<br>and Reconfiguration                                                                                                                              | 145 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

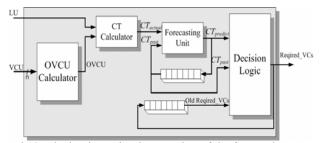

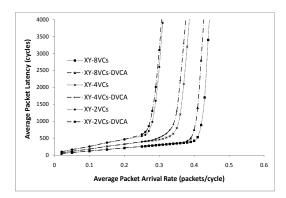

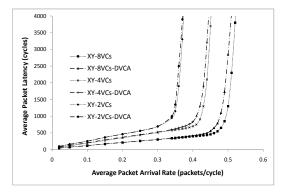

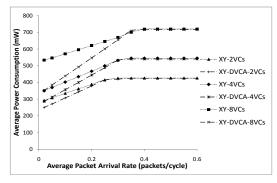

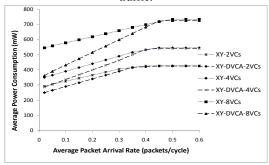

| Tameesh Suri and Aneesh Aggarwal<br>Forecasting-Based Dynamic Virtual Channels Allocation for Power Optimization<br>of Network-on-Chips<br>Amir-Mohammad Rahmani, Masoud Daneshtalab, Ali Afzali-Kusha, Saeed Safari,<br>and Masoud Pedram | 151 |

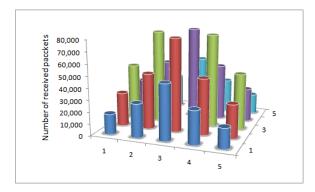

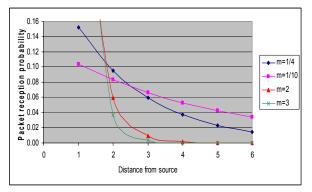

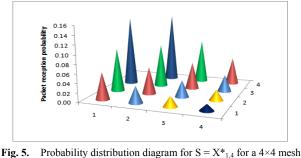

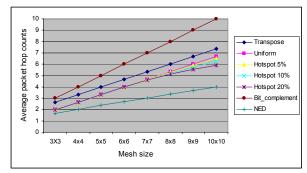

| Negative Exponential Distribution Traffic Pattern for Power/Performance Analysis<br>of Network on Chips<br><i>Amir-Mohammad Rahmani, Iman Kamali, Pejman Lotfi-Kamran, Ali Afzali-Kusha,</i><br><i>and Saeed Safari</i>                    | 157 |

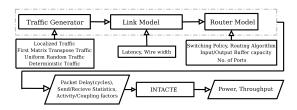

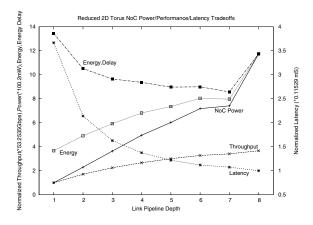

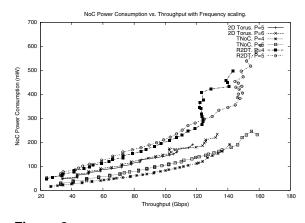

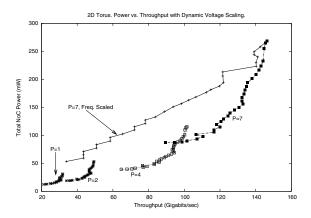

| Latency, Power and Performance Trade-offs in Network-on-Chips<br>by Link Microarchitecture Exploration<br>Basavaraj Talwar, Shailesh Kulkarni, and Bharadwaj Amrutur                                                                       |     |

# Session 3A: Low Power Device Technology

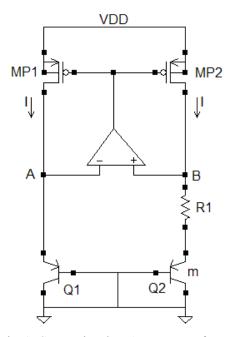

| A Low Voltage CMOS Proportional-to-Absolute Temperature Current Reference<br>Sanjay Kumar Wadhwa                                                      | .171 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Novel MOS Decoupling Capacitor Optimization Technique for Nanotechnologies<br>Bardia Bozorgzadeh and Ali Afzali-Kusha                                 | .175 |

| Switched-Capacitor Based Buck Converter Design Using Current Limiter<br>for Better Efficiency and Output Ripple<br><i>Tamal Das and Pradip Mandal</i> | .181 |

# Session 3B: System Synthesis

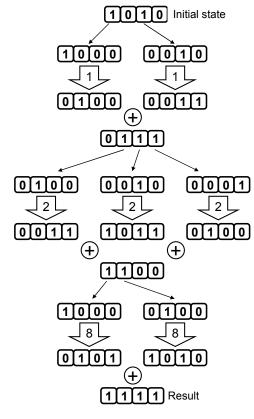

| Reversible Logic Synthesis with Output Permutation<br>Robert Wille, Daniel Große, Gerhard W. Dueck, and Rolf Drechsler           | .189 |

|----------------------------------------------------------------------------------------------------------------------------------|------|

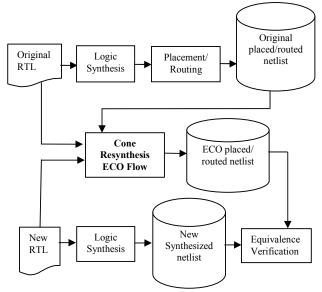

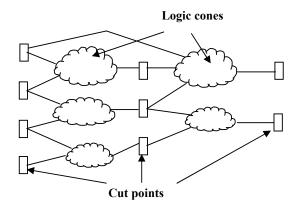

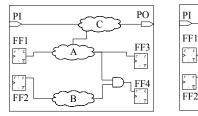

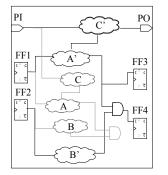

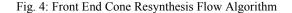

| Cone Resynthesis ECO Methodology for Multi-Million Gate Designs<br>Suresh Raman and Mike Lubyanitsky                             | .195 |

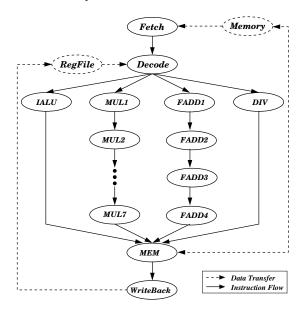

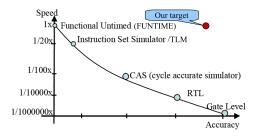

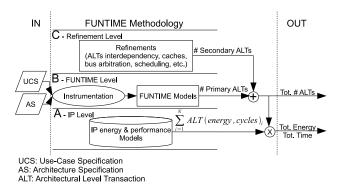

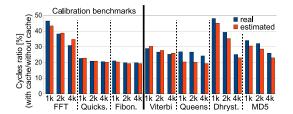

| A General Approach to High-Level Energy and Performance Estimation in SoCs<br>Sandro Penolazzi, Ahmed Hemani, and Luca Bolognino | .200 |

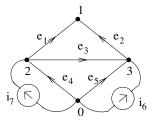

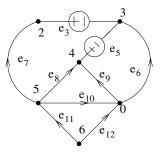

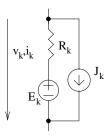

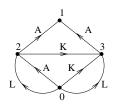

| Exploiting Hybrid Analysis in Solving Electrical Networks<br>V. Siva Sankar, H. Narayanan, and Sachin B. Patkar                  | .206 |

# Session 3C: Test Generation

| The Effect of Filling the Unspecified Values of a Test Set on the Test Set Quality<br>Irith Pomeranz and Sudhakar M. Reddy   | .215 |

|------------------------------------------------------------------------------------------------------------------------------|------|

| New Techniques for Accelerating Small Delay ATPG and Generating<br>Compact Test Sets<br>Boxue Yin, Dong Xiang, and Zhen Chen | .221 |

| TIGUAN: Thread-Parallel Integrated Test Pattern Generator Utilizing                                                          | .227 |

| An ILP Based ATPG Technique for Multiple Aggressor Crosstalk Faults Considering<br>the Effects of Gate Delays                | .233 |

# Session 4A: Advanced Device Modeling

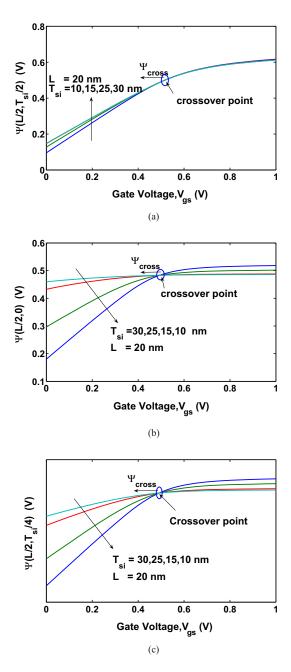

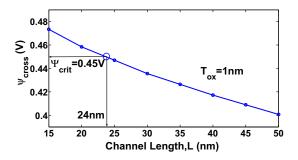

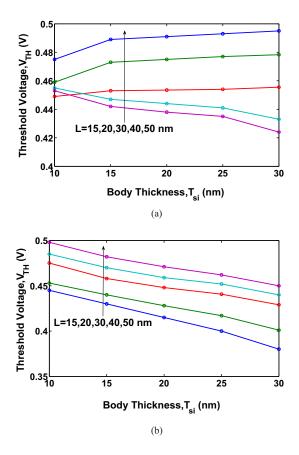

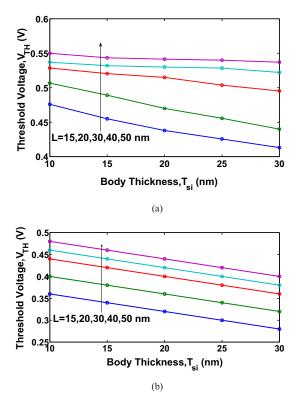

| Concept of "Crossover Point" and its Application on Threshold Voltage Definition     |     |

|--------------------------------------------------------------------------------------|-----|

| for Undoped-Body Transistors                                                         | 241 |

| Ratul Kumar Baruah and Santanu Mahapatra                                             |     |

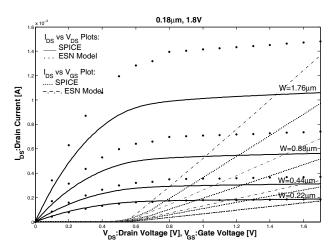

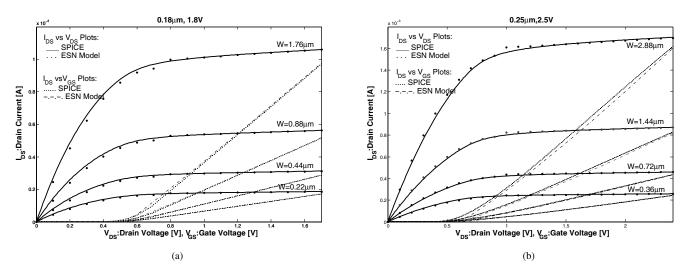

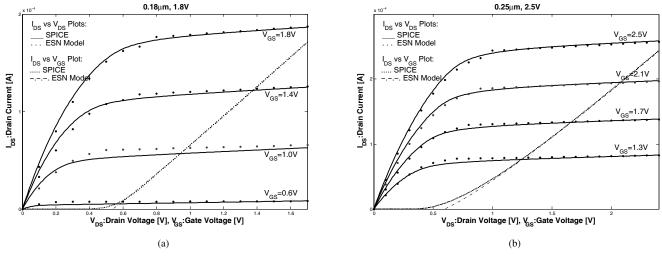

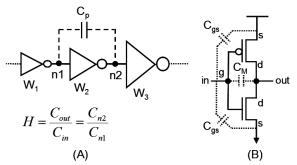

| Extended-Sakurai-Newton MOSFET Model for Ultra-Deep-Submicrometer                    |     |

| CMOS Digital Design                                                                  | 247 |

| Nishant Chandra, Apoorva Kumar Yati, and A.B. Bhattacharyya                          |     |

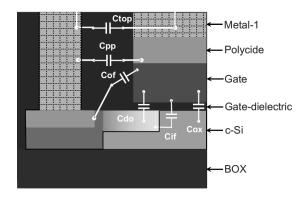

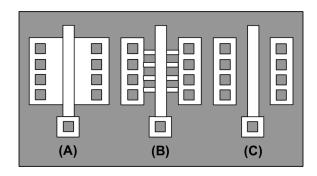

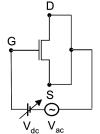

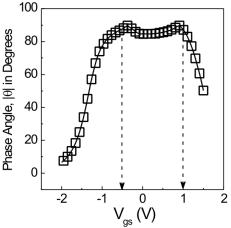

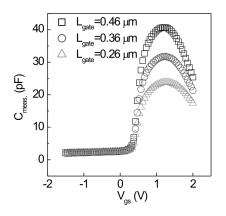

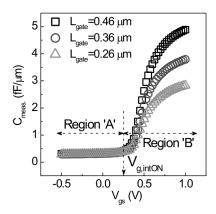

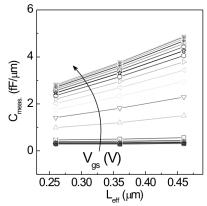

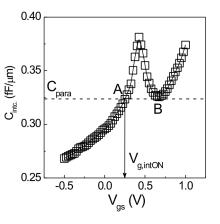

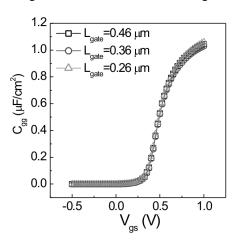

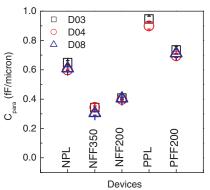

| Measurement and Analysis of Parasitic Capacitance in FinFETs with High-k Dielectrics |     |

| and Metal-Gate Stack                                                                 | 253 |

| Abhisek Dixit, Anirban Bandhyopadhyay, Nadine Collaert, Kristin De Meyer,            |     |

| and Malgorzata Jurczak                                                               |     |

# Session 4B: Application-Specific Architectures and Reconfigurable Computing

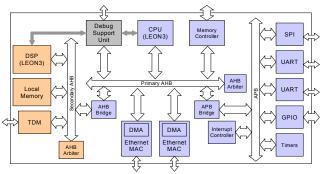

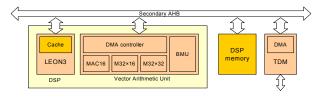

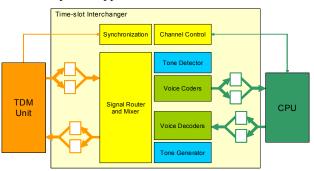

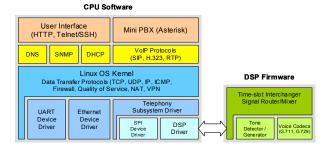

| Design, Implementation and Validation of an Open Source IP-PBX/VoIP Gateway SoC<br>Spyros Apostolacos, George Lykakis, Apostolos Meliones, Vassilis Vlagoulis,<br>Emmanuel Touloupis, and George Konstantoulakis | .261 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

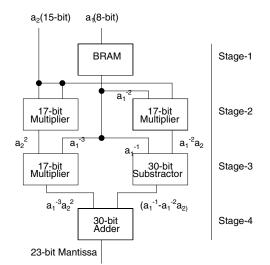

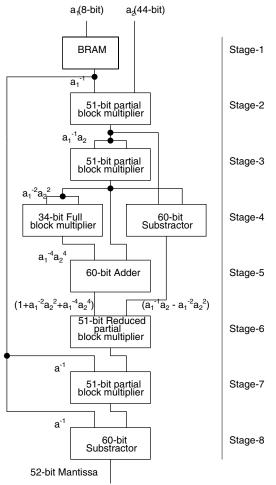

| Efficient Implementation of Floating-Point Reciprocator on FPGA                                                                                                                                                  | .267 |

#### Invited Talk

| ReConfigurable Technologies | 272 |

|-----------------------------|-----|

| Mona Mathur                 |     |

#### Session 4C: Embedded Systems I

| High-Speed On-Chip Event Counters for Embedded Systems<br>Nilanjan Mukherjee, Artur Pogiel, Janusz Rajski, and Jerzy Tyszer | 275 |

|-----------------------------------------------------------------------------------------------------------------------------|-----|

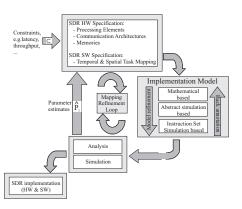

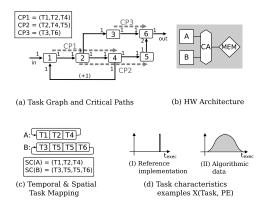

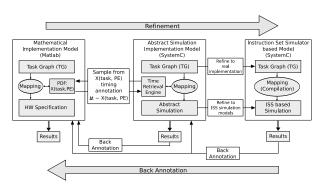

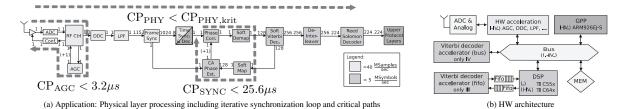

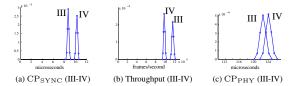

| A Workbench for Analytical and Simulation Based Design Space Exploration                                                    | 001 |

| of Software Defined Radios<br>T. Kempf, S. Wallentowitz, G. Ascheid, R. Leupers, and H. Meyr                                | 281 |

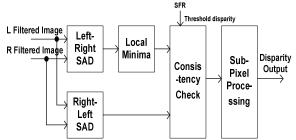

| Improved-Quality Real-Time Stereo Vision Processor<br>Sang-Kyo Han, SeongHoon Woo, Mun-Ho Jeong, and Bum-Jae You            | 287 |

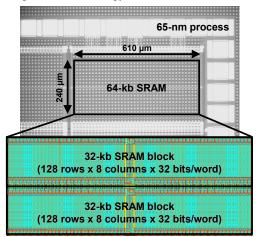

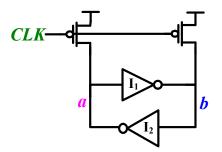

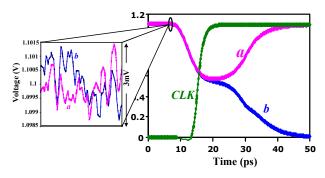

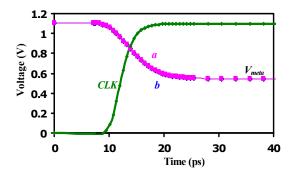

### Session 5A: SRAM and Random Number Generation

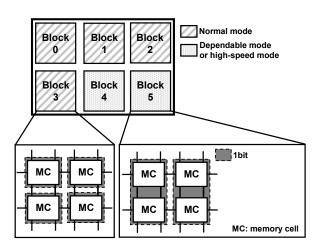

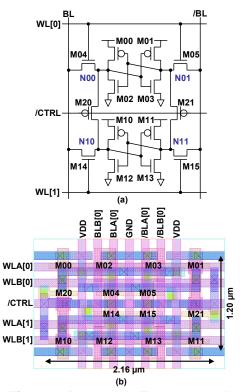

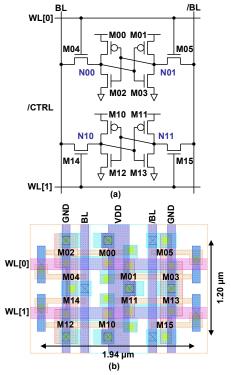

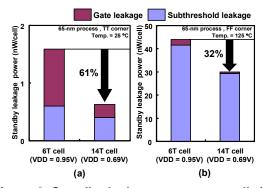

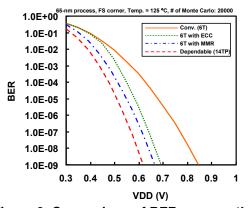

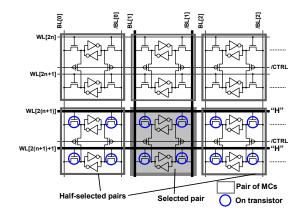

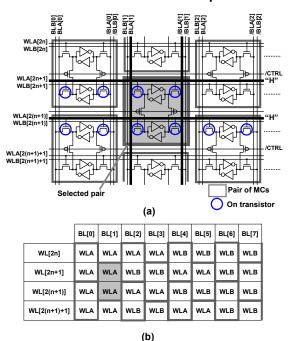

| A 7T/14T Dependable SRAM and its Array Structure to Avoid Half Selection<br>Hidehiro Fujiwara, Shunsuke Okumura, Yusuke Iguchi, Hiroki Noguchi, Hiroshi Kawaguchi,<br>and Masahiko Yoshimoto             | 295 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

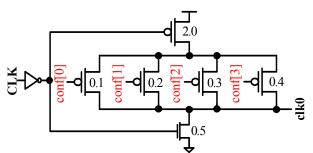

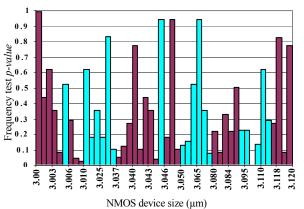

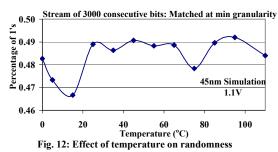

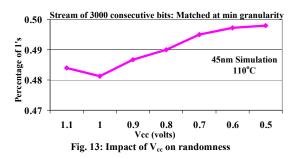

| A 4Gbps 0.57pJ/bit Process-Voltage-Temperature Variation Tolerant All-Digital<br>True Random Number Generator in 45nm CMOS<br>Suresh Srinivasan, Sanu Mathew, Vasantha Erraguntla, and Ram Krishnamurthy | 301 |

| Single Ended Static Random Access Memory for Low-V <sub>dd</sub> , High-Speed<br>Embedded Systems<br>Jawar Singh, Jimson Mathew, Saraju P. Mohanty, and Dhiraj K. Pradhan                                | 307 |

#### Session 5B: Secure VLSI Design

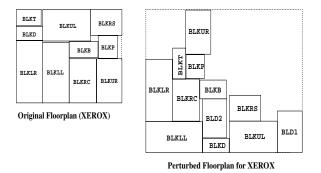

| Encoding of Floorplans through Deterministic Perturbation<br>Debasri Saha and Susmita Sur-Kolay                         | .315 |

|-------------------------------------------------------------------------------------------------------------------------|------|

| Design Optimization and Automation for Secure Cryptographic Circuits<br>Kuan Jen Lin, Yi Tang Chiu, and Shan Chien Fang | .321 |

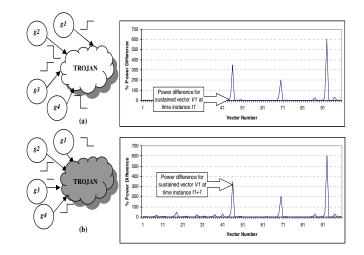

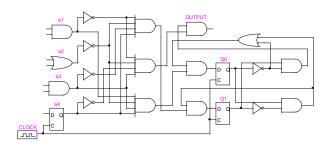

| A Novel Sustained Vector Technique for the Detection of Hardware Trojans<br>Mainak Banga and Michael S. Hsiao           | .327 |

| Session 5C: Embedded Systems II                                                                                                             |      |

|---------------------------------------------------------------------------------------------------------------------------------------------|------|

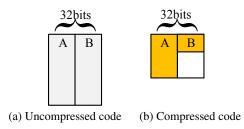

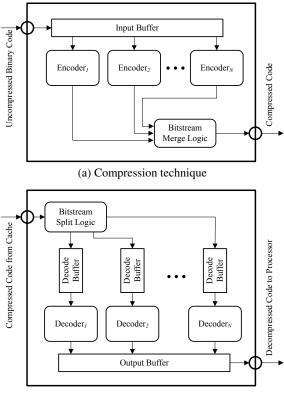

| Efficient Placement of Compressed Code for Parallel Decompression<br>Xiaoke Qin and Prabhat Mishra                                          | .335 |

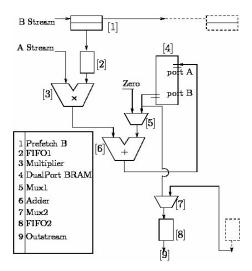

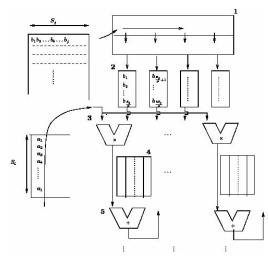

| FPGA Based High Performance Double-Precision Matrix Multiplication<br>Vinay B.Y. Kumar, Siddharth Joshi, Sachin B. Patkar, and H. Narayanan | 341  |

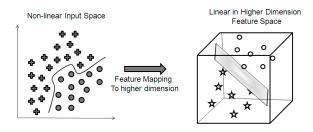

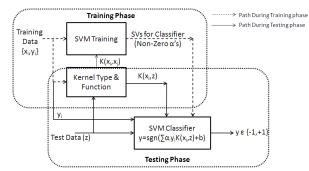

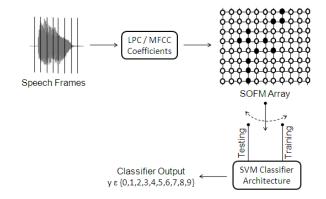

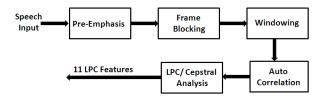

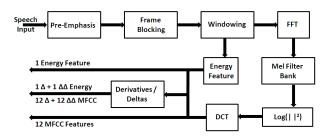

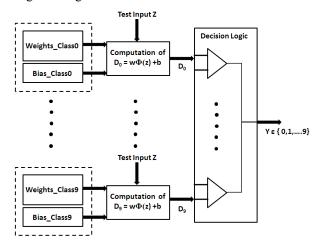

| FPGA Implementation of Support Vector Machine Based Isolated Digit Recognition System<br>J. Manikandan, B. Venkataramani, and V. Avanthi    | 347  |

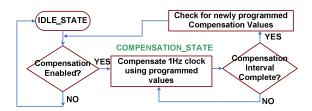

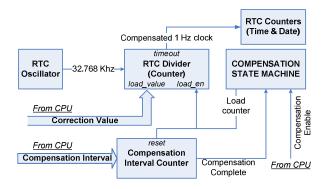

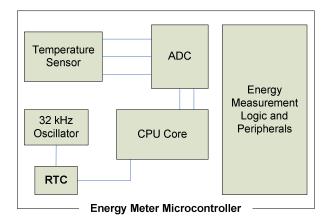

| A "Stitch" in Time: Accurate Timekeeping with On-Chip Compensation<br>Prashant Bhargava and Mohit Arora                                     | 353  |

# Session 6A: Analog and Mixed Signal II

| Systematic Methodology for High-Level Performance Modeling of Analog Systems<br>Soumya Pandit, Chittaranjan Mandal, and Amit Patra                                                                                                                           | .361 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

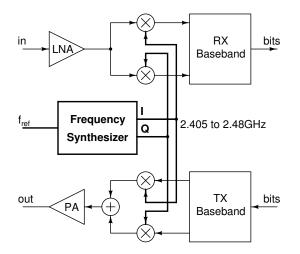

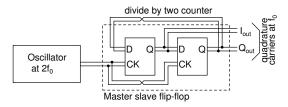

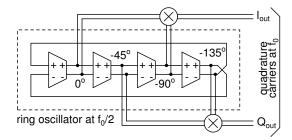

| A Comparison of Approaches to Carrier Generation for Zigbee Transceivers<br>Leburu Manojkumar, Arun Mohan, and Nagendra Krishnapura                                                                                                                          | .367 |

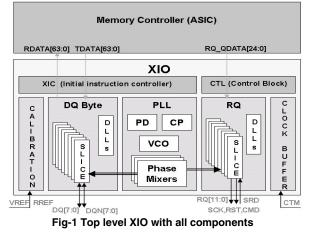

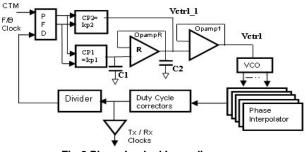

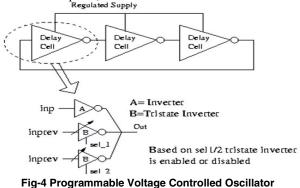

| A 2.4Gbps-4.8Gbps XDR-DRAM I/O (XIO) Link<br>Vijay Khawshe, Kapil Vyas, Renu Rangnekar, Prateek Goyal, Vijay Krishna,<br>Kashinath Prabhu, Pravin Kumar Venkatesan, Leneesh Raghavan, Rajkumar Palwai,<br>Thrivikraman M, Kunal Desai, and Abhijit Abhyankar | .373 |

# Session 6B: Routing, Power Optimization

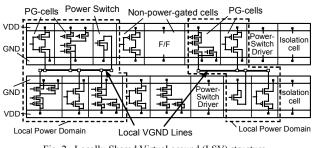

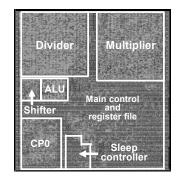

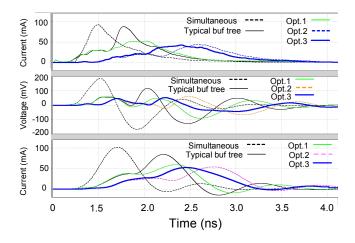

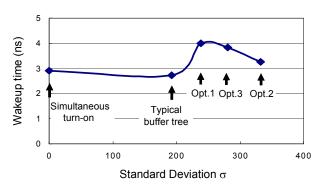

| Design and Implementation of Fine-Grain Power Gating with Ground Bounce Suppression | .381 |

|-------------------------------------------------------------------------------------|------|

| Kimiyoshi Usami, Toshiaki Shirai, Tasunori Hashida, Hiroki Masuda, Seidai Takeda,   |      |

| Mitsutaka Nakata, Naomi Seki, Hideharu Amano, Mitaro Namiki, Masashi Imai,          |      |

| Masaaki Kondo, and Hiroshi Nakamura                                                 |      |

| A Method for the Multi-net Multi-pin Routing Problem with Layer Assignment          | .387 |

| Tuhina Samantam, Hafizur Rahaman, Prasun Ghosal, and Parthasarathi Dasgupta         |      |

| A New Hardware Routing Accelerator for Multi-Terminal Nets                          | .393 |

| Kaleem Fatima and Rameshwar Rao                                                     |      |

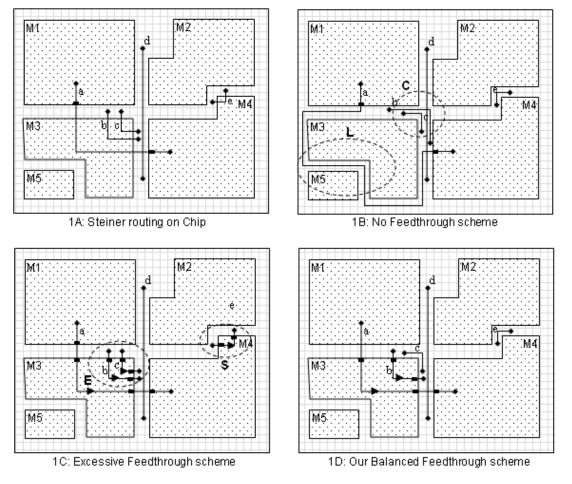

| Simultaneous Routing and Feedthrough Algorithm to Decongest Top Channel             | .399 |

| Shashank Prasad and Anuj Kumar                                                      |      |

# Session 6C: Low Power Design

| Metric Based Multi-Timescale Control for Reducing Power in Embedded Systems                 | 407 |

|---------------------------------------------------------------------------------------------|-----|

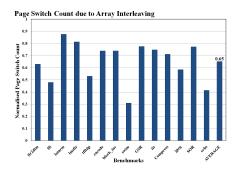

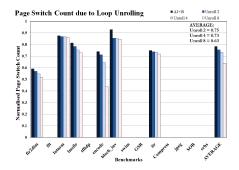

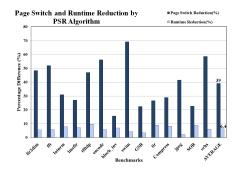

| Code Transformations for TLB Power Reduction                                                | 413 |

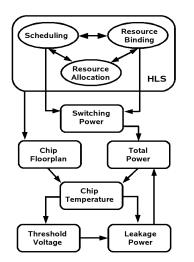

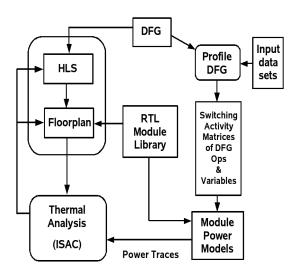

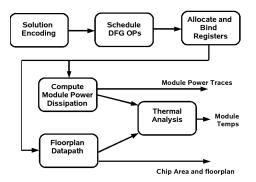

| Simultaneous Peak Temperature and Average Power Minimization<br>during Behavioral Synthesis | 419 |

# Session 7A: Analog and Mixed Signal III

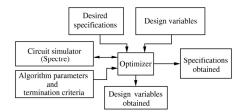

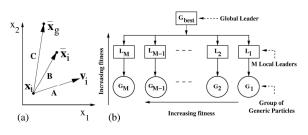

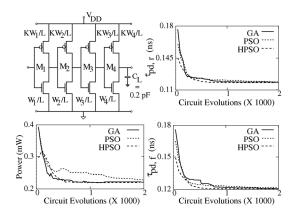

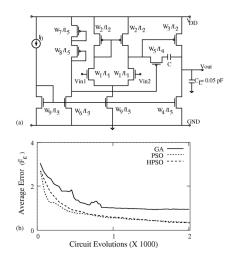

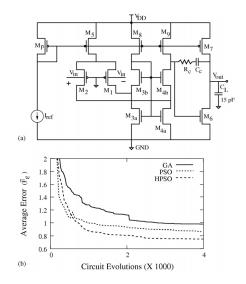

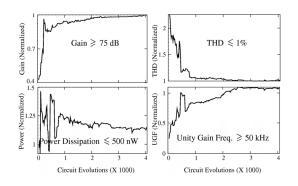

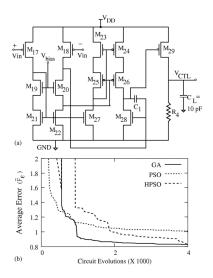

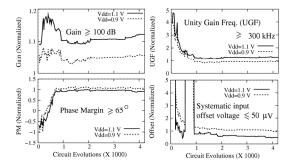

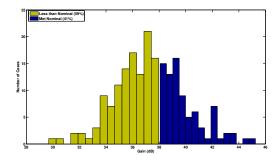

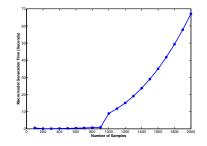

| Low-Power Low-Voltage Analog Circuit Design Using Hierarchical<br>Particle Swarm Optimization                                                                                                      | .427 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Rajesh Amratlal Thakker, M. Shojaei Baghini, and Mahesh B. Patil                                                                                                                                   |      |

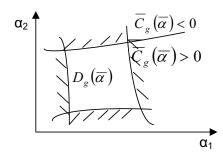

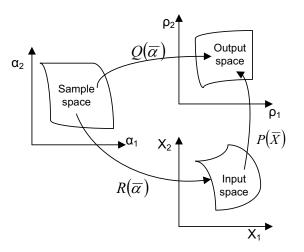

| Variation-Aware Macromodeling and Synthesis of Analog Circuits Using Spline Center<br>and Range Method and Dynamically Reduced Design Space<br>Shubhankar Basu, Balaji Kommineni, and Ranga Vemuri | .433 |

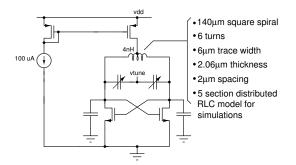

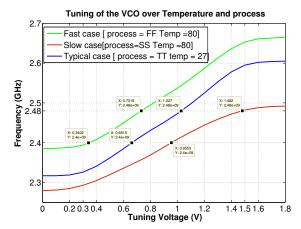

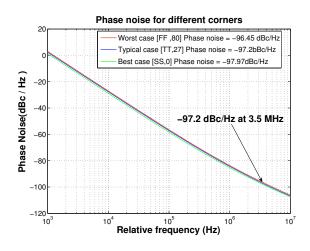

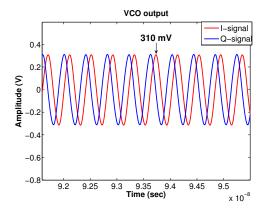

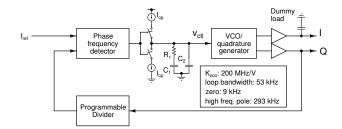

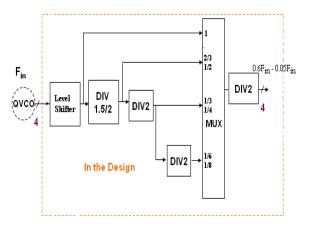

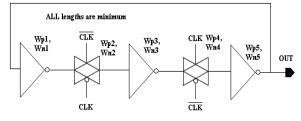

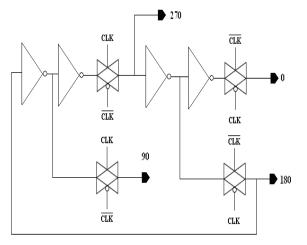

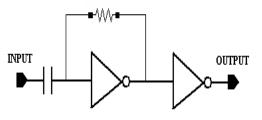

| A Low Power Architecture to Extend the Tuning Range of a Quadrature Clock<br>Ramen Dutta and T.K. Bhattacharyya                                                                                    | .439 |

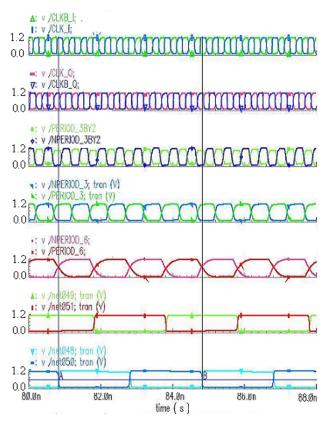

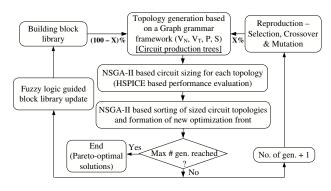

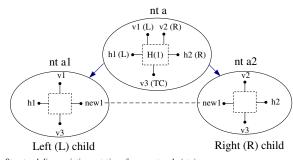

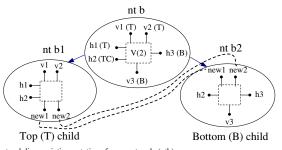

| Fuzzy Logic Based Guidance to Graph Grammar Framework for Automated<br>Analog Circuit Design                                                                                                       | 445  |

| Angan Das and Ranga Vemuri                                                                                                                                                                         |      |

#### Session 7B: Reliability and Design Space Exploration

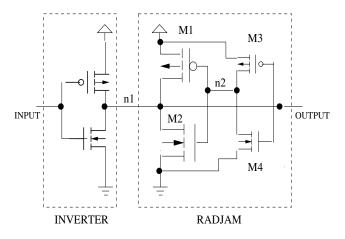

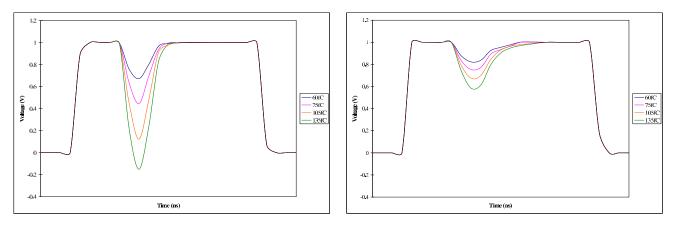

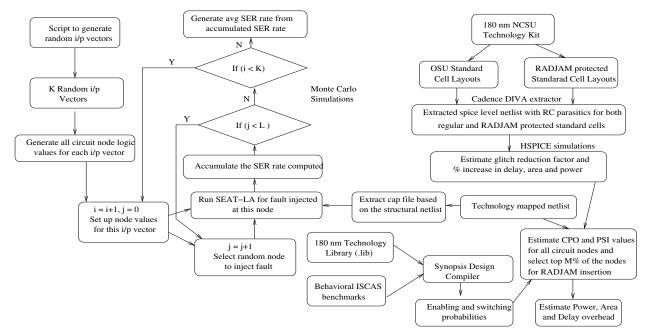

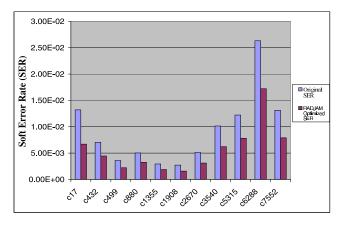

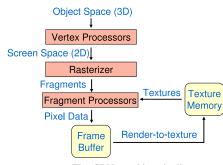

| RADJAM: A Novel Approach for Reduction of Soft Errors in Logic Circuits                   |

|-------------------------------------------------------------------------------------------|

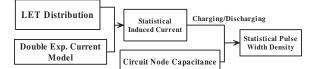

| Soft Error Rates with Inertial and Logical Masking                                        |

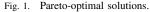

| Accelerating System-Level Design Tasks Using Commodity Graphics Hardware:<br>A Case Study |

#### Session 7C: BIST, Error Modeling

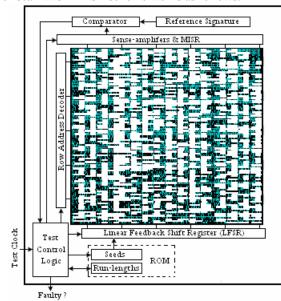

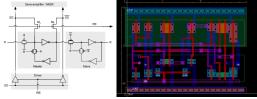

| Built in Self Test Based Design of Wave-Pipelined Circuits in ASICs                                |

|----------------------------------------------------------------------------------------------------|

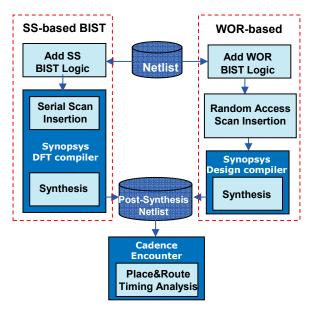

| WOR-BIST: A Complete Test Solution for Designs Meeting Power, Area<br>and Performance Requirements |

| Chunhua Yao, Kewal K. Saluja, and Abhishek A. Sinkar                                               |

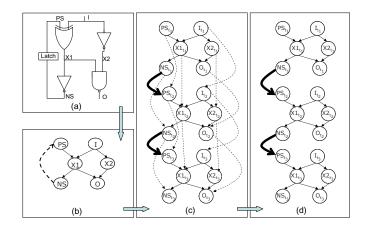

| An Error Model to Study the Behavior of Transient Errors in Sequential Circuits                    |

#### Session 8A: Advanced Nanodevice Modeling

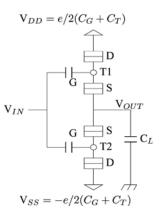

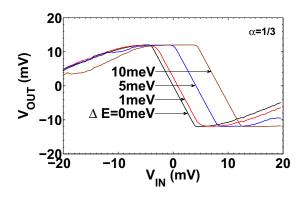

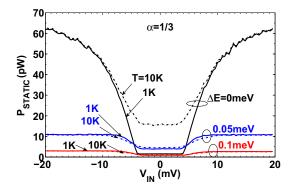

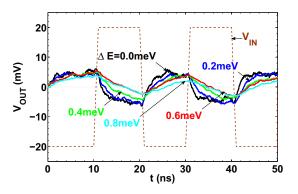

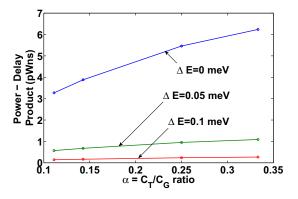

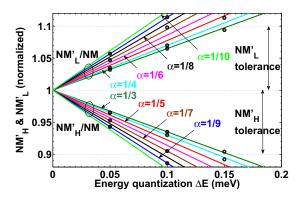

| Analysis of the Energy Quantization Effects on Single Electron Inverter Performance<br>through Noise Margin Modeling<br>Surya Shankar Dan and Santanu Mahapatra | .493 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

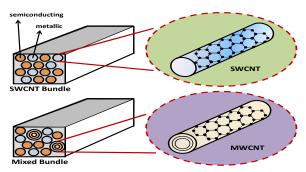

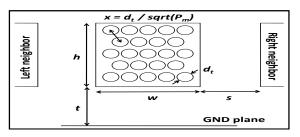

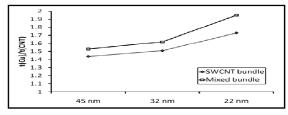

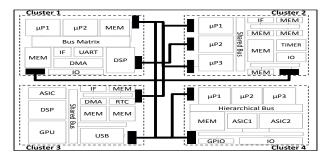

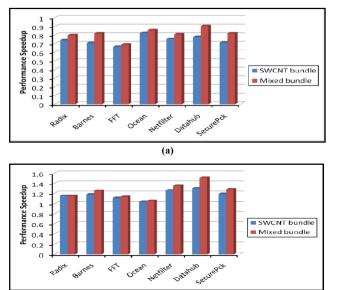

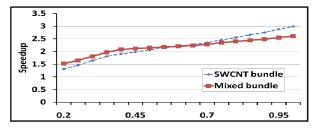

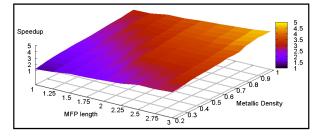

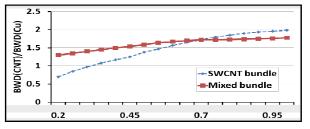

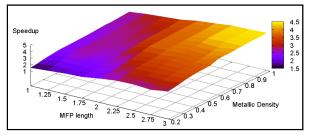

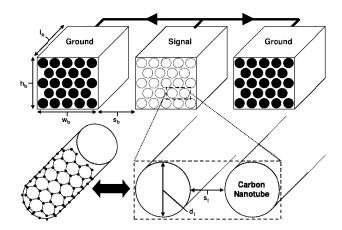

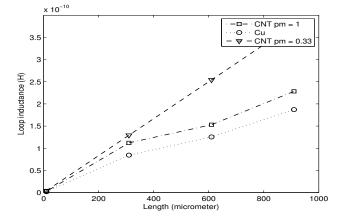

| Exploring Carbon Nanotube Bundle Global Interconnects<br>for Chip Multiprocessor Applications<br>Sudeep Pasricha, Nikil Dutt, and Fadi J. Kurdahi               | .499 |

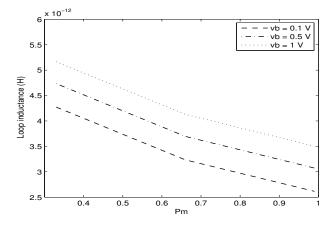

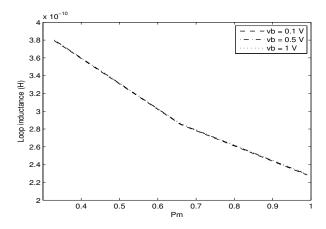

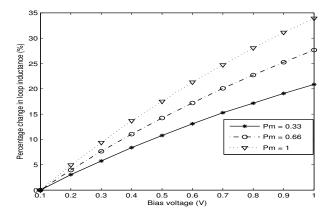

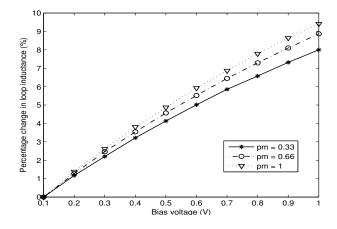

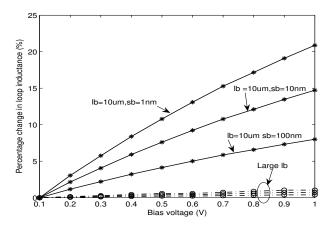

| Impact of Bias Voltage on Magnetic Inductance of Carbon Nanotube Interconnects<br>K.C. Narasimhamurthy and Roy P. Paily                                         | 505  |

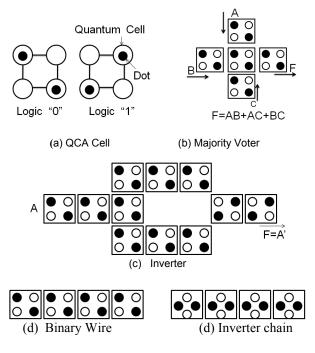

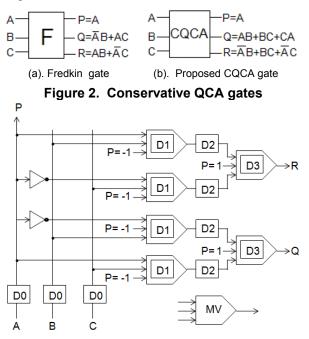

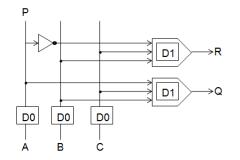

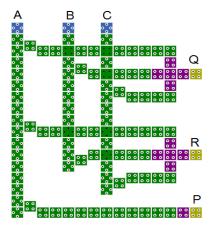

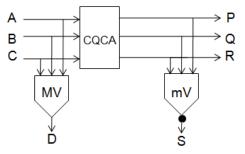

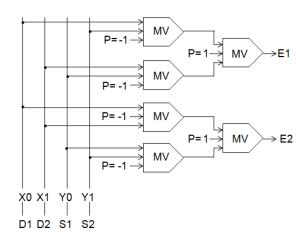

| Conservative QCA Gate (CQCA) for Designing Concurrently Testable<br>Molecular QCA Circuits<br><i>Himanshu Thapliyal and Nagarajan Ranganathan</i>               | .511 |

#### Session 8B: Timing Analysis and Optimization

| An Approach to Measure the Performance Impact of Dynamic Voltage Fluctuations<br>Using Static Timing Analysis | 519 |

|---------------------------------------------------------------------------------------------------------------|-----|

| Ramamurthy Vishweshwara, Ramakrishnan Venkatraman, Udayakumar H,<br>and Arvind N V                            |     |

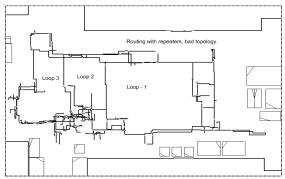

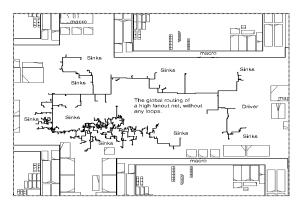

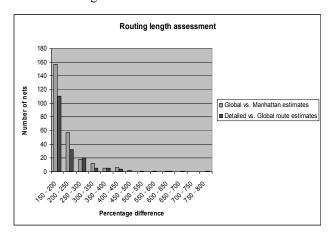

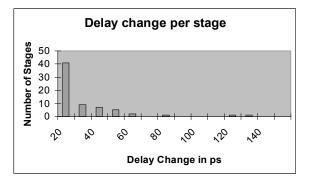

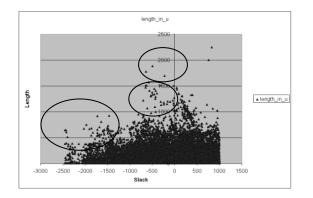

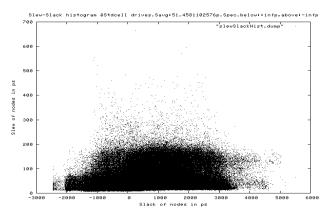

| Optimisation Quality Assessment in Large, Complex SoC Designs –<br>Challenges and Solutions                   |     |

| R. Venkatraman, Shrikrishna Pundoor, Arun Koithyar, Madhusudan Rao,<br>and Jagdish C. Rao                     |     |

#### **Invited Talk**

| Unified Challenges in Nano-CMOS High-Level Synthesis |  |

|------------------------------------------------------|--|

| Saraju P. Mohanty                                    |  |

#### Session 8C: Processor Design and Scheduling

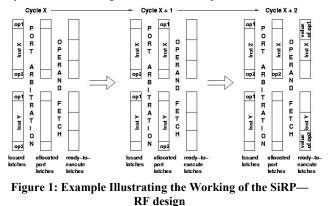

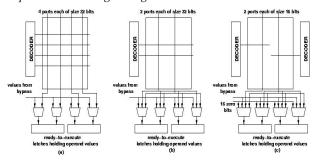

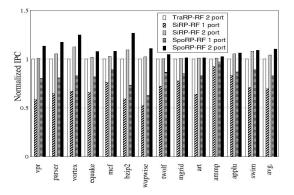

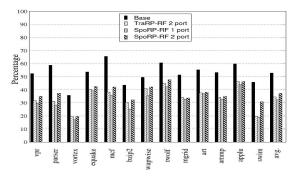

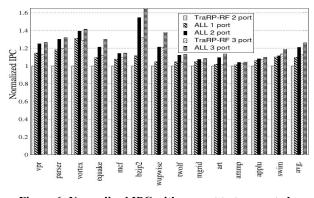

| Exploring the Limits of Port Reduction in Centralized Register Files<br>Sandeep Sirsi and Aneesh Aggarwal                       | .535 |

|---------------------------------------------------------------------------------------------------------------------------------|------|

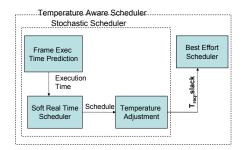

| Temperature Aware Scheduling for Embedded Processors<br>Ramkumar Jayaseelan and Tulika Mitra                                    | .541 |

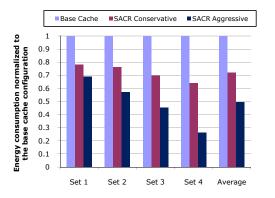

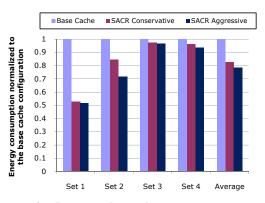

| SACR: Scheduling-Aware Cache Reconfiguration for Real-Time Embedded Systems<br>Weixun Wang, Prabhat Mishra, and Ann Gordon-Ross | .547 |

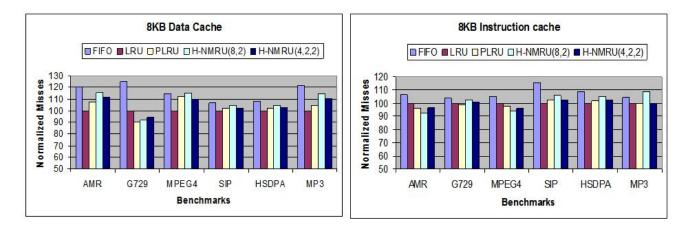

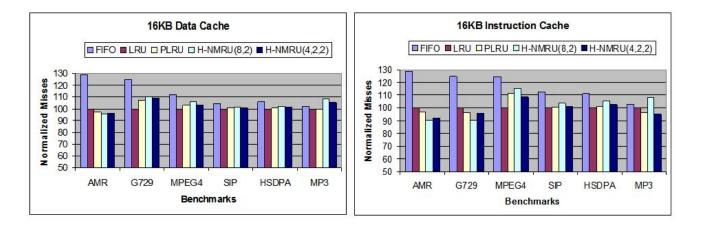

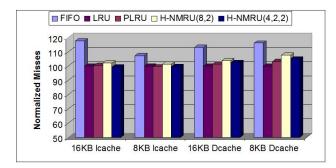

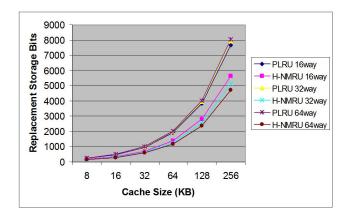

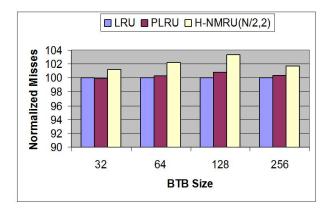

| H-NMRU: A Low Area, High Performance Cache Replacement Policy<br>for Embedded Processors<br>Sourav Roy                          | .553 |

#### Session 9A: VLSI Education

| Infrastructures for Education, Research and Industry in Microelectronics –    |   |

|-------------------------------------------------------------------------------|---|

| A Look Worldwide and a Look at India                                          | _ |

| B. Courtois, K. Torki, S. Dumont, S. Eyraud, J-F Paillotin, and G. di Pendina |   |

# Session 9B: Invited Paper-Phase Locked Loops

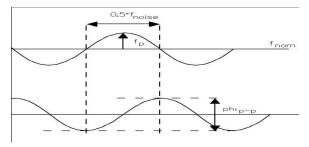

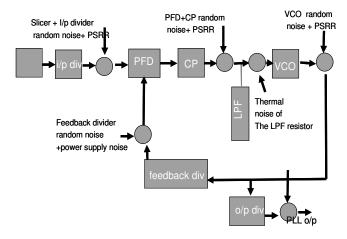

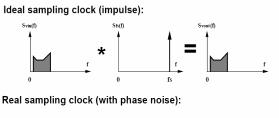

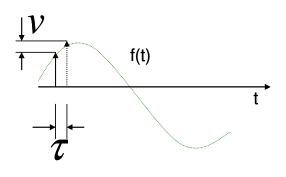

| Specification Driven Design of Phase Locked Loops     |  |

|-------------------------------------------------------|--|

| Prakash Easwaran, Prasenjit Bhowmik, and Rupak Ghayal |  |

|                                                       |  |

# Session 9C: Invited Paper-Design for Variations

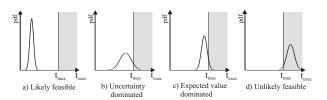

| Coping with Variations through System-Level Design                              | 581 |

|---------------------------------------------------------------------------------|-----|

| Nilanjan Banerjee, Saumya Chandra, Swaroop Ghosh, Sujit Dey, Anand Raghunathan, |     |

| and Kaushik Roy                                                                 |     |

|                                                                                 |     |

| Author Index                                                                    | 587 |

# VLSI Design 2009

# 22nd International Conference on VLSI Design

# Held jointly with 8th International Conference on Embedded Systems

New Delhi, India

5-9 January 2009

Technical Co-Sponsorship IEEE Circuits and Systems Society IEEE Solid State Circuits Society IEEE Electron Devices Society

Sponsored by VLSI Society of India

Sister Conference IEEE/ACM Design Automation Conference

Los Alamitos, California Washington • Tokyo

Copyright © 2009 by The Institute of Electrical and Electronics Engineers, Inc.

All rights reserved.

*Copyright and Reprint Permissions*: Abstracting is permitted with credit to the source. Libraries may photocopy beyond the limits of US copyright law, for private use of patrons, those articles in this volume that carry a code at the bottom of the first page, provided that the per-copy fee indicated in the code is paid through the Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923.

Other copying, reprint, or republication requests should be addressed to: IEEE Copyrights Manager, IEEE Service Center, 445 Hoes Lane, P.O. Box 133, Piscataway, NJ 08855-1331.

The papers in this book comprise the proceedings of the meeting mentioned on the cover and title page. They reflect the authors' opinions and, in the interests of timely dissemination, are published as presented and without change. Their inclusion in this publication does not necessarily constitute endorsement by the editors, the IEEE Computer Society, or the Institute of Electrical and Electronics Engineers, Inc.

IEEE Computer Society Order Number P3506 BMS Part Number CFP09041-PRT ISBN 978-0-7695-3506-7 ISSN Number 1063-9667

Additional copies may be ordered from:

IEEE Computer Society Customer Service Center 10662 Los Vaqueros Circle P.O. Box 3014 Los Alamitos, CA 90720-1314 Tel: + 1 800 272 6657 Fax: + 1 714 821 4641 http://computer.org/cspress csbooks@computer.org IEEE Service Center 445 Hoes Lane P.O. Box 1331 Piscataway, NJ 08855-1331 Tel: + 1 732 981 0060 Fax: + 1 732 981 9667 http://shop.ieee.org/store/ customer-service@ieee.org IEEE Computer Society Asia/Pacific Office Watanabe Bldg., 1-4-2 Minami-Aoyama Minato-ku, Tokyo 107-0062 JAPAN Tel: + 81 3 3408 3118 Fax: + 81 3 3408 3553 tokyo.ofc@computer.org

Individual paper REPRINTS may be ordered at: <reprints@computer.org>

Editorial production by Lisa O'Conner Cover art production by Alex Torres Printed in the United States of America by The Printing House

IEEE Computer Society Conference Publishing Services (CPS)

http://www.computer.org/cps

# **Message from the General Chairs**

Anurag Seth

Welcome to the joint 22nd International Conference on VLSI Design and 8th International Conference on Embedded Systems being held from 5th to 9th January, 2009 in New Delhi.

With a history of more than two decades, this conference has now become a prestigious annual event with participation from industry leaders, technical experts, practicing engineers, academicians and students from India and abroad. The conference theme this year is Improving Productivity Through Higher Abstraction, which reflects a growing concern about design productivity as the VLSI chips and systems are becoming increasingly complex while the time available for design is shrinking.

Like the past years, the conference brings three days of exciting technical sessions with papers selected through a world-wide peer review process and two days of informative tutorials by experts on topics of current interest. While the technical papers will present new results and discuss the intricacies of VLSI Design, Electronic Design Automation and Embedded Systems, there will be keynotes and invited talks by the leaders in the industry and academia, who would present a broader picture of the state of the art and do a bit of crystal gazing into the future. Keynote speakers in this conference include Justin Rattner, Intel Senior Fellow, Chief Technology Officer, Abhi Talwalkar, President and CEO, LSI Corp., Neil Henderson, GM, Mentor Graphics, Thomas Williams, Synopsys Fellow, Dr. Ajoy Bose, Founder, Atrenta and Jacob Abraham, Professor, University of Texas, Austin.

The conference has been constantly striving for improving its quality in order to attract the best of the people in the field. This year there has been a very good response to our call for papers. There were as many as 320 paper submissions, out of which the Program Chairs, Preeti Ranjan Panda and Rajendran Panda, along with their team of program committee members and reviewers, have selected the best 79 through a rigorous review process. This is a testimony to the growing stature of the conference and the selectivity it can afford now. The Tutorial Chairs, Sanjiv Narayan and Atul Jain, with their team of reviewers, have organized 7 full day and 2 half day tutorials on a variety of topics including Power-conscious Tests, Security & Dependability of Embedded Systems and Power Management for Mobile Multimedia. Again, the response for tutorial submissions has been overwhelming with a record 40+ submissions and the review team had a tough time selecting the 9.

The Industry Forum is now a regular feature of this conference. The Special Sessions Chair Rajiv Kapur has put together a session on Made for India, which would try to capture thoughts about the growing economy of India as an agent in shaping the electronic products. Among the special sessions, besides the mentioned keynotes, we have various high quality technical talks ranging from platform based design to computational lithography to Analog Design to Low Power issues and standards. Moreover, we have

four panel discussions this year in the areas of IP, EDA, Embedded software, and Automotive/Made for India.

We continue to encourage and facilitate participation of students. In the 2008 conference, a new feature Students Track was introduced with a view to initiate them in the field. The Student Track chairs Gurudutt Bansal and M. Jagadesh Kumar have organized a track for students that will run parallel to technical sessions on the 3rd day of the conference. The regular participants from the academia, both students and faculty, are supported through the fellowship program, which is being coordinated by the Fellowships Chair Vineet Sahula. The promotional activities of the conference, which aim at bringing out innovative ideas from the budding professionals, include a Design Contest and the new EDA Software Contest introduced this year. The Design Contest Chairs Aloknath De and Subind Kumar and the EDA Contest Chairs Manu Lauria and Shabbir Batterywala have organized these contests.

A conference of this magnitude cannot materialize without the financial support from the industry as well as organizational efforts from the individuals. The Sponsorship and Exhibits Chairs Sanjeev Aggarwal and S. Uma Mahesh have taken care of mobilizing the required financial resources. The sponsors this year include Cadence, ARM, Magma, Atrenta, Broadcom, and Conexant. You can expect to see state of the art exhibits from these companies as well as several others. The Organizing Chair Rajeev Sehgal and Organizing Coordinator Harish Chauhan have put in tremendous efforts to bring the conference to this shape. As expected, without the proactive drive from the Finance Chair Prem Nivasa (especially in the current economy) with a good tab on inflows and outflows and compliance issues etc, things would have been not as smooth.

We would also like to acknowledge the proactive efforts from our publicity chairs – Ricky Bedi, Sapan Garg and Yatin Trivedi to make the conference a grand affair.

The role of the Publication Chair Nagi Naganathan and Lisa O'Conner, Production Editor, Conference Publishing Services of IEEE has been very crucial in bringing out the conference proceedings in a timely manner.

The conference has been enjoying association with several reputed professional societies, that adds to its prestige. We acknowledge the contributions of CP Ravikumar (VLSI Society of India), N. Ranganathan (IEEE Circuits and Systems Society), Anantha Chandrakasan (IEEE Solid-State Circuits Society), Nikil Dutt (ACM/SIGDA) and Poornima Shenoy (Indian Semiconductor Association) in making this association continue.

Finally we would like to thank the Steering Committee Chair Vishwani Agrawal and other members of the Steering Committee for giving us this opportunity to organize the conference. Hope you will enjoy the conference as well as the host city of Delhi.

Anshul Kumar and Anurag Seth

# **Message from the Program Chairs**

Preeti Ranjan Panda

Rajendran Panda

It is our pleasure to welcome you all to 2009 edition of the VLSI Design Conference! A strong technical program has been the hallmark of VLSI Design Conferences in the past, and we have endeavored to ensure that you will witness an outstanding technical program this year also.

In keeping with the international character of the conference, this year we received about 320 paper submissions from 21 countries. While India and USA accounted for a large fraction of the submissions, we also received a significant response from Iran, China, Japan, Germany, and UK. Getting the papers reviewed in the two months we had set for ourselves was a challenging task and would not have been possible without the hard and diligent work put in by the 90 member Technical Program Committee consisting of leading researchers from across the world, from both academia and industry. The papers were divided into 9 tracks based on subject areas, and were reviewed by a total of more than 300 reviewers. We are very much indebted to the team of reviewers for doing an outstanding job in making a thorough and fair evaluation of the submissions, that resulted in an average of more than 4 reviews per paper. Email discussions were initiated by the track chairs even before the actual program committee meeting, and approximate decisions were identified. In keeping with the conference tradition, two program committee meetings were organised - one in IIT Delhi and the other in Rutgers University, USA. A total of 57 Regular papers and 22 Short papers were selected by the program committee for inclusion in the technical program. These excellent papers, on a wide-ranging set of topics related to VLSI Design and Embedded Systems, have been organized into three parallel tracks for presentation. The selection process was highly competitive and many good papers could not make it to the final list. We sincerely hope that the feedback from our expert reviewers was helpful to every author. This being also an embedded systems conference, we have one running track on 6th January titled "Embedded Systems Day".

We would like to thank all authors for considering VLSI Conference as a venue for publishing their work. We would like to place on record our gratefulness to the Technical Program Committee members and the volunteer reviewers who worked very hard to make the technical program happen. The program committee list and reviewer list appears elsewhere in these proceedings, but we would like to take the opportunity to convey our special thanks to the track chairs who managed the review procedure within the nine tracks: Srivaths Ravi (Test), Prabhat Mishra (Synthesis and Verification), Nitin Chandrachoodan and Sudeep Pasricha (Application Specific Architectures), Puneet Gupta and Susmita Sur-Kolay (Physical Design), Praveen Elakkumanan and Nagi Naganathan (Low Power Electronics), Shouri Chatterjee (Analog), Kolin Paul and Tulika Mitra (Embedded Systems), Rajiv Joshi (TCAD), and Vijay Degalahal (Architecture). We also like to convey our deep appreciation to Vishwani Agrawal, Srimat Chakradhar, N. Ranganathan, and Mike Bushnell for their valuable help, feedback, and support throughout the planning and execution of the review process.

Special thanks are due to Nagi Naganathan, the Publications Chair, for undertaking the crucial and difficult task of co-ordinating with everyone else for compiling the contents of the conference proceedings and overall management of the iterative process, and to Lisa O'Conner, Production Editor at the Conference Publishing Services of IEEE for her expert handling of the proceedings production and for patiently and instantly accommodating the numerous update requests in spite of ill health. The polished final product in your hands is the result of their untiring efforts.

We sincerely believe we have assembled for you an outstanding technical program, and we hope you enjoy the experience. The charming capital city of Delhi has ancient history rubbing shoulders with high technology; it will dazzle you with its breathtaking sights, and has much to offer to both the first time visitor as well as the experienced traveller. We invite you to lose yourself amidst the tantalizing environs in and around Delhi.

Preeti Ranjan Panda, *IIT Delhi* Rajendran Panda, *Freescale Semiconductor, Austin* **VLSI09 Program Chairs** New Delhi, January 2009

# **Message from the Organizing Chair**

Welcome to the 22nd VLSI Design and 8th Embedded Systems conference to be held from 5th to 9th January 2009.

In the past years India has seen a lot of growth in the VLSI and Embedded Systems industry. The leading educational institutes in India have also been actively introducing curriculum with focus on this industry. Not only that, there has been increasing collaboration between the two on focused research in solving some of the extremely complex problems faced by the industry. The VLSI and Embedded systems conference is more relevant than other time in the past.

In these extremely difficult economic times to stage a conference of this size was a challenge. Anurag Seth and Dr. Anshul Kumar, the General chairs have led from the front in achieving the high goals set for the conference and I would like to acknowledge their efforts for the same.

The conference comes to New Delhi and National Capital Region (NCR) after a gap of 6 years. Significant changes have occurred during this period. There has been the introduction of Metro, building of more flyovers and still a lot of construction is going all around in preparation for the 2010 Commonwealth games to be held here. Similarly there has been tremendous growth in VLSI Design and EDA companies in last six years, NCR is now home to major VLSI Design centers such as ST and Freescale. It is also a home for many EDA companies, such as Cadence, Mentor, Sequence, Magma, Calypto, Co-Ware, Atrenta, Interra Systems, and so on.

I am sure you will enjoy the conference, tutorials, panel discussions, keynote speeches, industry forum and the special "Made for India" track, that the organizing committee has put together this year. Capital of India, New Delhi houses finest museums, galleries, shopping, dining and entertainment inviting you to take a plunge into the history and modernity of the city.

Once again, I welcome you to Delhi and the conference and have a memorable 5 days.

Rajeev Sehgal Organizing Chair

# **Conference Steering Committee**

Vishwani D. Agrawal, Chair

Jaswinder Ahuja M. Balakrishnan Srimat T. Chakradhar Dasaradha Gude Apurva Kalia Bobby Mitra A. Prabhakar N. Ranganathan C.P. Ravikumar

# **VLSI Design 2009 Committee Members**

Steering Committee Chair

Vishwani Agrawal Auburn University

#### **General Chair**

Anshul Kumar IIT Delhi

#### **Program Chair**

Preeti Ranjan Panda IIT, Delhi

#### Organizing Coordinator

Harish Chauhan *Cadence*

#### **Program Chair**

Rajendran Panda Freescale

#### **Publication Chair**

Nagi Naganathan LSI Corp.

**General Chair**

Anurag Seth Cadence

#### **Organizing Chair**

Rajeev Sehgal Mentor Graphics

#### **Publicity Chair**

Ricky Bedi Magma

#### **Tutorial Chair**

Sanjiv Narayan *Calypto*

#### Sponsorship / Exhibit Chair

Sanjeev Aggarwal *Cadence*

#### **Design Contest Chair**

Aloknath De ST Microelectronics

#### **Publicity Chair**

Sapan Garg Atrenta

#### **Tutorial Chair**

Atul Jain *TI*

#### Sponsorship / Exhibit Chair

S. Uma Mahesh Indrion Technologies

#### **Design Contest Chair**

Subind Kumar Freescale

#### **Publicity Chair**

Yatin Trivedi Magma

#### **Special Session Chair**

Rajiv Kapur Broadcom

#### **Finance Chair**

Prem Nivasa Mentor Graphics

#### **Fellowship Chair**

Vineet Sahula MNIT, Jaipur

#### **EDA Contest Chair**

Manu Lauria *Cadence*

#### **Student Track Chair**

Gurudutt Bansal *Cadence*

#### **SSCS** Liaison

Anantha Chandrakasan *MIT*

#### ACM/SIGDA Liaison

Nikil Dutt University of California, Irvine

#### **EDA Contest Chair**

Shabbir Batterywala Synopsys

#### **Student Track Chair**

M Jagadesh Kumar IIT, Delhi

#### **ISA** Liaison

**Poornima Shenoy**

#### **IEEE** Liaison

Nagarajan Ranganathan University of South Florida

#### **VSI** Liaison

CP Ravi Kumar TI

# VLSI Design 2009 Technical Program Committee

#### **Program Co-Chairs**

Preeti Ranjan Panda, IIT Delhi, India Rajendran Panda, Freescale Semiconductor, USA

Tracks (Names of Track Chairs or Co-Chairs are in BOLD)

### AMS: Analog, RF, Mixed Signals

Shouri Chatterjee, IIT Delhi, India Debapriya Sahu, Texas Instruments, India G.S. Visweswaran, IIT Delhi, India Nagendra Krishnapura, IIT Madras, India Pavan K. Hanumolu, Oregon State University, USA Prakash Easwaran, Cosmic Circuits, India Sambuddha Bhattacharya, Synopsys, India Shanthi Pavan, IIT Madras, India Srinivasan C, Cosmic Circuits, India Vivek G. Pawar, Sankalp Semiconductor, India

#### ASA: Application Specific Architecutures, Security Nitin Chandrachoodan, IIT Madras, India Sudeep Pasricha, Colorado State University, USA Ashish Mathur, Freescale Semiconductor, India Mona Mathur, ST Microelectronics, India Sivakumar Sri, Wipro, India Sri Parameswaran, UNSW, Australia Sri Chandra, Freescale Semiconductor, India Sriram R. Vangal, Intel, USA,

#### PHY: Physical Design, DFM, Power and Signal Integrity, Interconnect and Timing Analysis/Optimization, Reliability Puneet Gupta, UCLA, USA Susmita Sur-Kolay, ISI Kolkata, USA Chul-Hong Park, Samsung, S. Korea Elaheh Bozorgzadeh, University of California, Irvine, USA

Florin Balasa, Southern Utah University of California, Irome, US Florin Balasa, Southern Utah University, USA Min Zhao, Magma Design Automation, USA Murat Becer, CLK-DA, USA Puneet Sharma, Freescale Semiconductor, USA Sao-Jie Chen, National Taiwan University, Taiwan Savithri Sundareswaran, Freescale Semiconductor, USA Shabbir Batterywala, Synopsys, India Vishal Khandelwal, Synopsys, USA Vladimir Zolotov, IBM, USA EMB: Embedded Systems, Fault Tolerance, Sensor Networks, Ubiquitous Computing, Asynch. Design, Low Power Systems Kolin Paul, IIT Delhi, India Tulika Mitra, National University of Singapore, Singapore Anup Gangwar, AMD, India Basant Dwivedi, Calypto Design Systems, India Javier Resano, UCM Madrid, Spain David Atienza, UCM Madrid, Spain Madhu Mutyam, IIT Madras, India Mahesh Mehendale, Texas Instruments, India Nikil Dutt, UC Irvine, USA Niraj Jha, Princeton University, USA Paolo Ienne, EPFL, Switzerland Pradip Jha, Xilinx, USA Samarjit Chakrabarty, National University of Singapore, Singapore Sarma Vrudhula, Arizona State University, USA

LPE: Low Power Electronics Nagi Naganathan, LSI Corp, USA Praveen Elakkumanan, IBM, USA Amit Patra, IIT Kharagpur, India

Bharadwaj Amrutur, IISc, India Ram Krishnamurty, Intel, USA Tezaswi Raja, LSI Corp, USA Xin Li, CMU, USA Aditya Bansal, IBM, USA Saibal Mukhopadhyay, Georgia Tech., USA

#### TECH: Technology, Device Modeling and Simulation, MEMs, Nanoelectronics, and Biological Systems

Rajiv Joshi, IBM, USA Bipul Paul, Toshiba, USA Durgamadhab Misra, NJIT, USA Josef Watts, IBM, USA M. Jagadesh Kumar, IIT Delhi, India Madabusi Govindarajan, IBM, India Sukumar Jairam, Texas Instruments, India

#### ARCH: Processor Architecture, Multi-core Systems

Vijay Degalahal, Intel, India Ashok Jagannathan, Intel, India Maurizio Palesi, UNICT, Italy Petru Eles, Linkoping Universitet, Sweden Nagarajan Ranganathan, University of South Florida, USA S.K. Nandy, IISc, India Sourav Roy, Freescale Semiconductor, India

# SYN: Design Specification, Modeling, and Synthesis, Hardware/Software Co-design, Simulation, Emulation and Formal Verification

#### Prabhat Mishra, University of Florida, USA

Indira Iyer, Synfora, India Jayanta Bhadra, Freescale Semiconductor, USA Logie Ramachandran, Synopsys, USA Malay Haldar, Calypto Design Systems, India Pallab Dasgupta, IIT Kharagpur, India Saraju Mohanty, University of North Texas, USA Shankar Hemmady, Synopsys, USA Sandeep Shukla, Virginia Tech, USA

#### **TEST: Testing, DFT**

#### Srivaths Ravi, Texas Instruments, India

Adit Singh, Auburn University, USA Bernard Courtois, CMP, France Bhargav Bhattacharya, ISI Kolkata, India Kartik Mohanram, Rice University, USA Kewal Saluja, University of Wisconsin, USA Nagesh Tamarapalli, AMD, India Pradip Thaker, Analog Devices, India C. P. Ravikumar, Texas Instruments, India Rubin Parekhji, Texas Instruments, India Srimat Chakradhar, NEC Labs, USA Sudhakar Reddy, University of Iowa, USA Vishwani Agrawal, Auburn University, USA

# Reviewers

# **External Reviewers**

Aashish Pant Abhijit Das Adam Donlin Ajit Pal Ajit Gupte Alexander Fell Alok Pugalia Aman Kokrady Amin Khajeh Amit Badole Amit D Amol Bhinge Amrit Singh Anshoo Tandon Anshuman Chandra Ansuman Banerjee Anthony Chun Anupam Singal Apu Sivadas Aravindh Anantaraman Ari Valero-Lopez Arup Chakraborty Aseem Gupta Ashok Balivada Bernd Becker Bhaskar Pal Bhasker Karmakar **Bijov** Jose Bo Hu Bo Wan Chandra Tirumurti Chandramouli Gopalakrishnan Chao Huang Charles Wen Chittaranjan Mandal Chouki Aktouf Chrysostomos Nicopoulos Chungchun Wan Chunhua Yao Colin Tan Craig Gleason Daniel Chaver Daniel Mozos

UCLA TIXilinx *Indian Institute of Technology-Kharagpur* ΤI Indian Institute of Science Sankalp Semiconductor P. Ltd. TIUniversity of California, Irvine Freescale Semiconductor ΤI Freescale Semiconductor Freescale Semiconductor Freescale Semiconductor Synopsys Interra Systems Intel Freescale Semiconductor TIIntel LSI University of California, Irvine University of California, Irvine Analog University of Freiburg, Germany Synopsys ΤI Virginia Tech Intel Synopsys Virginia Tech National Chiao Tung University, Taiwan

Indian Institute of Technology-Kharagpur DeFacTo Technologies EPFL Stanford University University of Wisconsin National University of Singapore Synfora Universidad Complutense de Madrid Universidad Complutense de Madrid Debasri Saha Deepak C. Deepak Mathaikutty Deji Akinwanda Devadutt K Devanathan Varadarajan Dhruva Ghai Dong Ha Dwarka Prasad Ekaterina Trofimova Elias Kougianos Erika Cota Fan Wang Gabor Madl Gaurav Singh Gireesh Rajendran Grady Giles Haihua Yan Hangsheng Wang Hans-Joachim Wunderlich Harish P Hillary Grimes Himanshu Thapliyal Himyanshu Anand Hiren Patel Huynh Phung Huynh Ilia Polian Indradeep Ghosh Irith Pomeranz Iwao Yamazaki Jais Abraham James Tschanz Janakiraman V Jawar Singh Jiang Hu Jie Qin Jim Holt Jim Plusquellic Jimson Mathew Jins Davis Alexander Jong Eun Lee Jooheung Lee José Ayala Jose Ignacio Gomez Jose Luis Risco Juan Antonio Clemente Kalyana Chakravarty Kanishka Lahiri Kausar Banoo Kausik Datta

Indian Statistical Institute Indian Institute of Science Intel Stanford University Synfora ΤI University of North Texas Virginia Tech Freescale Semiconductor Freescale Semiconductor University of North Texas Universidade Federal do Rio Grande do Sul **Juniper** Network University of California, Irvine Virginia Tech ΤI AMD Synopsys Freescale Semiconductor University of Stuttgart, Germany Indian Institute of Science Auburn University University of South Florida Freescale Semiconductor University of California, Berkeley National University of Singapore Fujitsu Purdue University Hitachi AMD Intel **Bristol University** Texas A&M University Auburn University Freescale Semiconductor

Freescale Semiconductor University of New Mexico Bristol University Auburn University Arizona State University University of Central Florida Universidad Complutense de Madrid Universidad Complutense de Madrid Universidad Complutense de Madrid Universidad Complutense de Madrid Ereescale Semiconductor Intel LSI Interra Systems Kedarnath Balakrishnan Keshavan Varadarajan Koushik M Koustav Bhattacharya Krishnaiah Gummidipudi Krishnaswamy T L. Begin Lerong Chen Lin Li Lin Zhong Loganathan Lingappan Lokesh Gupta Luis Bathen M. Balakrishnan Mahalingam Venkataraman Mainak Banga Manish Pillai Manish Ratnani Manish Pillai Manvi Agarwal Marcos Sanchez-Elez Michael Bushnell Michael Hsiao Michel Renovell Mihir Choudhury Mike Burns Mingsong Chen Minyoung Kim Mohammed Ashfaq Shukoor Mrinal Bose Mukesh Mishra Mukund Sivaraman Narasimhaswamy Bharath Naveen Raina Neeraj Goel Nisar Ahmed Nishad P Nithiyanandan Bashyam Nitin Yogi Nur Touba Pablo García Palkesh J Patrick Schaumont Paul Schumacher PJ Joseph Prajit Nandi Prakash Venkitaraman Prasanta Basu Pratap Das Praveen Sanjeev

#### AMD

Indian Institute of Science Indian Institute of Science University of South Florida Indian Institute of Technology-Delhi TIUniversité Libre de Bruxelles University of California, Los Angeles Intel *Rice University* Intel Magma University of California, Irvine Indian Institute of Technology-Delhi University of South Florida Virginia Tech TIUniversity of North Texas TINXP Universidad Complutense de Madrid Rutgers University Virginia Tech LIRMM, France *Rice University* Freescale Semiconductor University of Florida University of California, Irvine Auburn University Freescale Semiconductor Intel Synfora AMD Freescale Semiconductor Indian Institute of Technology-Delhi ΤI University of Minnesota Intel Auburn University University of Texas-Austin Universidad Complutense de Madrid TIVirginia Tech Xilinx Freescale Semiconductor Sankalp Semiconductor P. Ltd. AMD Calcutta University Indian Institute of Science Analog

Preetam T R Datta Rahul Jain Rajamani Sethuram Rajaraman Ramanarayanan Rajat Bhatia Rajesh S Rakesh Kumar Rakesh Gnana David Ramkumar Jayaseelan Rani Ghaida Ranjan Bose Ravi Venkatesan Rohit Kapur Rubin Parekhji Saibal Mukhopadhyay Sanatan Chattopadhyay Sandeep Oswal Sandip Kundu Sandip Ray Sanjay Kumar Sanjukta Bhanja Sankaran Aniruddhan Santosh Salunkhe Sanu Mathew Saravana Ganeshan Satish Anand Satish Yada Satishkumar Udayanarayanan Saurabh Tiwari Seiji Kajihara Shail Aditya Shailendra Jain Shakti R Sharad Seth Shashi Kumar Shiva Kasiviswanathan Shreya Dasgupta Shyam Sundar Silpa BVN Sitaraman Iver Sivaramalinga, Reddy Soonte Kim Soujanna Sarkar Soumyaroop Roy Sravan Kumar Srinivas Patil Srinivas V Srinivas Katkoori Srinivasulu Alampally

TITICalypto Design Systems Intel Freescale Semiconductor Cosmic Circuits ΤI National University of Singapore University of California, Los Angeles Indian Institute of Technology-Delhi Intel Synopsys ΤI Georgia Tech TIUniversity of Massachusetts University of Texas-Austin Broadcom University of South Florida Analog Intel TIIntel Wipro Intel Synfora Intel TIUniversity of Nebraska-Lincoln Jonkoping University, Sweden Penn State Analog Analog Indian Institute of Technology-Delhi Analog Information and Communication University, S. Korea TIUniversity of South Florida AMD Intel TIUniversity of South Florida ΤI

Sriparna Saha Subhasis Banerjee Subir Roy Subodh Sharma Subramanian Rajagopalan Subrat Panda Sudheer Prasad Sudip Shekhar Sujoy Chakravarty Suman Mandal Sumant Kale Sumit Ahuja Surendra Guntur Suresh PR Sutirtha Sanyal Swarup Bhunia T Pramod Tania Mishra Tej Rai Theocharis Theocharides Tomokazu Yoneda Tuck-Boon Chan Udaykumar H Umit Ogras Upavan Gupta V. Nagarajan Vaideeswaran Sethuraman Veezhinathan Kamakoti Venkatesh C Venugopal Puvvada Vijay Sundaresan Vikram K.N. Vincenzo Catania Virendra Singh Wei Jiang Wei Qin Weixun Wang Wen Xiaoqing Xiaofang Wang Xiaoke Qin Xijiang Lin Yang Yi Yi-Shing Chang Yong Wang Yoshinobu Higami Yu Huang Yuhong Fu Zhan Guo Zhao Li

Indian Statistical Institute Intel TI University of Utah, Salt Lake City Indian Institute of Technology-Kharagpur TI

ΤI

Virginia Tech NXP TI Barcelona Supercomputing Center Case Western Magma University of Florida Freescale Semiconductor University of Cyprus NAIST, Japan University of California, Los Angeles TI Intel University of South Florida

#### AMD

*Indian Institute of Technology-Chennai Indian Institute of Science*

University of Cincinatti George Washington University University of Catania, Italy Indian Institute of Science Auburn University Boston University University of Florida Kyushu Institute of Technology, Japan Villanova University University of Florida Mentor Graphics Freescale Semiconductor Intel

Ehime University, Japan Mentor Graphics Freescale Semiconductor Lund University, Sweeden

# **Tutorial Committee**

#### **Tutorial Co-Chairs**

Atul JainTexas InstrumentsSanjiv NarayanCalypto Design Systems

#### Reviewers

Abhishek Ranjan Alok Jain Anand K. Anil Kumar Anindya Saha Anup Gangwar Anurag Midha Apu Sivadas Arun Chandrashekhar Arun Ramakrishnan Ashish Mathur Basant Dwivedi Bhaskar Karmakar D. R. Bhaskar Dwayne Lee Frank Vahid Ganesan Thiagarajan Jagdish Rao Jai Balakrishnan Jairam Sukumar Jayashree Saxena Kaushik De Ken Butler Kolin Paul M. Balakrishnan Mahesh Mehendale Manu Chopra Nikil Dutt Nitin Chandrachoodan

Nitin Chawla Pallab Dasgupta Pradeep Kumar Pravin Jain Raj Mitra Raj Senani Rajan Arora **Rajeev Sehgal** Rajendra Pratap Rajesh Gupta Ranga Vemuri Ranjit Dash Reene Tayal Ricky Bedi Rubin Parekji S. Dharamrajan Sandeep Bhatia Sandeep Kumar Sandeep Pagey Sanjeev Saluja Saraju Mohanty Shabbir Batterywala Subhahshish Mukherjee Sushil Gupta Udaykumar H. Venugopal Puvvada Vinod Kathail Vivek Pawar

# VLSI Design 2008 Fellowship Recipients

Ajith Kumar Panda Anilkumar V. Nandi Arunachalam.V Babita Roslind Jose Bhanu Murthy Bhaskara Bhavesh **B.Karthikeyan** Bishnu Prasad Das C.D.Naidu C.N. Shariff Surajit Das Dipak Kumar Kole Darvinder singh Oberoi Ahsan Raja Chowdhury Ghanshyam Singh H.Mangalam B.P. Harish Devasarmahiren Kumar Indranil Hatai Jayarajan. R K. Sivani Chitrasena Bhat Krishnendu Choudhury K. Sivasankaran Lakshmi Prabha Viswanathan T. Laxmikandan Prof. Kamaraju Ms.Madhusmita Panda Manu. T.M D. Meghanathan Nachiketa Das N.B. Balamurugan M. Nirmala Devi N. Rajkumar N. Siva Sankar Reddy Prof. N.S. Murthy Sreehari Rao Patri Pradyut Sarkar Priyabrata Pattananaik S.Rajaram Rajib Kar K. Venkata Ramanaiah Ramesh Bhakthavatchalu

NIS & T, Berhampur B.V.B. College of Engg. & Tech. SES, VIT University Cochin University Nalla Malla Reddy Coll. Of Engg. NIT, Silchar SES, VIT University IISC VNR Institute of Engg.& Tech. Bellary Engg.College Vidya Sagar College, Kolkata St. Thomas College of Engg.& Tech. University of Jammu University of Dhaka **MNIT** S.K. Collge of Engg. & Tech, Coimbatore Visveswaraya College of Engg. SMIT, Sikkim IIT, Kharagpur Anna University, Chennai Kakatiya Institute of Technology KIT, Tiptur NIT, Durga pur SES, VIT University Govt. College of Technology Anna University, Chennai GEC, Gudlavalleru CV Raman College of Engg. Bellary Engg.College Anna University, Chennai MERI Thiagarajar College of Engg. Amrita Vishwa VidyaPeetham NHCE Vasavi College of Engg. NIT, Warangal NIT, Warangal MCKV Institute of Engg. Silcon Institute of Technology Thiagarajar College of Engg. NIT, Durga pur Narayana Engg.College, Nellore Amrita Vishwa VidyaPeetham

Aytha Ramesh Kumar C.V. Krishna Reddy **Rockey Gupta** Pranab Roy **R.Sakthivel** M.Sreenivasulu Saroja V Siddamal Saurabh Choudhury S.Sivanantham Samrat L. Sabat S.Muthukumar Sriyankar Acharyya S. Moorthi M.Srinivasa Rao Susheel Kumar Sharma S.Vasu Krishna P. Vijay Kumar Vinayak V Vinoth Thyagarajan Madhavi latha Rajeshwari M Bankar S.P. Venu MadhavaRao Mohammed Abid Hussain Amit Harode Aseem Gupta Rahul M Badghare Chandan Karfa Rathna Falguni Sinhababu Prashanth Inanendra Arun Janarthanan Jimson Mathew Ianakiraman V K. Navaram Kumar Kameswara Rao Chepette Kaushik Bhattacharya G. Krishnaiah Rasmita Panda Mehdi Fazeli Susmit Maiti Mamatha.S, Mrs. G. Muneeswari Nagaraju Pothineni Neeraj Goel Noor Mahammad Sk Pejman Lotfi Kamran K. Praveen Kumar Reddy K. Shyamala S. Ramasamy R.V. Kshirsagar

VNR Institute of Engg.& Tech. Kakatiya Institute of Technology University of Jammu J & K BES University, Shibpur V IT University Nalla Malla Reddy Coll. of Engg. *INTU, Kukatpally* NIT, Silchar VIT University Central University VIT University West Bengal University of Tech. NIT, Tiruchirapalli VNR Institute of Engg.& Tech. University of Jammu J & K VNR Institute of Engg.& Tech. PSG College of Tech., Coimbatore VNIT, Nagpur Thiagarajar College of Engg. **JNTU** BVB College, Engg.& Tech. Osmania University IIIT, Hyderabad VNIT, Nagpur California VNIT, Nagpur IIT, Kharagpur Anna University, Chennai ViT University IIT, Madras University of Cincinnati University of Bristol IISc, Bangalore VNIT, Nagpur IIT, Delhi IIT, Kharagpur IIT, Delhi Berhampur University Sharif University of Tech., Azadi BES University, Shibpur IIIT, Hyderabad IIT, Madras IIT, Delhi IIT, Delhi IIT, Madras CAD Research Group VNIT, Nagpur IIT, Madras NIT, Trichy VNIT, Nagpur

Ravindra Jayanthi Ravindra Mukhiya Rupam Mukherjee Vikas. G S.D. Thimmappa Chandrashekhar T Kukade B.V.N. Silpa Narasimham K Soumyajit Dey Vijay Sundaresan Supata Ditti Uma Rajaram P.V. Sankara Rao Falguni Sinhababu Rabindra Kumar Pradhan Rangababu Abhay S Kochhar Abhishek Mittal Alladi. Mahish Amitava Banerjee Amey M. Walke Anurag Sharma Archana Devi .B.R. Aishwarya Bharathi Sankara V. Ashis Kumar Ashis Maity Lingamneni Avinash Biswajit Ray Chester Rebeiro Deepa Kannan Nithin B.Dev Vikas Singh Ganpat anant parulekar Hassan Raza Hitesh Kumar Gupta Jayalakshmi Periyasamy Prakash.J Jyotirmoy Ghosh T.V. Kalyan Kamalika Datta Ms Karthik T J M Kiran Kumar Reddy Kranthi Kumar.Guduru J.S. Krishnam Raja Reddy J. Lavanya Manas Kumar Lenka Shashidhar L Manikumar Ravula Shyam Shroff M. Vijaya Raju

IIIT, Hyderabad IIT, Kharagpur IIT, Kharagpur IISc, Bangalore IIT, Delhi VNIT, Nagpur IIT, Delhi C.C.C.M/B.A.R.CIIT, Kharagpur University of Cincinnati BES University, Shibpur Anna University, College of engg., IIT, Kharagpur BES University, Shibpur IIT, Kharagpur University of Hyderabad VNIT, Nagpur ViT University VNIT, Nagpur IIT, Kharagpur VNIT, Nagpur ViT University ViT University University of California, Irvine N.I.T.K. Surathkal IIT, Kharagpur IIIT, Hyderabad IISc, Bangalore IIT, Madras Arizona State University N.I.T.K. Surathkal IIT, Madras VNIT, Nagpur VNIT, Nagpur IISc Bangalore VNIT, Nagpur ViT University IIT, Kharagpur IIIT, Hyderabad IIT, Kharagpur IIT, Madras IISc, Bangalore N.I.T.K. Surathkal ViT University IIT, Madras IISc Bangalore IISc, Bangalore N.I.T.K. Surathkal IIT, Madras University of Hyderabad

Partha Mukhopadhyay Narendra Konidala Sreeram N S N S Vinay Arun.K **Omprakash** Parida Lalit Patnaik Prabhu Natarajan Pradeep Nair T. Prashanth Reddy Raja Shekar Guntupally Rajesh Kumar Dasari Prasenjit Ray Rooha Razmid Ahamed **Reiley Jeyapaul** Rajashekar n B. Sandeep Bhukya Hariprasad R. Rajasekhar Mohammed Shoaib Sivakumar Bondada Sreekanth Reddy P Sreehari Veeramachaneni K. Srimannarayana Karthik Santanu Sarkar Subho Chatterjee Subir Kumar mandal Sudip Roy Sumit Samajpati Sunil shah Virendra Thakur Mangaiarkkarasi.K Umakant Goyal Vani S P. Venkateswarlu Virendra Kumar Patidar Anurag Avinash Zope G.Palakshi S.V. Mohanasundaram Suraj Sindia Deepa Devendran V. Raghavendra Saurav Bandyopadhyay Amal Kumar Kundu Ajaykumar Devarapalli M. Kirthi Krishna Mohit Sharma Rahul Choudary Aranab Ray Vysakh

IIT, Kharagpur N.I.T.K. Surathkal IISc, Bangalore IISc, Bangalore Anna Univ, College of Engg., **IISc Bangalore** IISc Bangalore Anna University IISc, Bangalore VNIT, Nagpur N.I.T.K. Surathkal IIT, Madras BES University, Shibpur VNIT, Nagpur Arizona State University IISc, Bangalore VNIT, Nagpur VNIT, Nagpur Anna University, College of Engg., IIT, Madras IISc, Bangalore IIIT, Hyderabad IIIT, Hyderabad Sathyabama University IIT, Kharagpur IIT, Kharagpur VNIT, Nagpur IIT, Kharagpur IIT, Madras IIT, Delhi IIT, Madras ViT University IISc Bangalore ViT University NIT, Trichy IIT, Madras VNIT, Nagpur IIT, Madras NIT, Trichy IISC, CEDT IIT, Madras IIIT, Pune IIT, Kharagpur IIT, Kharagpur University of Hyderabad IIIT, Hyderabad Malaviya Institute of Technology, Jaipur Malaviya Institute of Technology Malaviya Institute of Technology Amrita University, Kerala

Navneet Menon Ashwin Menon Ranjith C Ms Gayatri Venugopal. M Swagat Nanda Anusha Kakarala Amrita University Amrita University National Institute of Technology, Warangal National Institute of Technology National Institute of Technology VIT VIT

# VLSI Design 2008 Best Paper Awards

#### Arun Kumar Choudhury Best Paper Award

"Integrated TIA-Equalizer for High Speed Optical Link"

Saurav Bandyopadhyay (Indian Institute of Technology, Kharagpur) Stephen E. Ralph (Georgia Institute of Technology, USA) Pradip Mandal (Indian Institute of Technology, Kharagpur) Kenneth Pedrotti (University of California, Santa Cruz, USA)

#### Nripendra Nath Biswas Best Student Paper Award

"Recursive Statistical Blockade: An Enhanced Technique for Rare Event Simulation with Application to SRAM Circuit"

Amith Singhee (*Dept. of ECE, Carnegie Mellon University, Pittsburgh, USA*) Jiajing Wang (*ECE Dept., University of Virginia, Charlottesville, USA*) Benton H. Calhoun (*ECE Dept., University of Virginia, Charlottesville, USA*) Rob A. Rutenbar (*Dept. of ECE, Carnegie Mellon University, Pittsburgh, USA*)

#### Honorable Mention Award

"Compact Modeling of Suspended Gate FET"

Y.S. Chauhan (*Ecole Polytechnique Fédérale de Lausanne (EPFL), Switzerland*)

D. Tsamados (Ecole Polytechnique Fédérale de Lausanne (EPFL), Switzerland)

N. Abelé (Ecole Polytechnique Fédérale de Lausanne (EPFL), Lausanne, Switzerland) and (ST Microelectronics, Crolles, France)

C. Eggimann (Center for Integrated Systems, Stanford University, Stanford, CA USA)

M. Declercq (Ecole Polytechnique Fédérale de Lausanne (EPFL), Lausanne, Switzerland)

A.M. Ionescu (Ecole Polytechnique Fédérale de Lausanne (EPFL), Lausanne, Switzerland)

#### Honorable Mention Award

"Optimal Dual-VT Design in Sub-100 Nanometer PDSOI and Double-Gate Technologies"

Aditya Bansal (School of Electrical and Computer Engineering, Purdue University, West Lafayette, USA) Jae-Joon Kim (IBM T. J. Watson Research Center, Yorktown Heights, USA) Keunwoo Kim (IBM T. J. Watson Research Center, Yorktown Heights, USA) Saibal Mukhopadhyay (IBM T. J. Watson Research Center, Yorktown Heights, USA) Ching-Te Chuang, (IBM T. J. Watson Research Center, Yorktown Heights, USA) Kaushik Roy (School of Electrical and Computer Engineering, Purdue University, West Lafayette, USA)

## VLSI Design Conference History

| Meeting<br>Sequence | Place               | Dates               | Number of<br>Papers | Number of<br>Posters | Number of<br>Tutorials | Proceedings<br>Pages |

|---------------------|---------------------|---------------------|---------------------|----------------------|------------------------|----------------------|

| First               | Madras,<br>India    | Dec. 26-28,<br>1985 | 29                  | 0                    | 1                      | 193                  |

| Second              | Bangalore,<br>India | Dec. 15-18,<br>1988 | 26                  | 21                   | 4                      | 496                  |

| Third               | Bangalore,<br>India | Jan. 6-9,<br>1990   | 30                  | 22                   | 4                      | 390                  |

| Fourth              | New Delhi,<br>India | Jan. 4-8,<br>1991   | 45                  | 16                   | 9                      | 315                  |

| Fifth               | Bangalore,<br>India | Jan. 4-7,<br>1992   | 57                  | 24                   | 4                      | 378                  |

| Sixth               | Bombay,<br>India    | Jan. 3-6,<br>1993   | 70                  | 9                    | 6                      | 371                  |

| Seventh             | Calcutta,<br>India  | Jan. 5-8,<br>1994   | 87                  | 0                    | 6                      | 448                  |

| Eighth              | New Delhi,<br>India | Jan. 4-7,<br>1995   | 77                  | 6                    | 6                      | 456                  |

| Ninth               | Bangalore,<br>India | Jan. 3-6,<br>1996   | 75                  | 16                   | 6                      | 480                  |

| Tenth               | Hyderabad,<br>India | Jan. 4-7,<br>1997   | 84                  | 18                   | 6                      | 608                  |

| Eleventh            | Chennai,<br>India   | Jan. 4-7,<br>1998   | 98                  | 0                    | 6                      | 624                  |

| Twelfth             | Goa,<br>India       | Jan. 7-10,<br>1999  | 103                 | 0                    | 6                      | 682                  |

| Thirteenth          | Calcutta,<br>India  | Jan. 3-7,<br>2000   | 93                  | 0                    | 6                      | 590                  |

| Fourteenth          | Bangalore,<br>India | Jan. 3-7,<br>2001   | 77                  | 0                    | 9                      | 592                  |

| Fifteenth           | Bangalore,<br>India | Jan. 7-11,<br>2002  | 109                 | 0                    | 8                      | 834                  |

| Sixteenth           | New Delhi,<br>India | Jan. 4-8,<br>2003   | 84                  | 0                    | 6                      | 622                  |

| Seventeenth         | Mumbai,<br>India    | Jan. 5-9,<br>2004   | 120                 | 44                   | 8                      | 1132                 |

| Eighteenth          | Kolkata,<br>India   | Jan. 3-7,<br>2005   | 113                 | 23                   | 9                      | 922                  |

| Nineteenth          | Hyderabad,<br>India | Jan. 3-7,<br>2006   | 136                 | 0                    | 11                     | 880                  |

| Twentieth           | Bangalore,<br>India | Jan. 6-10,<br>2007  | 147                 | 0                    | 15                     | 990                  |

| Twenty First        | Hyderabad,<br>India | Jan. 4-8,<br>2008   | 108                 | 0                    | 10                     | 780                  |

| Twenty<br>Second    | New Delhi,<br>India | Jan. 5-9,<br>2009   | 79                  | 0                    | 9                      | 632                  |

## Embedded Systems Conference: History

| Meeting<br>Sequence | Place               | Dates              | Number of<br>Papers | Proceedings<br>Pages |

|---------------------|---------------------|--------------------|---------------------|----------------------|

| First               | New Delhi,<br>India | Jan. 2-4,<br>2002  | 8                   | 70                   |

| Second              | New Delhi,<br>India | Jan. 4-8,<br>2003  | 84                  | 622                  |

| Third               | Mumbai,<br>India    | Jan. 5-9,<br>2004  | 120                 | 1132                 |

| Fourth              | Kolkata,<br>India   | Jan. 3-7,<br>2005  | 113                 | 922                  |

| Fifth               | Hyderabad,<br>India | Jan. 3-7,<br>2006  | 136                 | 880                  |

| Sixth               | Bangalore,<br>India | Jan. 6-10,<br>2007 | 147                 | 990                  |

| Seventh             | Hyderabad,<br>India | Jan. 4-8,<br>2008  | 108                 | 780                  |

| Eighth              | New Delhi,<br>India | Jan. 5-9,<br>2009  | 79                  | 632                  |

#### About the Cover

India Gate, an important monument of the city, is a memorial built in commemoration of more than 80,000 Indian soldiers who were killed during World War I. At the base of the India gate there is another memorial, the Amar Jawan Jyoti (Flame of the immortal warrior), a never-ceasing flame under the humongous arch to remind the nation of soldiers who laid their lives to serve this nation. India Gate was designed to convey to the people of India the values of "Duty, discipline, unity, fraternity, loyalty, service and sacrifice".

Delhi is the capital of India, a country that blends an amazing history and a dynamic future creating an enchanting experience for all of its visitors, a vibrant dynamic masterpiece, the largest democracy and second most populous nation on earth. It offers a unique cultural mix blending ancient and noble cultures, modern and dynamic societies.

New Delhi is the only city in the world with 3 World Heritage Sites – The Red Fort, The Qutub Minar and The Humayun's Tomb.

Delhi has had the honour to host many magnificent events in the past. In 1951, the inaugural edition of the Asian Games was organized in Delhi and again in 1982. Now the Capital city of Delhi is preparing to host the most prestigious Commonwealth Games in 2010.

# VLSI Design 2009

## **Invited Keynote Speakers**

Justin R. Rattner Intel Senior Fellow Vice President Director, Corporate Technology Group and Intel Chief Technology Officer

Neil Henderson General Manager, Embedded Systems Division (ESD) of Mentor Graphics

Dr. Ajoy K. Bose Chairman of the Board, Founder, President and Chief Executive Officer Atrenta Inc.

Abhi Talwalkar President and Chief Executive Officer LSI Corporation

Thomas W. Williams Synopsys Fellow, Synopsys, Inc.

Prof. Jacob A. Abraham Electrical and Computer Engineering University of Texas, Austin

## Invited Talks/Special Sessions Abstracts

## A Decade of Platform-Based Design: A look backwards, a look forwards

Grant Martin, Chief Scientist, Tensilica

Abstract:

It has been 10 years since a group of us wrote the book "*Surviving the SoC Revolution: A Guide to Platform-Based Design*", and almost a decade since I gave a talk at VLSI 2000 in Kolkata about this theme. The intervening time has seen considerable development in the platform based design approach. It has become the near ubiquitous approach to the development of complex SoCs for many application areas. It has branched out from its original, mainly hardware-centric focus, to assume much more of a system and software focus complementing hardware. And the nature of platform architectures have changed: we now see many more embedded processors of all kinds in SoC platforms, from application-specific processors (ASIPs) to clusters of homogeneous or heterogeneous processing engines and many integrated subsystems each including one or more ASIPs or general purpose cores.

This talk will look back at the past decade in platform based design and describe the evolution of architectures, design approaches and tools, and also look forward at the next decade or two and try to paint some possible scenarios for the future evolution of the platform-based approach. As we move towards new generations of design tools and higher level design approaches, what will be the main forms of platforms in future and how will designers use them?

#### Speaker Bio:

Grant Martin is a Chief Scientist at Tensilica, Inc. in Santa Clara, California. Before that, Grant worked for Burroughs in Scotland for 6 years; Nortel/BNR in Canada for 10 years; and Cadence Design Systems for 9 years, eventually becoming a Cadence Fellow in their Labs. He received his Bachelor's and Master's degrees in Mathematics (Combinatorics and Optimisation) from the University of Waterloo, Canada, in 1977 and 1978.

Grant is a co-author or co-editor of nine books dealing with SoC design, SystemC, UML, modelling, EDA for integrated circuits and system-level design, including the first book on SoC design published in Russian. His most recent book, *ESL Design and Verification*, written with Brian Bailey and Andrew Piziali, was published by Elsevier Morgan Kaufmann in February, 2007.

He was co-chair of the DAC Technical Program Committee for Methods for 2005 and 2006. His particular areas of interest include system-level design, IP-based design of system-on-chip, platform-based design, and embedded software. Grant is a Senior Member of the IEEE.

## Analog IC Design in Nanometer CMOS Technologies

Prof. Willy Sansen, K.U.Leuven Belgium

#### Abstract:

In nanometer CMOS technologies, several new effects emerge, such as velocity saturation and gate leakage currents. As a result the transconductance and speed are both limited by velocity saturation. Also noise and mismatch are affected as a result of the thinner gate oxides used. Moreover the supply voltage is reduced to values below 1 Volt, creating new challenges for analog circuit design.

This presentation provides a review of the modifications in model parameters, including noise and distortion. It is followed by an exploration of the noise/power compromise in existing circuit blocks such as Miller operational amplifiers and Gm-C filters. An overview is the given of low-voltage amplifiers/filters configurations with both Gate and Bulk drives. Several sub-1 Volt circuits are finally discussed for different applications.

#### Speaker Bio:

Prof. Willy Sansen has the PhD degree from the University of California, Berkeley in 1972. Since 1980 he has been full professor at the Catholic University of Leuven, in Belgium, where he has headed the ESAT-MICAS laboratory on analog design since 1984. He has been supervisor of sixtyfive PhD theses and has authored and coauthored more than 625 publications and sixteen books, among which is *Analog Design Essentials*. He is a Fellow of the IEEE. He was program chair of the ISSCC-2002 conference and is now President of the IEEE SSCS.

### Common Power Format: A User-driven Ecosystem for Proven Low Power Design Flows

Dr. Sumit DasGupta, Senior Vice President, Si2

#### Abstract:

Low power design has emerged as one of the urgent needs in IC design. The International Technology Roadmap for Semiconductors (ITRS) has identified the challenges surrounding low power design as one of the fundamental bottlenecks in exploiting the full capabilities of some of the advanced technology nodes. In fact, data from major chip design houses have underscored this need.

Much attention has been focused world-wide on the three existing formats for expressing low power constraints and intent: Common Power Format (CPF) from Silicon Integration Initiative (Si2), UPF 1.0 from Accellera, and UPF 2.0/P1801 from IEEE. However, the real challenge lies in the development of design flows and tools that exploit the content expressed by designers in these formats to solve real-life, power-related issues in design. Therefore, it should come as no surprise that at Si2 the focus has been on both developing and standardizing CPF in a coalition of both users and EDA suppliers, and in creating an ecosystem that provides training and adoption aids for CPF to support its adoption by chip designers and tool developers alike and proliferation of CPF into design flows in IC companies around the world.