# **RISC Compiler and Simulator, Release V0.6.0: Out-of-Order Parallel Simulatable SystemC Subset**

Guantao Liu, Tim Schmidt, Zhongqi Cheng, Daniel Mendoza and Rainer Dömer

Technical Report CECS-19-04 September 30, 2019

Center for Embedded and Cyber-physical Systems University of California, Irvine Irvine, CA 92697-2620, USA +1 (949) 824-8919

http://www.cecs.uci.edu/~doemer/risc.html

# **RISC Compiler and Simulator, Release V0.6.0: Out-of-Order Parallel Simulatable SystemC Subset**

Guantao Liu, Tim Schmidt, Zhongqi Cheng, Daniel Mendoza and Rainer Dömer

Technical Report CECS-19-04 September 30, 2019

Center for Embedded and Cyber-physical Systems University of California, Irvine Irvine, CA 92697-2620, USA +1 (949) 824-8919

http://www.cecs.uci.edu/~doemer/risc.html

#### Abstract

The IEEE SystemC standard is widely used to specify and simulate Electronic System Level (ESL) design models. Despite the wide availability of multi-core processor hosts, however, the Accellera reference simulator is still based on sequential Discrete Event Simulation (DES) and executes only a single thread at any time.

Parallel SystemC simulators have been proposed which run multiple threads simultaneously based on synchronous Parallel Discrete Event Simulation (PDES) semantics. Synchronous PDES, however, limits parallel execution to threads that run at the same time and delta cycle. Moreover, most approaches require manual preparation of the SystemC model and rely on the designer to perform difficult conflict analysis.

In this report, we describe the Recoding Infrastructure for SystemC (RISC) approach where a dedicated SystemC compiler and advanced parallel simulator implement Out-of-Order Parallel Discrete Event Simulation (OoO PDES) for SystemC. Using automatic conflict analysis based on Segment Graph (SG) abstraction, OoO PDES can execute threads safely in parallel and out-of-order (ahead of time) and thus achieves fastest simulation speed, but nevertheless maintains the standard SystemC semantics with maximum compliance.

This report describes the RISC Compiler and Simulator and details the SystemC subset supported by the open source RISC Release V0.6.0, as of September 30, 2019. In comparison to the previous V0.5.0 release in 2018, RISC is more efficient and robust, and now supports the analysis and safe simulation of TLM-2.0 models, as well as the integration with Simics virtual platforms.

# Contents

| 1  | Introduction 1                                             |    |  |  |

|----|------------------------------------------------------------|----|--|--|

| 2  | Out-of-Order Parallel Simulation                           | 2  |  |  |

|    | 2.1 Notations                                              | 2  |  |  |

|    | 2.2 Discrete Event Scheduler                               | 3  |  |  |

|    | 2.3 Parallel Discrete Event Scheduler                      | 3  |  |  |

|    | 2.4 Out-of-Order Parallel Discrete Event Scheduler         | 5  |  |  |

| 3  | RISC Compiler and Simulator                                | 6  |  |  |

|    | 3.1 Segment Graph                                          | 6  |  |  |

|    | 3.2 Partial Segment Graph                                  |    |  |  |

|    | 3.3 Conflict Analysis                                      |    |  |  |

|    | 3.3.1 Static Analysis                                      |    |  |  |

|    | 3.3.2 Dynamic Analysis                                     |    |  |  |

|    | 3.4 Source Code Instrumentation                            |    |  |  |

|    | 3.5 Library Support                                        |    |  |  |

|    | 3.6 Support for Data-Level Parallelism                     |    |  |  |

|    | 3.7 Support for SystemC TLM-2.0                            |    |  |  |

|    | 3.8 Compiler Backend                                       |    |  |  |

|    | 3.9 Simulator                                              |    |  |  |

|    |                                                            |    |  |  |

| 4  | Out-of-Order Parallel Simulatable SystemC Subset           | 16 |  |  |

|    | 4.1 SystemC Hierarchical Structure of Modules and Channels | 17 |  |  |

|    | 4.2 SystemC Threads                                        | 17 |  |  |

|    | 4.3 SystemC Transaction Level Modeling (TLM)               | 26 |  |  |

|    | 4.4 SystemC Data Types                                     | 26 |  |  |

|    | 4.5 SystemC Utilities and Other Constructs                 | 27 |  |  |

| 5  | <b>RISC Analysis and Transformation Tools</b>              | 27 |  |  |

|    | 5.1 RISC Visual Tool                                       | 27 |  |  |

|    | 5.2 Simics®Virtual Platform Integration                    |    |  |  |

| 6  | RISC Open Source Software                                  | 29 |  |  |

| U  | 6.1 Open Source Code and Documentation                     |    |  |  |

|    | 6.2 Binary Image for "Plug-and-Play" Evaluation            |    |  |  |

|    |                                                            | 50 |  |  |

| 7  | Conclusion                                                 | 30 |  |  |

|    | 7.1 Future Work                                            | 30 |  |  |

| Ac | cknowledgements                                            | 31 |  |  |

|    |                                                            |    |  |  |

| A | App         | endix: RISC Manual Pages                                     | 35 |

|---|-------------|--------------------------------------------------------------|----|

|   | A.1         | Manual Page of the RISC Compiler and Simulator               | 35 |

|   | A.2         | Manual Page of the RISC Elaborator                           | 40 |

|   | A.3         | Manual Page of the RISC SIMD Advisor                         | 43 |

|   | A.4         | Manual Page of the RISC Visual Tool                          | 46 |

|   | A.5         | Manual Page of the RISC Tree Tool                            | 48 |

|   | A.6         | Manual Page of the RISC List Tool                            | 49 |

| В | Арр         | endix: RISC Software Package Documentation                   | 52 |

|   | <b>B</b> .1 | Overview of the RISC Software Package                        | 52 |

|   | B.2         | Copyright of the RISC Compiler and Simulator                 | 54 |

|   | B.3         | Open Source License of the RISC Compiler and Simulator       | 55 |

|   | B.4         | Installation Instructions of the RISC Compiler and Simulator | 56 |

|   | B.5         | Change Log of the RISC Compiler and Simulator                | 59 |

# List of Figures

| 1  | Traditional Discrete Event Simulation (DES) scheduler for SystemC.                               | 3  |

|----|--------------------------------------------------------------------------------------------------|----|

| 2  | Synchronous Parallel Discrete Event Simulation (PDES) scheduler for SystemC.                     | 4  |

| 3  | Out-of-Order Parallel Discrete Event Simulation (OoO PDES) scheduler for SystemC.                | 5  |

| 4  | RISC Compiler and Simulator for Out-of-Order PDES of SystemC.                                    | 6  |

| 5  | RISC software stack.                                                                             | 6  |

| 6  | RISC internal representation.                                                                    | 7  |

| 7  | Scaled RISC tool flow with Partial Segment Graph technology.                                     | 8  |

| 8  | RISC Elaborator feeds dynamic elaboration information to RISC Compiler for precise conflict      |    |

|    | analysis                                                                                         | 9  |

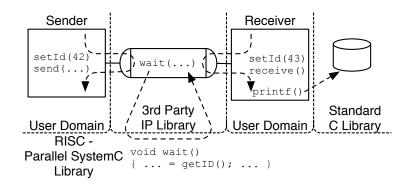

| 9  | Control-flow abstractions for wait in library functions                                          | 12 |

| 10 | Different source code domains of a design model                                                  | 12 |

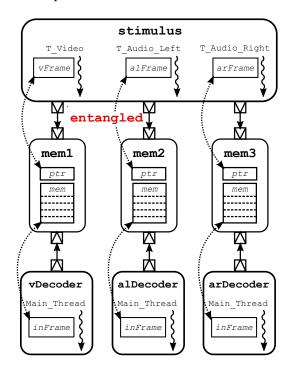

| 11 | SystemC TLM-2.0 model of a DVD player                                                            | 14 |

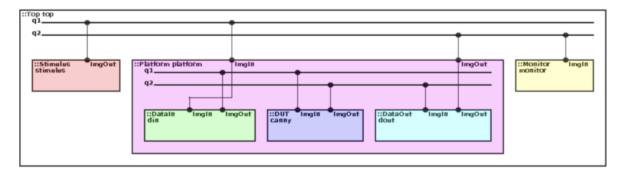

| 12 | Module hierarchy visualization of a SystemC model of a Canny edge detector.                      | 27 |

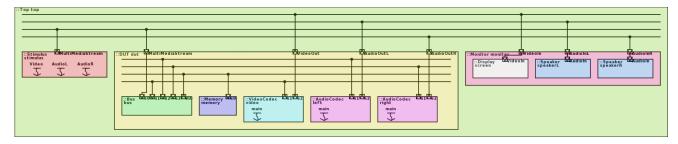

| 13 | Module hierarchy visualization of a TLM-2.0 DVD player example.                                  | 28 |

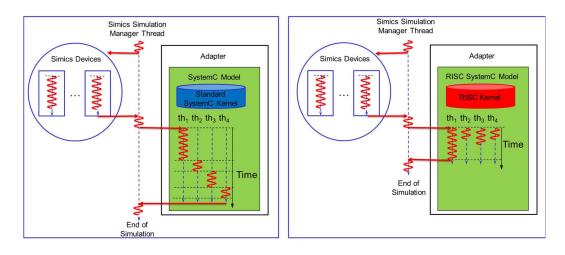

| 14 | Two different Simics simulations of the same model with the left-side using a standard SystemC   |    |

|    | kernel and the right-side featuring RISC kernel for out-of-order parallel multithreading of Sys- |    |

|    | temC threads                                                                                     | 29 |

| 15 | Linux commands to quickly evaluate RISC in a Docker container                                    | 30 |

# List of Tables

| 1 | RISC V0.6.0 Out-of-Order Parallel Simulatable SystemC Subset                     | 18 |

|---|----------------------------------------------------------------------------------|----|

| 2 | RISC V0.6.0 Out-of-Order Parallel Simulatable SystemC Subset (continued)         | 19 |

| 3 | RISC V0.6.0 Out-of-Order Parallel Simulatable SystemC Subset (continued)         | 20 |

| 4 | RISC V0.6.0 Out-of-Order Parallel Simulatable SystemC Subset (continued)         | 21 |

| 5 | RISC V0.6.0 Out-of-Order Parallel Simulatable SystemC Subset (continued)         | 22 |

| 6 | RISC V0.6.0 Out-of-Order Parallel Simulatable SystemC Subset (continued)         | 23 |

| 7 | RISC V0.6.0 Out-of-Order Parallel Simulatable SystemC Subset (continued)         | 24 |

| 8 | RISC V0.6.0 Out-of-Order Parallel Simulatable SystemC Subset (continued)         | 25 |

| 9 | RISC V0.6.0 Out-of-Order Parallel Simulatable SystemC Subset, TLM-2.0 Primitives | 26 |

## **RISC Compiler and Simulator, Release V0.6.0: Out-of-Order Parallel Simulatable SystemC Subset**

Guantao Liu, Tim Schmidt, Zhongqi Cheng, Daniel Mendoza and Rainer Dömer

Center for Embedded and Cyber-physical Systems University of California, Irvine Irvine, CA 92697-2620, USA http://www.cecs.uci.edu/~doemer/risc.html

#### Abstract

The IEEE SystemC standard is widely used to specify and simulate Electronic System Level (ESL) design models. Despite the wide availability of multi-core processor hosts, however, the Accellera reference simulator is still based on sequential Discrete Event Simulation (DES) and executes only a single thread at any time.

Parallel SystemC simulators have been proposed which run multiple threads simultaneously based on synchronous Parallel Discrete Event Simulation (PDES) semantics. Synchronous PDES, however, limits parallel execution to threads that run at the same time and delta cycle. Moreover, most approaches require manual preparation of the SystemC model and rely on the designer to perform difficult conflict analysis.

In this report, we describe the Recoding Infrastructure for SystemC (RISC) approach where a dedicated SystemC compiler and advanced parallel simulator implement Out-of-Order Parallel Discrete Event Simulation (OoO PDES) for SystemC. Using automatic conflict analysis based on Segment Graph (SG) abstraction, OoO PDES can execute threads safely in parallel and out-of-order (ahead of time) and thus achieves fastest simulation speed, but nevertheless maintains the standard SystemC semantics with maximum compliance.

This report describes the RISC Compiler and Simulator and details the SystemC subset supported by the open source RISC Release V0.6.0, as of September 30, 2019. In comparison to the previous V0.5.0 release in 2018, RISC is more efficient and robust, and now supports the analysis and safe simulation of TLM-2.0 models, as well as the integration with Simics virtual platforms.

## **1** Introduction

As an IEEE standard [1], the SystemC System Level Description Language (SLDL) is widely used for the specification, modeling, validation and evaluation of Electronic System Level (ESL) models. Under the Accellera Systems Initiative [2], the SystemC Language Working Group [3] maintains not only the official SystemC language definition, but also provides an open source proof-of-concept library [4] that can be used to simulate SystemC design models. However, implementing the classic scheme of Discrete Event Simulation (DES), this reference simulator runs sequentially and cannot utilize the parallel computing resources available on multi-core (or many-core) processor hosts. This severely limits the execution speed of SystemC simulation.

In order to provide faster simulation, Parallel Discrete Event Simulation (PDES) [5] has recently gained again significant attraction (examples include [6], [7], [8], [9], [10], and [11]). The PDES approach issues multiple threads (i.e. SC\_METHOD, SC\_THREAD and SC\_CTHREAD) concurrently and runs them on the available processor cores in parallel. In turn, the simulation speed increases significantly.

Regular PDES is synchronous, however. That is, time advances globally and all threads execute in lock-step fashion. Here, the total order of time imposed by synchronous PDES still limits the opportunities for parallel execution. When a thread completes its evaluation phase, it has to wait until all other threads finish their evaluation phases as well. Earlier completed threads must stop at the simulation cycle barrier and available processor cores are left idle until all runable threads reach the cycle barrier.

In order to overcome this problem, we have developed a novel technique called Out-of-Order Parallel Discrete Event Simulation (OoO PDES) [12, 13, 14, 15]. By localizing the simulation time to individual threads and carefully handling events at different times, the simulation kernel can issue threads in parallel and ahead of time, following a partial order of time without loss of accuracy. Thus, Ooo PDES significantly reduces the idle time of available parallel processor cores and results in maximum simulation speed, while maintaining the traditional language and modeling semantics.

The OoO PDES technique was originally implemented based on the SpecC language [16, 17, 18, 19]. In this report, we document our efforts to apply OoO PDES to the IEEE SystemC SLDL [20, 21, 1] which is both the de-facto and official standard for ESL design today. In particular, we describe our Recoding Infrastructure for SystemC (RISC) [22] which consists of a dedicated SystemC compiler and corresponding out-of-order parallel simulator and implements OoO PDES with prediction for SystemC [23].

The remainder of this report is organized as follows: After a brief description of the simulator scheduling algorithms used for DES, PDES and OoO PDES in Section 2, we describe the RISC Compiler and Simulator proof-of-concept prototype in Section 3. In Section 4, we then list in detail the SystemC subset that is supported by the current RISC Release V0.6.0  $(2019-09-30)^1$ . In Section 5, we describe additional analysis and transformation tools built on top of RISC, and outline the open source distribution of RISC in Section 6. We finally conclude this report in Section 7.

## 2 Out-of-Order Parallel Simulation

In this section, we briefly outline the scheduling algorithm used in out-of-order parallel simulation. We do this incrementally, starting from the traditional Discrete Event Simulation (DES) scheduler, then describe the synchronous Parallel DES (PDES) extension, and finally define the Out-of-Order PDES (OoO PDES) scheduling algorithm.

#### 2.1 Notations

To formally describe the discrete event scheduling algorithms, the following notations are introduced.

- 1. Each SystemC thread (SC\_METHOD, SC\_THREAD and SC\_CTHREAD) is assigned a localized time stamp  $(t_{th}, \delta_{th})$ .

- 2. Each event (sc\_event) is assigned a notification time stamp  $(t_e, \delta_e)$ , where  $EVENTS = \bigcup EVENTS_{t,\delta}$ .

- 3. Threads are grouped into different queues. Specifically,

- (a)  $QUEUES = \{READY, RUN, WAIT, WAITTIME\}.$

- (b)  $READY = \bigcup th_{t,\delta}$  where Thread *th* is ready to run at time  $(t,\delta)$ .

- (c)  $RUN = \bigcup th_{t,\delta}$  where Thread *th* is running at time  $(t, \delta)$ .

<sup>&</sup>lt;sup>1</sup> Earlier versions of this technical report document the prior alpha release in 2015 [24], the beta release in 2016 [25], the release v0.4.0 in 2017 [26], and the release v0.5.0 in 2018 [27].

- (d)  $WAIT = \bigcup th_{t,\delta}$  where Thread *th* is waiting since time  $(t, \delta)$ .

- (e) WAITTIME =  $\cup th_{t,0}$  where Thread th is waiting for simulation time advance to (t,0).

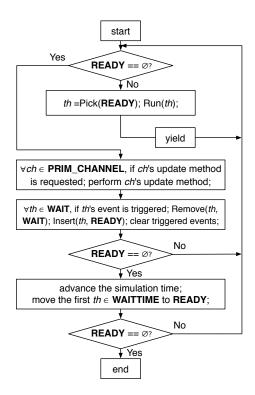

Figure 1: Traditional Discrete Event Simulation (DES) scheduler for SystemC.

#### 2.2 Discrete Event Scheduler

The Accellera reference simulation library of SystemC [4] is based on DES. Figure 1 depicts such a traditional DES scheduling algorithm. In DES, a single thread is running at all times. When all threads in the *READY* and *RUN* queues complete their current delta cycle, the root thread resumes and performs the update and notification phase. Then threads are woken up and moved from the *WAIT* queue back into the *READY* queue. A new delta cycle begins.

If no threads are ready after the update and notification phase, the current time cycle finishes. The simulation kernel advances the simulation time and processes the earliest timed event from the *WAITTIME* queue. A new cycle begins for the updated simulated time.

Finally, when both the WAITTIME and READY queues are empty, the simulation terminates.

#### 2.3 Parallel Discrete Event Scheduler

In comparison to DES, regular synchronous PDES issues multiple threads (SC\_METHOD, SC\_THREAD and SC\_CTHREAD) concurrently in a delta cycle. These threads can then execute truly in parallel on the multiple available processor cores of the host.

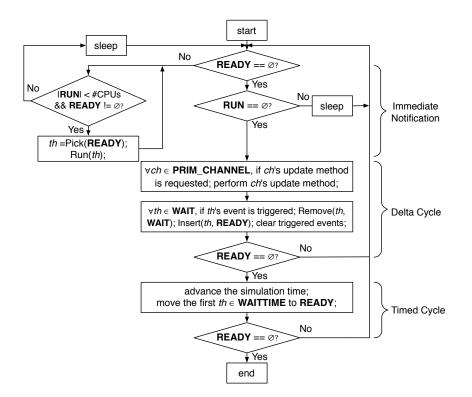

Figure 2 shows the regular synchronous PDES scheduling algorithm. In the evaluation phase, as long as the *READY* queue is not empty and an idle core is available, the PDES scheduler will issue a new thread from the

Figure 2: Synchronous Parallel Discrete Event Simulation (PDES) scheduler for SystemC.

*READY* queue. If a thread finishes earlier than other threads in the same cycle, a new ready thread is assigned to the idle processor core, unless there is no thread available in the *READY* queue, in which case the core is kept idle until the next delta cycle.

It should be emphasized that synchronous PDES implies an absolute barrier at the end of each delta and time cycle. All threads need to wait at the barrier until all other runable threads finish their current evaluation phase. Only then the synchronous PDES scheduler resumes and performs the update and notification phases, and finally advances to the next delta or time cycle.

For the SystemC language in particular, there is yet another very important aspect to consider when applying PDES. For semantics-compliant SystemC simulation, complex inter-dependency analysis over all variables in the system model is a prerequisite to parallel simulation [28].

The Standard SystemC Language Reference Manual (LRM) [1] clearly states that "process instances execute without interruption". This requirement is also known as cooperative (or co-routine) multitasking which is assumed by the SystemC execution semantics. As detailed in [28], the particular problem of parallel simulation is specifically addressed in the SystemC LRM [1]:

"An implementation running on a machine that provides hardware support for concurrent processes may permit two or more processes to run concurrently, provided that the behavior appears identical to the co-routine semantics defined [...]. In other words, the implementation would be obliged to analyze any dependencies between processes and constrain their execution to match the co-routine semantics."

We will describe the required dependency analysis in more detail below (in Section 3.3), as it is also needed for out-of-order PDES.

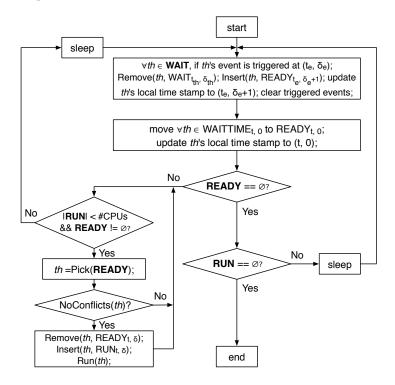

#### 2.4 Out-of-Order Parallel Discrete Event Scheduler

In OoO PDES, we break the strict order of time (the synchronous barrier) by localizing time stamps to each thread. Figure 3 shows the out-of-order parallel DES scheduling algorithm. Since each thread has its own time stamp, the OoO PDES scheduler relaxes the event and simulation time updates, allowing more threads (at different simulation cycles!) to run in parallel and ahead of time. This results in a higher degree of parallelism and thus higher simulation speed.

Figure 3: Out-of-Order Parallel Discrete Event Simulation (OoO PDES) scheduler for SystemC.

In comparison to the synchronous PDES in Figure 2, Figure 3 moves threads from the *WAIT* and *WAITTIME* queues into the *READY* queue as soon as possible. Also, there is no specific point in the scheduling flow any more for the classic delta and time cycles. Both delta and time updates are performed locally for each thread, provided that there are no possible conflicts in the way (the *NoConflicts*(*th*) condition is explained below).

In contrast to Figure 2 which performs requested update methods in primitive channels in each delta cycle, Figure 3 does not contain this step any more. Due to the out-of-order scheduling and the eliminated central scheduling point for delta cycles, it is difficult to determine an efficient and safe point in the OoO PDES scheduler when primitive channel update requests can be served. However, it is always possible to safely fall back to synchronous PDES when primitive channel updates are requested.

Note the *NoConflicts*(*th*) condition shown in Figure 3. As already mentioned above for the synchronous PDES, detailed dependency analysis is needed to avoid data or event conflicts for any shared variables among the parallel threads. Only if *NoConflicts*(*th*) is true, a new thread is issued for parallel execution (moved from the *READY* to the *RUN* queue).

We will be using advanced static compile-time analysis (and optionally dynamic run-time analysis, see Section 3.3.2) to identify all such potential conflicts. Based on this information (a simple table look-up is sufficient), the OoO PDES scheduler can then at run-time quickly decide whether or not a set of threads has any conflicts with each other.

## **3 RISC Compiler and Simulator**

To realize the OoO PDES approach for the IEEE SystemC language, we present now our Recoding Infrastructure for SystemC (RISC) and describe the overall RISC Compiler and Simulator proof-of-concept prototype (Release V0.6.0 as of 2019-09-30).

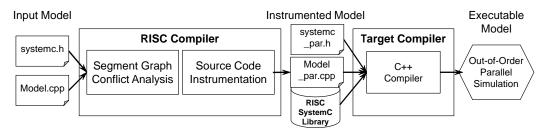

Figure 4: RISC Compiler and Simulator for Out-of-Order PDES of SystemC.

To perform parallel SystemC simulation in maximum compliance with the IEEE standard semantics, we introduce a *dedicated SystemC compiler*. This is in contrast to the traditional SystemC simulation where a regular SystemC-agnostic C++ compiler includes the SystemC headers and links the input model directly against the SystemC library.

As shown in Figure 4, our RISC compiler acts as a frontend that processes the input SystemC model and generates an intermediate model with special instrumentation for OoO PDES. The instrumented parallel model is then linked against the extended RISC SystemC library by the target compiler (a regular C++ compiler) to produce the final executable output model. OoO PDES is then performed simply by running the generated executable model.

From the user perspective, we essentially replace the regular SystemC-agnostic C++ compiler with the SystemC-aware RISC compiler (which in turn calls the underlying C++ compiler). Otherwise, the overall SystemC validation flow remains the same as before. It is just faster due to the parallel simulation.

For reference, the detailed Linux manual page of the RISC compiler risc and simulator is included in Appendix A.1 of this report.

Internally, the RISC compiler performs three major tasks, namely Segment Graph (SG) construction, conflict analysis, and source code instrumentation.

|   | RISC          |      |    |  |  |  |

|---|---------------|------|----|--|--|--|

|   | Segment Graph |      |    |  |  |  |

| S | ystemC IR     |      |    |  |  |  |

|   | ROSE IR       |      |    |  |  |  |

|   | C/C++ Foun    | dati | on |  |  |  |

Figure 5: RISC software stack.

### 3.1 Segment Graph

RISC relies on a comprehensive software stack composed of complex data structures, as illustrated in Figure 5. On top of the C/C++ standard libraries and the internal representation of the Rose compiler [29], RISC builds a SystemC internal representation which, in turn, carries the segment graph data structures.

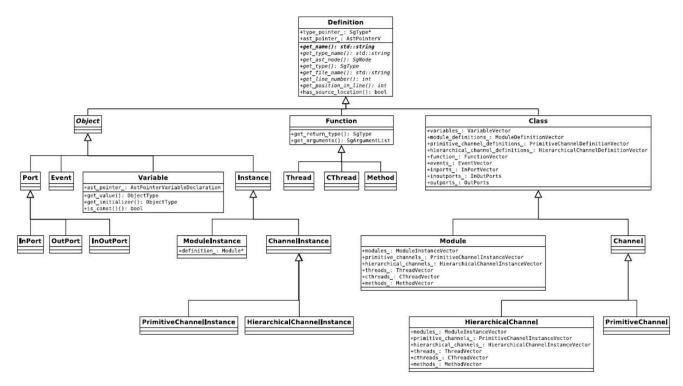

The first task of the RISC compiler is to parse the SystemC input model into an abstract syntax tree (AST) by use of the Rose IR. Next, RISC creates a SystemC internal representation from the AST which reflects the SystemC module and channel hierarchy, connectivity, and other SystemC-specific relations, as depicted in Figure 6. This is similar to the SystemC-clang representation [30, 31]. For details on this part of the RISC application programming interface (API), please refer to the Doxygen-generated documentation [32].

Figure 6: RISC internal representation.

On top of this, the RISC compiler then builds a *Segment Graph* (*SG*) data structure for the model. A Segment Graph (SG) [12, 15] is a directed graph that represents the code segments executed during the simulation between scheduling steps. That is, every segment is associated with a scheduler entry point, i.e. a wait statement in SystemC.

At run time, threads switch back and forth between the states of *running* (threads in *READY* and *RUN* queues) and *waiting* (threads in *WAIT* and *WAITTIME* queues). When *running*, they execute specific segments of their code. These code segments make up the nodes in the Segment Graph, whereas edges in the graph indicate the possible transitions from one segment to another. In other words, the edges in the Segment Graph reflect an abstraction of the model's control flow.

For a formal description of the Segment Graph and its construction algorithm, the interested reader may refer to [15]. For details on the RISC compiler API, please refer to the Doxygen-generated documentation [32].

#### 3.2 Partial Segment Graph

The segment graph is the foundation data structure for the static analysis. However, there are restrictions: the entire source code for the input design must be available in one file, which does not scale. This disables the use of Intellectual Property (IP) and hierarchical file structures.

To solve this problem, we have proposed and implemented a Partial Segment Graph (PSG) as the representation

of the behavior model for each separate translation unit or IP. By combining PSGs, our tool is able to reconstruct the complete SG for the input model [33].

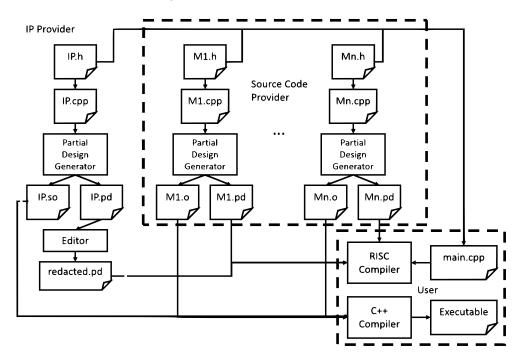

The extended tool flow is shown in Figure 7.

Figure 7: Scaled RISC tool flow with Partial Segment Graph technology.

A PSG is recursively built by traversing the AST of the current translation unit. The main difference between PSG and SG is that PSG is built based on an incomplete AST, where definitions of function calls may be unknown.

To deal with this uncertainty incurred by the non-defining function calls, we introduce three types of PSG nodes, which facilitate the integration of PSGs. They are *Segment Node*, *Partial Segment Node* and *Partial Function Call Node*.

The PSG is constructed by the IP provider. It is stored as a PSG file and is compatible with the Dot format so that the PSG can easily be visualized. The PSG file is shipped together with the IP files to the user. On the user's side, the RISC compiler is able to load and parse the PSG files. Then, the loaded PSGs are integrated to form a complete SG. During integration, *Partial Function Call Nodes* are replaced by the corresponding PSGs of the functions. *Partial Segment Nodes* are merged into *Segment Nodes*. After the integration, the graph becomes a valid and complete SG.

An IP provider can also inspect and redact the automatically generated PSG files so that the implementation details remain hidden. This way the IP users will not be able to obtain the inner implementation and the IP remains protected, while the correctness of behavior model of the design is still maintained [33].

#### **3.3** Conflict Analysis

The Segment Graph data structure serves as the foundation for segment *conflict analysis*. As outlined earlier, the OoO PDES scheduler must ensure that every parallel thread to be issued has no conflicts with any other threads currently in the *READY* and *RUN* queues. Here, we utilize the RISC compiler to detect any possible conflicts between these threads already at compile time.

Potential conflicts in SystemC include data hazards, event hazards, and timing hazards, all of which may exist among the segments executed by the threads considered for parallel execution. Please refer to [15] for a detailed discussion of these hazards which, if ignored, would become dangerous race conditions at run time.

Both possible hazard detection approaches, namely *static* analysis at compile time and *dynamic* analysis at run time, are supported by the RISC Compiler and Simulator. It should be emphasized that the accuracy of this analysis has significantly improved with the RISC release V0.5.0. As outlined in detail in [34], the RISC compiler now supports Port Call Path (PCP) sensitive conflict analysis which makes it aware of the actual channel instances used by threads from different modules. This much more precise analysis can avoid false positive conflicts in many cases and thus increases the efficiency of the simulation which, in turn, runs faster.

#### 3.3.1 Static Analysis

Static analysis relies purely on the available information in the SystemC source code of the design model at hand. In this case, the RISC compiler carefully performs conservative identification of the potential hazards in the model.

Identifying all possible hazards is a complex analysis task that requires the full "understanding" of the module hierarchy. One option is to statically extract the module hierarchy and analyze the individual threads. Here, the RISC compiler follows the approach outlined in [15].

In many cases, however, not all of the needed information can be gathered statically. For instance, design parameters may be passed via the command line, for example, to define the number of modules, certain channel characteristics, or other configuration information. In such SystemC models with a dynamic elaboration phase, the instantiated modules, channels, and ports are typically created by use of loops and new operators in a dynamic fashion. Thus, the structural parameters of the model are only available at run time, so they cannot be statically analyzed. In these cases, dynamic analysis is needed.

#### 3.3.2 Dynamic Analysis

Dynamic analysis takes run-time information into account and then augments the classic static analysis. The combination of static and dynamic analysis is here called *hybrid analysis* [35].

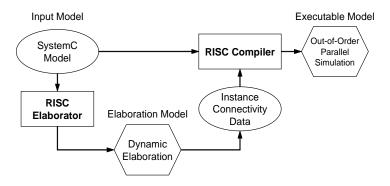

Figure 8: RISC Elaborator feeds dynamic elaboration information to RISC Compiler for precise conflict analysis.

Figure 8 shows the extended RISC design flow with support of dynamic analysis. As in the regular compilation flow discussed above in Figure 4, the input SystemC model is processed by the RISC Compiler to generate an executable model for out-of-order parallel simulation, as shown on the top half of Figure 8 from left to right.

The dynamic analysis step, shown on the bottom half of Figure 8, extends the compilation flow by a preprocessing step. The input SystemC model is fed into the RISC Elaborator elab which produces an executable model that only performs the SystemC elaboration phase when run. At the end of the elaboration, the executable model automatically traverses the created module hierarchy via the SystemC introspection API and dumps this detailed structural design information, shown as Instance Connectivity Data in Figure 8, into a file (model\_name.elab). This file is in turn provided as an input to the RISC compiler, so that the dynamically created design hierarchy and specific instance connectivity can be used for precise conflict analysis. The instance connectivity data file includes the actual module hierarchy, the specific port mapping, and the actual target variable mapping of references.

Note that the use of the RISC Elaborator is optional. Design models which can be fully analyzed in static fashion can be fed directly into the RISC Compiler without any pre-processing by the RISC Elaborator.

For reference, the detailed Linux manual pages of the RISC Compiler risc and RISC Elaborator elab are included in Appendix A.1 and Appendix A.2, respectively.

### 3.4 Source Code Instrumentation

As a result of the conflict analysis (static, dynamic, or hybrid [35]), the RISC compiler generates several conflict tables that describe all possible conflicts between threads in any two segments. Using this conservative conflict information, the simulator can then at run-time quickly determine by a simple table look-up whether or not it is safe to issue any given thread in parallel or ahead of time.

As shown above in Figure 4, the RISC compiler and simulator work closely together. The compiler performs conservative conflict analysis and passes the analysis results to the simulator which then can make safe scheduling decisions quickly.

To pass information from the compiler to the simulator, we use automatic model instrumentation. That is, the intermediate model generated by the compiler contains instrumented (automatically generated) source code which the simulator can then rely on. At the same time, the RISC compiler also instruments user-defined SystemC channels with automatic protection against race conditions among communicating threads.

In total, the RISC source code instrumentation includes four major components:

- 1. Segment and instance IDs: Individual threads are uniquely identified by a creator instance ID and their current code location (segment ID). Both IDs are passed into the simulator kernel as additional arguments to scheduler entry functions, including wait and thread creation.

- 2. Data and event conflict tables: Segment concurrency hazards due to potential data conflicts, event conflicts, or timing conflicts are provided to the simulator as two-dimensional tables indexed by a segment ID and instance ID pair. For efficiency, these table entries are filtered for scope, instance path, and reference and port mappings.

- 3. Current and next time advance tables, and thread state prediction tables: The simulator can make better scheduling decisions by looking ahead in time if it can predict the possible future thread states. This optimization is discussed in detail in [14] and is available in the RISC Compiler and Simulator in versions 0.4.0 and later. Since thread state prediction for most models requires only little additional compile time but results often in higher simulation speed, it is enabled by default (it can be turned off with the SYSC\_DISABLE\_PREDICTION environment variable, see below).

- 4. User-defined channel protection: SystemC allows the user to design channels for custom inter-thread communication. To ensure such communication is safe also in the OoO PDES situation where threads execute truly in parallel, the RISC compiler automatically inserts locks (binary semaphores) into these channels,

if needed<sup>2</sup>, so that mutually-exclusive execution of the channel methods is guaranteed. Otherwise, race conditions could exist when communicating threads exchange data.

Note that the source code instrumentation is performed automatically by the RISC Compiler and no userinteraction is necessary. However, the interested user may inspect the instrumented source code. It is stored in a file named risc\_model\_name.cpp which serves as the input file to the compiler backend which in turn then generates the final executable.

With RISC version 0.6.0, source code instrumentation is optimized for large design models with many segments. Here, the conflict, time, and prediction tables can become fairly large, which unnecessarily slows down the code generation step during compilation. To avoid such inefficiency, a separate file (model\_name.risc) is automatically generated with binary images of the tables. This file is then read at run time (automatically, just like a shared library) to fill the conflict, time, and prediction tables needed by the simulator.

#### 3.5 Library Support

In absence of PSG support (Section 3.2), there exists a significant limitation for the described conflict analysis and source code instrumentation. It only works if the compiler has access to the entire source code of the design model. This is typically fine for smaller SystemC benchmark examples, but does not hold true for more complex SystemC models where multiple translation units and/or library files are used. In these cases, the compiler has access only to the function signatures (function declarations in header files), but not to their implementation (function bodies which are pre-compiled in the library or object files). Thus, the compiler cannot analyze the function bodies for potential conflicts, neither can it instrument any segment boundaries (i.e. wait calls) in the library code with segment and instance IDs.

In its initial alpha version [24], the RISC Compiler and Simulator operated under the assumption that all library code is thread-safe without any conflicts and does not contain any segment boundaries (no wait statements). This is reasonable for the standard C/C++ libraries used in a modern Linux environment, as well as for the specially prepared RISC SystemC simulator library. However, this assumption poses a significant limitation for more complex SystemC models built around custom application libraries.

In order to mitigate this limitation, the beta version [25] and the RISC Compiler and Simulator version 0.4.0 offered basic support for library code by use of *function annotations*. This annotation scheme for library functions provides abstract information for both conflict analysis and segment boundaries [35].

Specifically, the user can annotate function declarations with pragma directives which specify whether or not the function poses any potential conflicts. The pragma directives can also describe common situations of wait calls that the control flow in the function body contains.

For example, the standard math function sqrt and the blocking read function of the SystemC sc\_fifo channel can be annotated as follows:

```

// standard math square-root function

#pragma RISC sqrt conflict-free no-wait

double sqrt(double x);

// sc_fifo blocking read function

#pragma RISC read conflict-free looped-wait event

virtual T read();

```

<sup>&</sup>lt;sup>2</sup> As of version 0.5.1, explicit mutex locks in user-defined channels are not needed any more when the channel methods can be fully analyzed with PCP [34] and SCP [36] techniques. Such redundant locks are *not* instrumented any more.

Here, the sqrt function is declared conflict-free because it is thread-safe and has no dangerous side effects. Since this is true for many functions (e.g. most functions in the C standard library), the RISC Compiler assumes this by default. Thus, this pragma statement is not explicitly needed.

The sc\_fifo::read function is also declared conflict-free because it operates in a standard SystemC channel that is safely protected by a lock in the RISC simulator library. However, this blocking sc\_fifo::read function is annotated as looped-wait because it does contain a wait statement in the body of a loop that is waiting for available data, which is indicated by some event. Thus, the RISC Compiler can take this segment boundary into account when building the Segment Graph for a thread that calls this function.

In general, a function is considered conflict-free if the corresponding function body contains no potential read/write access conflicts to any shared state with the other threads in the simulation model. Otherwise, it must be annotated as not-conflict-free.

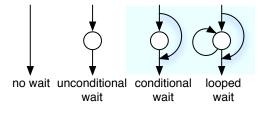

Figure 9: Control-flow abstractions for wait in library functions.

For the annotation of segment boundaries contained in library functions, Figure 9 shows the different controlflow abstractions with regards to wait function calls in the corresponding function body. In the first case, no\_wait, the function contains no wait statement and thus is a non-blocking function during the SystemC simulation. The next two cases, conditional\_wait and unconditional\_wait, apply to functions with a conditional or non-conditional wait statement, respectively. The last case covers the possible encounter of a wait statement in a loop, such as the blocking read call to a sc\_fifo channel discussed above.

The last parameter in the RISC pragma annotation specifies the type of the wait statement in the function body, either event for waiting for any notified event, or the minimum time increment that the simulator will incur when executing the corresponding function, such as sc-zero-time or (42,SC\_MS).

Figure 10: Different source code domains of a design model.

Figure 10 [35] illustrates the different domains of source code in a SystemC model where only the code in the user domain is available for the instrumentation described above in Section 3.4. For library code, any

contained wait() calls cannot be instrumented. Here, the RISC Compiler and Simulator (version 0.4.0 and above) instruments the code before such library function calls with setID(SegID) functions that store the upcoming segment IDs for the wait statements in the library in thread-local data. Then, when wait statements without explicit segment ID arguments are executed in the library, the segment IDs are obtained from the thread-local data by use of a getID() function in the RISC simulation library.

Note that the library support by use of pragma directives remains available (for backward compatibility reasons) in the RISC Compiler and Simulator beyond version 0.4.0. However, the Partial Segment Graph (PSG) technology described in Section 3.2 offers an alternative solution that is much more general. In particular, the PSG technology resolves two prior limitations. First, the annotations shown in Figure 9 only cover the cases of zero or one wait statement in a library function. Multiple wait statements were not covered. Thus, PSG technology was designed in order to cover general control-flow inside of library functions which are now represented by their own partial segment graphs. Second, PSG technology supports multiple separate translation units by building and storing PSG files together with generated object files that then can be integrated again into a complete SG when the final simulation executable is being built [33].

### 3.6 Support for Data-Level Parallelism

As of version 0.4.0, the RISC Compiler and Simulator comes with support for exploiting data-level parallelism, also known as Single-Instruction-Multiple-Data (SIMD) vectorization [37]. Here, an advanced analysis tool, namely the SIMD Advisor simd (see Appendix A.3), can identify possible locations in the SystemC model's source code where data-level parallelism may be exploited for faster simulation (on top of the thread-level parallelism already exploited due to OoO PDES).

The SIMD Advisor adds a pre-analysis step to the RISC Compiler and Simulator tool flow where simd provides the designer with candidates for loop vectorization. Specifically, simd performs advanced thread controlflow and variable access analysis and then reports to the user the source code line numbers where loops qualified for SIMD vectorization are found. The user confirms suitable locations by inserting #pragma simd directives in front of the chosen loops. Finally, the design model is then compiled with the Intel compiler icpc which performs the vectorization and builds the executable for simulation with both thread- and data-level parallelism.

Note that the manual confirmation by the designer is necessary. An example is the following C function:

```

void add(float *a, float *b, float *c, int n)

{

for(int i=0; i<n; i++)

{ a[i] = a[i] + b[i] + c[i];}

}</pre>

```

Here, arrays passed as pointers can only be vectorized if the user asserts that there is no vector dependence in the way. This confirmation step is only possible with application knowledge, not just by static compiler analysis. The RISC SIMD Advisor is aware of SystemC and its concurrent multi-threading semantics, and thus can identify certain loops as potential candidates, but the final data independence assertion must come from the user who knows the application specifics (i.e. that the pointers point to non-overlapping arrays).

Exploiting both thread- and data-level parallelism can be very effective for many design models. Experimental results in [37] show a nearly linear speedup of  $N \times M$ , where N and M denote the thread and data-level factors, respectively.

The SIMD Advisor is documented in detail in the manual page for simd listed in Appendix A.3.

### 3.7 Support for SystemC TLM-2.0

As of version 0.6.0, the RISC Compiler and Simulator comes with support for SystemC TLM-2.0 models, including blocking transport interface (BTI), non-blocking transport interface (NBTI), and direct memory access interface (DMI) [36]. As an example, Figure 11 shows a SystemC TLM-2.0 model of a DVD player which decodes a stream of H.264 video and MP3 audio data using separate decoders. All communications are modeled using TLM-2.0 sockets and APIs. With the SystemC TLM-2.0 support, the SystemC compiler is able to accurately analyze the behavior of each process.

Figure 11: SystemC TLM-2.0 model of a DVD player.

For TLM-2.0 model analysis, RISC uses the Socket Call Path (SCP) technique [36] to increase the accuracy of the static analysis for SystemC TLM-2.0 communication. SCP provides the SystemC compiler with the information regarding how a target is reached by the initiator through the TLM-2.0 interface. The idea is similar to the Port Call Path (PCP) [34]. One main difference is that PCP is based on port-to-channel connections whereas SCP is for analyzing socket-to-module connections. Also different from PCP, a SCP is represented by a list of sockets. When used together with Segment Graph, SCP helps the SystemC compiler to perform instance-aware conflict analysis, which provides similar benefits as to the use of PCP.

SCP is important for the SystemC compiler to understand the variable entanglements in order to reduce the number of false data conflicts. Take BTI as an example, the variable entanglement analysis happens in three steps:

- 1. Identify original and alias variable: In this step, the compiler identifies a) the original variable encapsulated in a generic payload by set\_data\_ptr, and b) the alias variable extracted from a generic payload by get\_data\_ptr.

- 2. Reference analysis for generic payload with SCP: In the second step, the compiler analyzes the mapping between *parametric generic payload* (PGP) and *referred generic payload* (RGP).

3. Variable access analysis for entangled variables: Through the PGP-RGP reference mappings, the corresponding alias and original variables are entangled. Algorithm 1 in [36] describes this step in details.

Note that while BTI, NBTI and DMI communication is supported, our analysis does not support Blocking-to-Non-Blocking nor Non-Blocking-to-Blocking communication styles. Our analysis does support different communication structures, including direct communication, hierarchical communication, and interconnected communication. Our experiments [36] demonstrate the correctness and effectiveness of the approach with demonstration examples from Accellera [4] and three real world examples: DVD Player, Mandelbrot Renderer and Bitcoin miner.

#### 3.8 Compiler Backend

After the automatic source code instrumentation, the RISC compiler passes the generated intermediate model in file risc\_model\_name.cpp to the underlying regular C++ compiler. That target compiler then produces the final simulation executable by linking the instrumented code against the RISC extended SystemC library.

By default, the RISC Compiler and Simulator rely on the GNU C++ compiler g++ for the backend code generation. Alternatively, the Intel C++ compiler icpc may be used to generate a simulation executable that is optimized for Intel processors with Single-Instruction-Multiple-Data (SIMD) capabilities or the Intel Many-Integrated-Core (MIC) architecture. Please refer to the command-line options -risc:icpc and -risc:mic, respectively, which are documented in the manual pages for risc (see Appendix A.1) and elab (see Appendix A.2).

#### 3.9 Simulator

Same as the classic Accellera proof-of-concept implementation [4], the RISC simulator is not an explicit tool, but a run-time library [38] that the generated executable SystemC model is linked against. Thus, simulation is performed by execution of the compiled model, the same way as in the classic tool flow (just faster).

The RISC simulator identifies itself by its log message at the beginning of the simulation run, announcing RISC 0.6.0 execution after the SystemC language version number (SystemC 2.3.1). It also adds the Center for Embedded and Cyber-physical Systems (CECS) as a contributor to the RISC-extended SystemC library.

A simple *HelloWorld* model is shown running in the following example:

```

sh % ./HelloWorld

```

SystemC 2.3.1-RISC 0.6.0 --- Sep 30 2019 09:42:00 Copyright (c) 1996-2019 by CECS and all Contributors, ALL RIGHTS RESERVED

```

Hello World!

```

There are several environment variables which the RISC out-of-order parallel SystemC library recognizes. These are logged at the beginning of the simulation if SYSC\_PRINT\_MODE\_MESSAGE is defined.

| * * * | RISC simulator mode: out-o | f-order par | allel with predicti | .on *** |

|-------|----------------------------|-------------|---------------------|---------|

| * * * | SYSC_PRINT_MODE_MESSAGE    | is          | defined             | * * *   |

| * * * | SYSC_SYNC_PAR_SIM          | is          | not defined         | * * *   |

| * * * | SYSC_VERBOSITY_FLAG_1      | is          | not defined         | * * *   |

| * * * | SYSC_VERBOSITY_FLAG_2   | is | not defined | * * * |

|-------|-------------------------|----|-------------|-------|

| * * * | SYSC_VERBOSITY_FLAG_3   | is | not defined | * * * |

| * * * | SYSC_VERBOSITY_FLAG_4   | is | not defined | * * * |

| * * * | SYSC_DISABLE_PREDICTION | is | not defined | * * * |

| * * * | SYSC_PAR_SIM_CPUS       | is | 64          | * * * |

The environment variable SYSC\_SYNC\_PAR\_SIM can be used to force the default out-of-order parallel scheduler to fall-back to synchronous parallel execution. By default (when undefined), SYSC\_SYNC\_PAR\_SIM is assumed to be false, so out-of-order parallel simulation (OoO PDES) with prediction is performed. On the other hand, if SYSC\_SYNC\_PAR\_SIM is defined, the simulator will execute in synchronous PDES fashion.

Also, as indicated above in Section 2.4, the RISC simulator automatically falls back to synchronous execution as soon as primitive SystemC channels are used with requests to update functions. Thus, such models will execute in safe synchronous manner.

The variables SYSC\_VERBOSITY\_FLAG\_1 through SYSC\_VERBOSITY\_FLAG\_4 are used by the RISC simulator at run-time to print debugging information about the simulator queues, event processing, and time advances. Such debugging lines are only printed when the corresponding variable is defined. Please refer to the manual page of the RISC Compiler and Simulator for details (see Appendix Section A.1).

The variable SYSC\_DISABLE\_PREDICTION is used by the RISC simulator to switch back to non-predictive conflict detection. This avoids scheduling overhead at run time, but usually results in slower simulation due to more false conflicts. If SYSC\_DISABLE\_PREDICTION is defined, thread state prediction is not used during out-of-order scheduling.

The environment variable SYSC\_PAR\_SIM\_CPUS specifies the maximum number of parallel threads allowed in out-of-order parallel simulation (namely #CPUs in Figure 3). For efficient simulation, this variable should be set to a value suitable for the simulation host, e.g. the number of available CPU cores. If unset, SYSC\_PAR\_SIM\_CPUS defaults to 64.

## 4 Out-of-Order Parallel Simulatable SystemC Subset

Over more than a decade, the SystemC language [21], which technically is a C++ application programming interface (API) with a corresponding simulation library, has evolved from basic constructs for modeling parallel modules connected by signals and channels to a highly complex set of macros, types, classes, templates, and functions for very advanced modeling (i.e. Transaction Level Modeling (TLM) [39, 40]) and highly optimized simulation of SystemC models. Usually these optimization steps have aimed at higher simulation speed, i.e. by minimizing context switches in the simulator, or at higher levels of abstraction due to purposely relaxed timing. Often, the uninterrupted (sequential) execution semantics on a single processor host have been presumed or are explicitly required.

Along these lines, it has been recognized that there is considerable need to study and adjust or *evolve* the SystemC language towards better support of parallel execution (following some form of suitable PDES semantics). One example of the ongoing discussion within the SystemC community is a presentation at the SystemC Evolution Day 2016 where significant obstacles in the current language standard have been identified [41]. These *seven obstacles* have then been documented also in a letter to the editor of IEEE Embedded System Letters [42].

The RISC Compiler and Simulator aims for advanced parallel execution on multi- and many-core hosts, maximizing the compliance with the current SystemC standard [1]. Changing some assumptions about SystemC simulator execution consequently affects a number of SystemC constructs and APIs which need to be revisited and evaluated anew. The goal of this section is to document this process and status, and enable fruitful discussions. Below, we describe and list the out-of-order parallel simulatable SystemC subset supported by the current RISC Compiler and Simulator, Release V0.6.0. In particular, Table 1 through Table 8 list for each SystemC construct whether or not it is supported at this time. If applicable, an explanation note is provided that briefly outlines the status and/or the plans for the given feature.

Overall, the current RISC proof-of-concept prototype supports the classic SystemC constructs for hierarchical modeling with modules and interconnected channels by featuring fast multi-threaded execution. Modern TLM-2.0 style communication is also supported (as of RISC version 0.6.0). However, several specific SystemC features are not supported yet or left undecided at this stage. The status "undecided" in particular indicates that further study is needed to decide whether or not the given construct can be supported in efficient and reasonable manner by RISC and its OoO PDES approach.

#### 4.1 SystemC Hierarchical Structure of Modules and Channels

RISC supports the regular hierarchical and structural composition of the SystemC design model. This includes the SystemC program start (sc\_main, sc\_start) and the general static or dynamic composition (SC\_CTOR) of modules (sc\_module, SC\_MODULE, sc\_behavior) and channels (sc\_channel, sc\_prim\_channel).

Connectivity and communication of the instantiated components is supported directly or hierarchically through ports (sc\_port, sc\_in, sc\_inout, sc\_out) and interfaces (sc\_interface). Also, modern TLM-2.0 style communication is supported (as of RISC version 0.6.0) directly or hierarchically through sockets (tlm\_utils::simple\_initiator\_socket, tlm\_utils::simple\_target\_socket, tlm::tlm\_initiator\_socket, and tlm::tlm\_target\_socket), with or without interconnect components.

In contrast to the traditional Accellera library, which only provides a type alias (typedef) sc\_channel for sc\_module, the RISC header files explicitly distinguish channel and module classes. Here, a separate sc\_channel class is inherited from sc\_module, providing the same functionality, but making the two class types explicit.

Most of the SystemC predefined primitive channels<sup>3</sup> (such as sc\_fifo) are supported for OoO PDES, except sc\_fifo::operator= which is not supported yet. For more details, please refer to Tables 1 through 8 and the Doxygen-generated documentation of the RISC simulation library [38].

#### 4.2 SystemC Threads

The explicit and statically or dynamically [35] analyzable multi-threading of a SystemC design model is naturally supported in RISC OoO PDES. This includes SystemC processes (SC\_HAS\_PROCESS, sc\_process\_handle, sc\_thread\_process) and the corresponding threads (SC\_THREAD). For basic inter-thread synchronization, SystemC event notifications (sc\_event.notify) and waiting for events or simulation time advance (wait) are supported.

However, dynamic SystemC thread creation and deletion (sc\_spawn, SC\_FORK, SC\_JOIN) are not supported at this time.

While the application programming interface (API) for these constructs remains unmodified from the SystemC user perspective, the RISC SystemC kernel internally supports extra parameters or arguments for several of these constructs which are utilized after the automatic source code instrumentation by the RISC compiler (see Section 3.4 above). In particular, segment and instance identifiers are supplied with each of these function calls so that the simulator kernel is aware of the exact thread state upon every scheduler entry. This includes in particular

<sup>&</sup>lt;sup>3</sup> As described in Section 2.4 and Section 3.9, the RISC Compiler and Simulator Release V0.6.0 falls back to synchronous PDES execution when primitive channels with update requests are used in the design model.

| Name                     | Туре              | Supported or not             | Notes                                            |

|--------------------------|-------------------|------------------------------|--------------------------------------------------|

| sc_abs                   | function          | Undecided                    | This function may not work with                  |

| sc_a05                   |                   | Undecided                    | some arithmetic SystemC datatypes.               |

| sc_actions               | typedef           | Supported                    | typedef unsigned sc_actions                      |

| sc_argc                  | function          | Supported                    |                                                  |

| sc_argv                  | function          | Supported                    |                                                  |

| sc_assemble_vector       | function          | Undecided                    | Work on this function in the future              |

| sc_assert                | macro             | Undecided                    | Work on this macro in the future                 |

| sc_attr_base             | class             | Undecided                    | Work on this class in the future                 |

| sc_attr_cltn             | class             | Undecided                    | Work on this class in the future                 |

| sc_attribute             | class             | Undecided                    | Work on this class in the future                 |

| sc_behavior              | typedef           | Supported                    | typedef sc_module sc_behavior                    |

| sc_bigint                | class template    | Supported                    |                                                  |

| sc_biguint               | class template    | Supported                    |                                                  |

| sc_bind_proxy            | class             | Undecided                    |                                                  |

| sc_bind                  | macro             | Undecided                    | Work on this macro in the future                 |

| sc_bit                   | type (deprecated) | Undecided                    | Work on this type in the future                  |

| sc_bitref_r              | class template    | Undecided                    | Work on this class template in the future        |

| sc_bitref                | class template    | Undecided                    | Work on this class template in the future        |

| sc_buffer                | class             | Undecided                    |                                                  |

| sc_bv_base               | class             | Undecided                    | Work on this class in the future                 |

| sc_bv                    | class template    | Undecided                    | Work on this class template in the future        |

| sc_channel               | class             | Supported                    |                                                  |

| sc_clock                 | class             | Not Supported Yet            | <pre>sc_clock::before_end_of_elaboration()</pre> |

| sc_close_vcd_trace_file  | function          | Initial support as of v0.5.0 |                                                  |

| sc_concatref             | class             | Undecided                    | Work on this class in the future                 |

| sc_concref_r             | class template    | Undecided                    | Work on this class template in the future        |

| sc_context_begin         | enumeration       | Undecided                    |                                                  |

| sc_copyright             | function          | Supported                    |                                                  |

| sc_cor                   | class             | Supported                    |                                                  |

| sc_cor_pkg               | class             | Supported                    |                                                  |

| sc_cor_pthread           | class             | Supported                    |                                                  |

| sc_cor_pkg_pthread       | class             | Supported                    |                                                  |

| sc_create_vcd_trace_file | function          | Initial support as of v0.5.0 |                                                  |

| sc_cref                  | macro             | Undecided                    | Work on this macro in the future                 |

| sc_cthread_process       | class             | Limited Support              | Supported up to Internal Representation          |

| SC_CTHREAD               | macro             | Limited Support              | Supported up to Internal Representation          |

| SC_CTOR                  | macro             | Supported                    |                                                  |

## Table 1: RISC V0.6.0 Out-of-Order Parallel Simulatable SystemC Subset

| Name                          | Туре           | Supported or not   | Notes                                               |

|-------------------------------|----------------|--------------------|-----------------------------------------------------|

|                               |                |                    | <pre>sc_cycle() calls sc_simcontext::cycle(),</pre> |

|                               | function       |                    | which is not supported in                           |

| sc_cycle                      | (deprecated)   | Not Supported Yet  | the out-of-order simulation                         |

|                               |                |                    | in the current release.                             |

| an delte acunt                | function       | Modified semantics | This function returns the local                     |

| sc_delta_count                | Tunction       | Modified semantics | delta count of the running process.                 |

| sc_elab_and_sim               | function       | Supported          |                                                     |

| sc_end_of_simulation_invoked  | function       | Undecided          | Work on this function in the future                 |

| sc_event_and_expr             | class          | Supported          | Initial support as of v0.5.0                        |

| sc_event_and_list             | class          | Supported          | Initial support as of v0.5.0                        |

| for the second for the second | .1             | TT. J d. J         | Work on this class template                         |

| sc_event_finder_t             | class template | Undecided          | in the future                                       |

| sc_event_finder               | class          | Undecided          | Work on this class in the future                    |

| sc_event_or_expr              | class          | Supported          | Initial support as of v0.5.0                        |

| sc_event_or_list              | class          | Supported          | Initial support as of v0.5.0                        |

| sc_event_queue_if             | class          | Not Supported Yet  |                                                     |

|                               |                |                    | The constructor function is not                     |

| sc_event_queue                | class          | Not Supported Yet  | supported by the out-of-order                       |

| *                             |                |                    | simulation in the current release.                  |

|                               | class          | Limited Support    | The immediate notification is not                   |

| sc_event                      |                |                    | supported by the out-of-order                       |

|                               |                |                    | simulation in the current release.                  |

| sc_exception                  | typedef        | Undecided          | Work on this typedef in the future                  |

| sc_export_base                | class          | Not Supported Yet  | No port following in compiler analysis              |

| sc_export                     | class          | Not Supported Yet  | No port following in compiler analysis              |

| sc_fifo_blocking_in_if        | class          | Supported          |                                                     |

| sc_fifo_in_if                 | class          | Supported          |                                                     |

| sc_fifo_in                    | class          | Supported          |                                                     |

| sc_fifo_nonblocking_in_if     | class          | Supported          |                                                     |

| sc_fifo_out_if                | class          | Supported          |                                                     |

| sc_fifo_out                   | class          | Supported          |                                                     |

|                               | .1             | Lincited Comment   | <pre>sc_fifo::operator= is not supported;</pre>     |

| sc_fifo                       | class          | Limited Support    | execution falls back to synchronous PDES            |

| sc_find_event                 | function       | Undecided          | Work on this function in the future                 |

| sc_find_object                | function       | Undecided          | Work on this function in the future                 |

| sc_fix_fast                   | class          | Undecided          | Work on this class in the future                    |

| sc_fix                        | class          | Undecided          |                                                     |

|                               |                |                    | Work on this class template                         |

| sc_fixed_fast                 | class template | Undecided          | in the future                                       |

| sc_fixed                      | class template | Undecided          |                                                     |

Table 2: RISC V0.6.0 Out-of-Order Parallel Simulatable SystemC Subset (continued)

| Name                                      | Туре                     | Supported or not | Notes                               |

|-------------------------------------------|--------------------------|------------------|-------------------------------------|

| SC_FORK                                   | macro                    | Undecided        | Work on this macro in the future    |

| sc_fxcast_context                         | class                    | Undecided        | Work on this class in the future    |

| sc_fxcast_switch                          | class                    | Undecided        | Work on this class in the future    |

| sc_fxnum_bitref                           | class                    | Undecided        | Work on this class in the future    |

| sc_fxnum_fast_bitref                      | class                    | Undecided        | Work on this class in the future    |

| sc_fxnum_fast_subref                      | class                    | Undecided        | Work on this class in the future    |

| sc_fxnum_fast                             | class                    | Undecided        | Work on this class in the future    |

| sc_fxnum_subref                           | class                    | Undecided        | Work on this class in the future    |

| sc_fxnum                                  | class                    | Undecided        |                                     |

| sc_fxtype_context                         | class                    | Undecided        | Work on this class in the future    |

| sc_fxtype_params                          | class                    | Undecided        | Work on this class in the future    |

| sc_fxval_fast                             | class                    | Undecided        | Work on this class in the future    |

| sc_fxval                                  | class                    | Undecided        | Work on this class in the future    |

| sc_gen_unique_name                        | function                 | Undecided        | Work on this function in the future |

| sc_generic_base                           | class                    | Undecided        | Work on this class in the future    |

| sc_get_curr_process_handle                | function<br>(deprecated) | Supported        |                                     |

| sc_get_current_process_handle             | function                 | Supported        |                                     |

| sc_get_default_time_unit                  | function<br>(deprecated) | Supported        |                                     |

| sc_get_status                             | function                 | Supported        |                                     |

| sc_get_stop_mode                          | function                 | Supported        |                                     |

| sc_get_time_resolution                    | function                 | Supported        |                                     |

| sc_get_top_level_events                   | function                 | Undecided        | Work on this function in the future |

| sc_get_top_level_objects                  | function                 | Undecided        | Work on this function in the future |

| SC_HAS_PROCESS                            | macro                    | Supported        |                                     |

| sc_hierarchical_name_exists               | function                 | Undecided        | Work on this function in the future |

| sc_in_clk                                 | typedef                  | Undecided        |                                     |

| sc_in_resolved                            | class                    | Undecided        |                                     |

| sc_in_rv                                  | class                    | Undecided        |                                     |

| sc_in                                     | class                    | Supported        |                                     |

| sc_in <bool></bool>                       | class                    | Supported        |                                     |

| sc_in <sc_dt::sc_logic></sc_dt::sc_logic> | class                    | Supported        |                                     |

# Table 3: RISC V0.6.0 Out-of-Order Parallel Simulatable SystemC Subset (continued)

| Name              | Туре                     | Supported or not  | Notes                                                                                  |

|-------------------|--------------------------|-------------------|----------------------------------------------------------------------------------------|

| sc_initialize     | function<br>(deprecated) | Supported         |                                                                                        |

| sc_inout_clk      | type (deprecated)        | Undecided         |                                                                                        |

| sc_inout_resolved | class                    | Undecided         |                                                                                        |

| sc_inout_rv       | class                    | Undecided         |                                                                                        |

| sc_inout          | class                    | Supported         |                                                                                        |

| sc_int_base       | class                    | Supported         |                                                                                        |

| sc_int_bitref_r   | class                    | Undecided         | Work on this class in the future                                                       |

| sc_int_bitref     | class                    | Undecided         | Work on this class in the future                                                       |

| sc_int            | class template           | Supported         |                                                                                        |

| sc_interface      | class                    | Supported         |                                                                                        |

| sc_interrupt_here | function                 | Undecided         | Work on this function in the future                                                    |

| sc_is_prerelease  | function                 | Undecided         | Work on this function in the future                                                    |

| SC_IS_PRERELEASE  | macro                    | Supported         |                                                                                        |

| sc_is_running     | function                 | Supported         |                                                                                        |

| sc_is_unwinding   | function                 | Supported         |                                                                                        |

| SC_JOIN           | macro                    | Undecided         | Work on this macro in the future                                                       |

| sc_length_context | class                    | Undecided         | Work on this class in the future                                                       |

| sc_length_param   | class                    | Undecided         | Work on this class in the future                                                       |

| sc_logic          | class                    | Undecided         | Work on this class in the future                                                       |

| sc_lv_base        | class                    | Undecided         | Work on this class in the future                                                       |

| sc_lv             | class template           | Undecided         | Work on this class template in the future                                              |

| sc_main           | function                 | Supported         |                                                                                        |

| sc_max_time       | function                 | Limited Support   | Time is currently represented<br>as a signed integer of 64 bits<br>(not sc_dt::uint64) |

| sc_max            | function                 | Supported         |                                                                                        |

| sc_method_process | class                    | Limited Support   | Initial basic support as of v0.6.0                                                     |

| SC_METHOD         | macro                    | Limited Support   | Initial basic support as of v0.6.0                                                     |

| sc_min            | function                 | Supported         |                                                                                        |